### Gowin DDR3 Memory Interface IP **User Guide**

IPUG281-2.4E, 03/14/2025

#### Copyright © 2025 Guangdong Gowin Semiconductor Corporation. All Rights Reserved.

**GOWIN** is a trademark of Guangdong Gowin Semiconductor Corporation and is registered in China, the U.S. Patent and Trademark Office, and other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders. No part of this document may be reproduced or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of GOWINSEMI.

#### Disclaimer

GOWINSEMI assumes no liability and provides no warranty (either expressed or implied) and is not responsible for any damage incurred to your hardware, software, data, or property resulting from usage of the materials or intellectual property except as outlined in the GOWINSEMI Terms and Conditions of Sale. GOWINSEMI may make changes to this document at any time without prior notice. Anyone relying on this documentation should contact GOWINSEMI for the current documentation and errata.

#### **Revision History**

| Date       | Version | Description                                                                                                                                                                                                                                                                  |  |  |  |  |

|------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 08/24/2018 | 1.0E    | Initial version published.                                                                                                                                                                                                                                                   |  |  |  |  |

| 03/12/2019 | 1.1E    | Description of DDR3 1:4 clock ratio about continuous burst added.                                                                                                                                                                                                            |  |  |  |  |

| 07/12/2019 | 1.2E    | <ul><li>Address format modified.</li><li>Read and write efficiency description added.</li></ul>                                                                                                                                                                              |  |  |  |  |

| 01/06/2020 | 1.3E    | Static parameter options modified.                                                                                                                                                                                                                                           |  |  |  |  |

| 06/30/2021 | 1.4E    | <ul> <li>memory_clk and pll_lock ports added.</li> <li>Design source code file updated.</li> </ul>                                                                                                                                                                           |  |  |  |  |

| 11/25/2021 | 1.5E    | <ul> <li>The timing descriptions of cmd_en and cmd_ready modified.</li> <li>The timing descriptions of wr_data_en and wr_data_rdy modified.</li> </ul>                                                                                                                       |  |  |  |  |

| 08/12/2022 | 1.6E    | <ul> <li>The timing descriptions of user interface updated.</li> <li>The descriptions for continuous burst mode and non-continuous burst mode of the controllers added.</li> </ul>                                                                                           |  |  |  |  |

| 10/17/2022 | 1.7E    | wr_data_wren modified to wr_data_en, clk modified to clk_out, and wr_data_ready modified to wr_data_rdy in the timing diagrams.                                                                                                                                              |  |  |  |  |

| 06/08/2023 | 2.0E    | <ul> <li>The description of GW5AST-138 device added.</li> <li>pll_stop signal added.</li> <li>Chapter 8 Reference Design and Chapter 9 File Delivery removed.</li> </ul>                                                                                                     |  |  |  |  |

| 08/18/2023 | 2.1E    | <ul> <li>GW5A-25 devices added.</li> <li>Burst_Number_Enable option removed.</li> <li>The descriptions of app_burst_number interface signals removed.</li> </ul>                                                                                                             |  |  |  |  |

| 09/12/2023 | 2.2E    | GW5A-25 devices support pll_stop.                                                                                                                                                                                                                                            |  |  |  |  |

| 12/31/2024 | 2.3E    | <ul> <li>The maximum rate supported by devices and related descriptions modified.</li> <li>The content related to pll_stop of the IP in GW5A(T)-60K environment added.</li> <li>Data_Mask port description updated.</li> <li>Descriptions of 5.1.2 Reset updated.</li> </ul> |  |  |  |  |

| 03/14/2025 | 2.4E    | <ul> <li>Descriptions of IP features updated.</li> <li>Descriptions of resource utilization updated.</li> </ul>                                                                                                                                                              |  |  |  |  |

### Contents

| Contentsi                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Figuresiii                                                                                                                                                 |

| List of Tablesiv                                                                                                                                                   |

| 1 About This Guide1                                                                                                                                                |

| 1.1 Purpose11.2 Related Documents11.3 Terminology and Abbreviations11.4 Support and Feedback2                                                                      |

| 2 Overview                                                                                                                                                         |

| 3 Features and Performance4                                                                                                                                        |

| 3.1 Features43.2 Operating Frequency and Bandwidth Efficiency5                                                                                                     |

| 4 Functional Description6                                                                                                                                          |

| 4.1 Structure       6         4.2 Memory Controller       6         4.3 PHY       7         4.3.1 Initialization Unit       7         4.3.2 Data Path Unit       7 |

| 4.3.3 Control Path Unit       7         4.3.4 I/O Logical Unit       8         4.4 User Interface       8         4.4.1 Initialization Interface       8           |

| 4.4.2 Command and Address Interface84.4.3 The Location Relationship Between Command and Write Data94.4.4 Write Data Interface104.4.5 Read Data124.4.6 Refresh14    |

| 5 IP Usage Notes16                                                                                                                                                 |

| 5.1 Clock and Reset                                                                                                                                                |

| 5.2 pll_stop              | 17 |

|---------------------------|----|

| 6 Port List               | 19 |

| 7 Parameter Configuration |    |

| 8 Interface Configuration | 24 |

### **List of Figures**

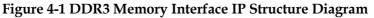

| Figure 4-1 DDR3 Memory Interface IP Structure Diagram                                   | . 6  |

|-----------------------------------------------------------------------------------------|------|

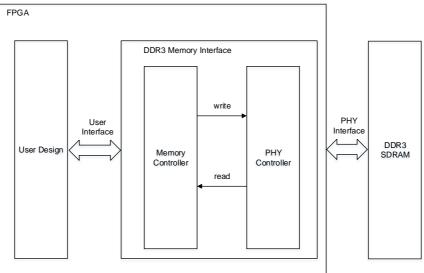

| Figure 4-2 DDR3 PHY Basic Structure Diagram                                             | . 7  |

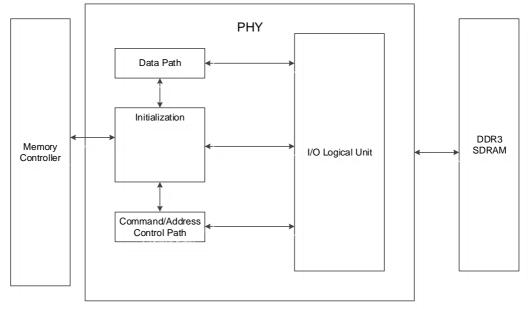

| Figure 4-3 Initialization Completion Signal Timing Diagram                              | . 8  |

| Figure 4-4 Addressing Scheme in Rank-Bank-Row-Column Order                              | . 9  |

| Figure 4-5 Command, Address, and Enable Signal Timing-A                                 | . 9  |

| Figure 4-6 The Location Relationship Between cmd and Data                               | . 10 |

| Figure 4-7 Write Data Timing with 1:2 Clock Ratio and Burst_Mode=BC4 or 1:4 Clock Ratio | . 11 |

| Figure 4-8 Write Data Timing with 1:2 Clock Ratio and Burst Mode=BL8                    | . 11 |

| Figure 4-9 Write Data Timing with 1:2 Clock Ratio and Burst Mode=OTF                    | . 12 |

| Figure 4-10 Read Data Timing with 1:2 Clock Ratio and Burst Mode=BC4                    | . 13 |

| Figure 4-11 Read Data Timing with 1:2 Clock Ratio and Burst Mode=BL8                    | . 13 |

| Figure 4-12 Read Data Timing with 1:2 Clock Ratio and Burst Mode= OTF                   | . 14 |

| Figure 4-13 Read Data Timing in Non-continuous Burst Mode with 1:4 Clock Ratio          | . 14 |

| Figure 4-14 User Refresh Timing                                                         | . 15 |

| Figure 5-1 Clock                                                                        | . 16 |

| Figure 5-2 Reset                                                                        | . 17 |

| Figure 5-3 138k pll_stop                                                                | . 17 |

| Figure 5-4 25K pll_stop                                                                 | . 18 |

| Figure 8-1 Open IP Core Generator                                                       | . 24 |

| Figure 8-2 Open DDR3 Memory Interface IP Core                                           | . 25 |

| Figure 8-3 IP Core Interface                                                            | . 25 |

| Figure 8-4 Basic Information Configuration Interface                                    | . 26 |

| Figure 8-5 Type Tab                                                                     | . 27 |

| Figure 8-6 Options Tab                                                                  | . 27 |

| Figure 8-7 Timing Tab                                                                   | . 28 |

| Figure 8-8 Debug Setting Options                                                        | . 28 |

### List of Tables

| Table 1-1 Terminology and Abbreviations                           | 1  |

|-------------------------------------------------------------------|----|

| Table 2-1 Gowin DDR3 Memory Interface IP                          | 3  |

| Table 3-1 Resource Utilization                                    | 5  |

| Table 4-1 Cmd                                                     | 8  |

| Table 6-1 IO Port List of Gowin DDR3 Memory Interface IP          | 19 |

| Table 7-1 Static Parameter Options of Gowin DDR3 Memory Interface | 22 |

| Table 7-2 DDR3 Time Parameter                                     | 23 |

### **1** About This Guide

#### 1.1 Purpose

The purpose of Gowin DDR3 Memory Interface IP User Guide is to help you quickly learn the features and usage of Gowin DDR3 Memory Interface IP by providing the descriptions of the functions, ports, timing, GUI, and reference design. The software screenshots in this manual are based on V 1.9.11. As the software is subject to change without notice, some information may not remain relevant and may need to be adjusted according to the software that is in use.

#### **1.2 Related Documents**

The latest user guides are available on the GOWINSEMI Website. You can find the related documents at <u>www.gowinsemi.com</u>:

- <u>DS102, GW2A series of FPGA Products Data Sheet</u>

- DS226, GW2AR series of FPGA Products Data Sheet

- DS1104, GW5AST series of FPGA Products Data Sheet

- DS1103, GW5A series of FPGA Products Data Sheet

- <u>SUG100, Gowin Software User Guide</u>

#### **1.3 Terminology and Abbreviations**

The terminology and abbreviations used in this manual are as shown in Table 1-1.

| Terminology and Abbreviations | Meaning                  |  |  |

|-------------------------------|--------------------------|--|--|

| ECC                           | Error Correcting Code    |  |  |

| FIFO                          | First Input First Output |  |  |

| GSR                           | Global System Reset      |  |  |

| IP                            | Intellectual Property    |  |  |

| LUT                           | Look-up Table            |  |  |

| RAM                           | Random Access Memory     |  |  |

**Table 1-1 Terminology and Abbreviations**

#### **1.4 Support and Feedback**

Gowin Semiconductor provides customers with comprehensive technical support. If you have any questions, comments, or suggestions, please feel free to contact us directly by the following ways.

Website: www.gowinsemi.com

E-mail: support@gowinsemi.com

## 2 Overview

Gowin DDR3 Memory Interface IP is a commonly used DDR3 memory interface IP that complies with the JESD79-3F standard protocol. The IP design includes DDR3 memory controller (MC) and the corresponding physical interface (PHY). Gowin DDR3 Memory Interface IP provides you with a general command interface which can connect with the memory chip to access and save data.

| Gowin DDR3 Memory Interface IP                          |                      |  |  |  |  |  |

|---------------------------------------------------------|----------------------|--|--|--|--|--|

| Logic Resource Please refer to Table 3-1.               |                      |  |  |  |  |  |

| Delivered Doc.                                          |                      |  |  |  |  |  |

| Design Files Verilog (encrypted)                        |                      |  |  |  |  |  |

| Reference Design Verilog                                |                      |  |  |  |  |  |

| TestBench Verilog                                       |                      |  |  |  |  |  |

| Test and Design Flow                                    | Test and Design Flow |  |  |  |  |  |

| Synthesis Software GowinSynthesis                       |                      |  |  |  |  |  |

| Application Software Gowin Software (V1.9.11 and above) |                      |  |  |  |  |  |

#### Table 2-1 Gowin DDR3 Memory Interface IP

#### Note!

For the devices supported, you can click here to get the information.

## **3** Features and Performance

#### **3.1 Features**

- Interfaces to the industrial standard DDR3 SDRAM devices and modules that are compatible with the JESD79-3F specification

- Supports memory data path width of 8 bits, 16 bits, 24 bits, 32 bits, 40 bits, 48 bits, 56 bits, 64 bits, and 72 bits

- Supports the single row RDIMM, UDIMM, and SODIMM memory modules

- Supports x8 and x16 data width memory chips

- Programs 4, 8, or OTF burst lengths

- Supports 1:2 and 1:4 clock ratio for GW2A-18, GW2A-55, and GW2AR-18, and supports 1:4 clock ratio for GW5AST-138

- Supports ECC

- Configurable CL

- Configurable AL

- Configurable CWL

- Configurable t<sub>FAW</sub>

- Configurable tRAS

- Configurable t<sub>RCD</sub>

- Configurable t<sub>RFC</sub>

- Configurable t<sub>RRD</sub>

- Configurable tRTP

- Configurable twrR

- Supports dynamic on-chip ODT

- Supports automatic refreshing and user startup refreshing and the interval of automatic refreshing is configurable

#### 3.2 Operating Frequency and Bandwidth Efficiency

The data rate of the DDR3 SDRAM that Gowin DDR3 Memory Interface supports is as follows:

- In 1:2 clock ratio mode, the maximum rate is 533 Mbps.

- In 1:4 clock ratio mode:

- For GW5A(R)(S)-25 devices, the maximum rate is 1100Mbps.

- For GW5A(T)-60 devices, the maximum rate is 1100Mbps.

- For other devices, the maximum rate is 800Mbps.

The bandwidth efficiency of Gowin DDR3 Memory Interface IP is as follows:

- In 1:2 clock ratio mode with a burst length of 4, the bandwidth efficiency is 50%.

- In 1:2 clock ratio mode with a burst length of 8, the bandwidth efficiency is 90%.

- In 1:4 clock ratio mode, the bandwidth efficiency is 90%.

Gowin DDR3 Memory Interface IP employs the Verilog language, and it is applied to GW2A and GW5A (excluding 15K) series chips. Due to differences in device density and speed, resource utilization may vary. Taking the GW5A-LV25UG324C2/I1 chip as an example, the resource utilization is as shown in Table 3-1.

#### **Table 3-1 Resource Utilization**

| Device   | Speed Grade | Name  | Resource Utilization |

|----------|-------------|-------|----------------------|

|          |             | LUT   | 2173                 |

| GW5A-25  | C2          | REG   | 3410                 |

| GVV5A-25 |             | ALU   | 125                  |

|          |             | BSRAM | 8                    |

#### Note!

In Table 3-1, Gowin DDR3 Memory Interface is configured with a user address width of 28 bits, DRAM width of x16 and the clock ratio of 1:4.

# **4** Functional Description

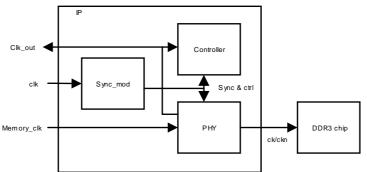

#### 4.1 Structure

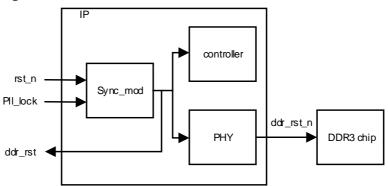

The structure of Gowin DDR3 Memory Interface IP is as shown in Figure 4-1. It includes Memory Controller and Physical Interface modules, etc. The User Design in the Figure 4-1 is the user design in the FPGA that needs to be connected to an external DDR3 SDRAM chip.

#### 4.2 Memory Controller

Memory Controller is located at MC layer, realizing protocol layer functions. Internal state machine is for BANK, ROW, COL, and refresh control. Memory Controller receives user-side read and write commands, stores the commands in FIFO logic internally, converts read and write commands into detectable interface timings on PHY side, and inputs to PHY side.

### 4.3 PHY

The PHY provides the physical definition and interface between MC and external DDR3 SDRAM, receives commands from the memory controller on MC layer, and provides the DDR3 SDRAM chip with interface timing.

The structure of PHY includes four modules: initialization module, data path, command address control path, and I/O logic module, as shown in Figure 4-2.

Figure 4-2 DDR3 PHY Basic Structure Diagram

#### 4.3.1 Initialization Unit

The initialization module is mainly used for initialization and read calibration after DDR3 SDRAM power-on. After initialization and read calibration are finished, the "init\_calib\_complete" signal will be high from low, indicating that the initialization has been completed.

#### Note!

Read/write operations are not allowed to be performed until the init\_calib\_complete signal is pulled up.

#### **Power-on Initialization**

According to the JESD79-3F protocol, there is a need to initialize the DDR3 SDRAM (chip or DIMM) after power-on. This includes the reset, clock enable, mode register configuration, and ZQ calibration.

#### 4.3.2 Data Path Unit

Data path includes write data path and read data path.

#### 4.3.3 Control Path Unit

The command/address control path is a single path that receives the command and address signal sent by the Memory Controller and cooperates with the data path to process the write and read data delay

parameters and sends the commands to the I/O logic module.

#### 4.3.4 I/O Logical Unit

The Logic I/O module is mainly used to convert the clock domain of the data, command, and address signals received from the data path and command/address path.

#### 4.4 User Interface

#### 4.4.1 Initialization Interface

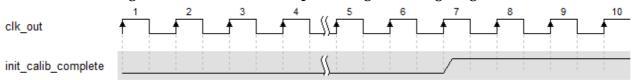

Init\_calib\_complete: The DDR3 SDRAM needs to be calibrated before write and read. Therefore, after power-on, PHY will initialize and calibrate the DDR3 SDRAM, and the init\_calib\_complete is pulled high after the initialization is completed, as shown in Figure 4-3.

#### 4.4.2 Command and Address Interface

#### Command

You can write commands to IP via cmd and cmd\_en, and the controller initiates read and write to the DDR3 chip according to the order of the write commands.

- Cmd is the command port;

- Cmd\_en is the enable signal of the command, active-high.

See Table 4-1 for the meanings of cmd:

#### Table 4-1 Cmd

| Command | cmd[2:0] |

|---------|----------|

| Read    | 3'b001   |

| Write   | 3'b000   |

#### Address

Addr is the user-side address bus which is written to the controller together with cmd. Addr is valid when cmd\_en is valid.

In the application, a mapping relationship exists between the address bus of user interfaces and Bank, Rank, Row, Column of the physical memory. In this design, the array is in Rank-Bank-Row-Column order, and the addressing scheme is as shown in Figure 4-4. You should note the order of the addresses provided in the application.

| User  | A<br>n    |           |          | A<br>5 | A /<br>4 3 | A A<br>3 2 | -   | A<br>0 |

|-------|-----------|-----------|----------|--------|------------|------------|-----|--------|

| SDRAM | Rank Addr | Bank Addr | Row Addr | Со     | lumr       | n Ac       | ddr |        |

#### Figure 4-4 Addressing Scheme in Rank-Bank-Row-Column Order

Addr is the DDR address, i.e. addr directly reflects the DDR memory address. When DDR3 burst\_mode is configured with BC4, one write/read needs to write/read 4 dq data to DDR, so one DDR write/read occupies 4 addresses. When DDR3 burst\_mode is configured with BL8, one write/read needs to write/read 8 dq data to DDR, so one DDR write/read occupies 8 addresses. You should note the control of the addresses provided in the application.

#### Address and Command Timing with 1:2 Clock Ratio

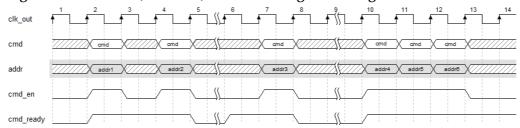

If clock ratio is 1:2 and cmd\_ready is high, it indicates that the DDR controller can receive user commands.

When cmd\_en and cmd\_ready is 1, write cmd and addr to IP. addr1 and addr2 have no relationship and do not have to be neighboring addresses.

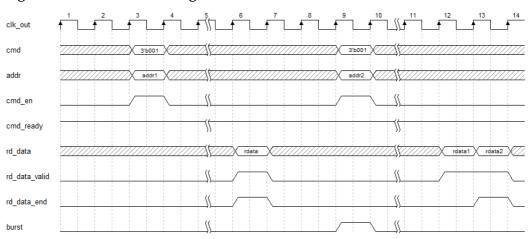

The timing of the command, address, and enable signals is as shown in Figure 4-5.

Figure 4-5 Command, Address, and Enable Signal Timing-A

#### Address and Command Timing with 1:4 Clock Ratio

The address and command timing is the same as that in 1:2 clock ratio. See the timing as shown in Figure 4-5.

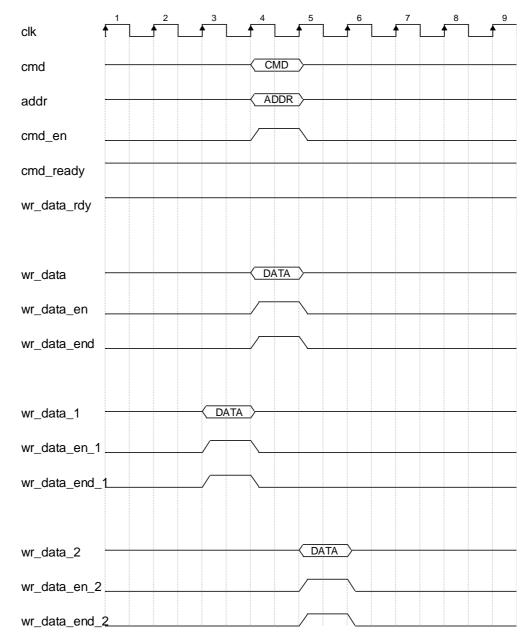

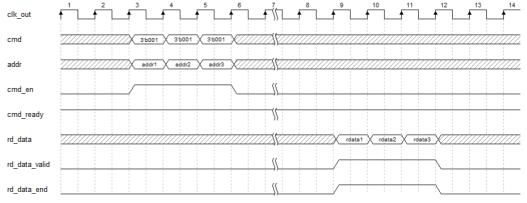

#### 4.4.3 The Location Relationship Between Command and Write Data

The location relationship between command and write data is as shown in Figure 4-6.

Figure 4-6 The Location Relationship Between cmd and Data

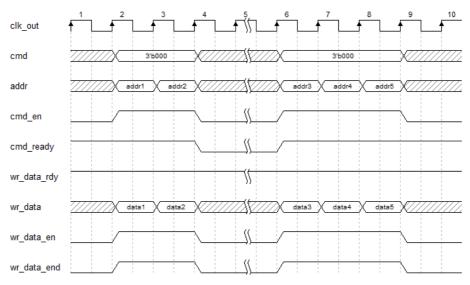

#### 4.4.4 Write Data Interface

- wr\_data: Data bus interface. You can write the data need to be stored in DDR through this interface.

- wr\_data\_en: Data write enable interface. wr\_data is active-high.

- wr\_data\_end: It indicates the data on wr\_data bus in current cycle is the last write data currently.

- wr\_data\_rdy: when wr\_data\_rdy is high, it indicates the controller can receive user data. You can write data in controller through wr\_data, wr\_data\_en, and wr\_data\_end interfaces.

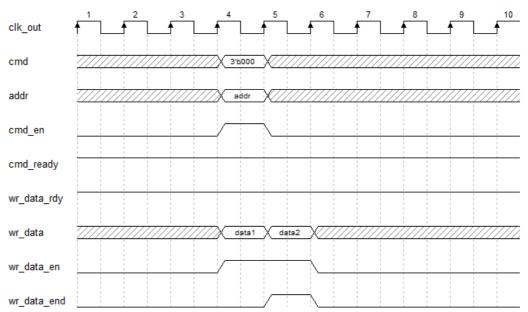

When the clock ratio is 1:2, the burst\_mode is configured with BC4, and the bit width ratio of wr\_data to dq data is 1:4. At this time, one wr\_data can meet one burst write for DDR. wr\_data\_en and wr\_data\_end

have the same action, so you can write 1 to wr\_data\_en and wr\_data\_end at the same time when writing data.

When the clock ratio is 1:4 and the burst\_mode is configured with BL8, the situation is the same as the above example. See Figure 4-7 for the timing.

Figure 4-7 Write Data Timing with 1:2 Clock Ratio and Burst\_Mode=BC4 or 1:4 Clock Ratio

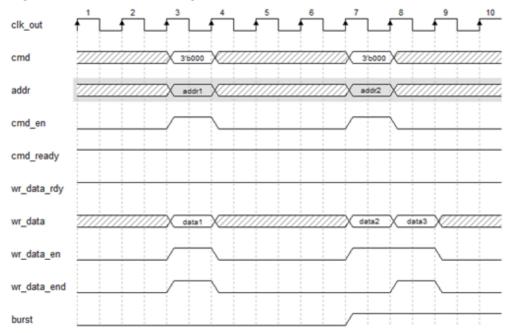

When the clock ratio is 1:2 and burst\_mode is configured with BL8, the bit-width ratio of wr\_data to dq data is 1:4. At this time, DDR needs two wr\_data for one burst write. Then wr\_data\_en should last for two consecutive cycles, and the second cycle will write wr\_data\_end to 1. See Figure 4-8 for the timing.

Figure 4-8 Write Data Timing with 1:2 Clock Ratio and Burst Mode=BL8

Only when the clock ratio is 1:2, burst\_mode is supported to be configured with OTF mode. In this mode, the port signal burst is 0 indicating the current DDR chip burst\_mode is BC4; the port signal burst is 1 indicates the current DDR chip burst\_mode is BL8. At this time, you should control the wr\_data \_en and wr\_data\_end signals according to the situation. See Figure 4-9 for the timing.

Figure 4-9 Write Data Timing with 1:2 Clock Ratio and Burst Mode=OTF

#### 4.4.5 Read Data

You can read the data from the DDR3 SDRAM using the user interfaces, including rd\_data, rd\_data\_valid, and rd\_data\_end.

- The rd\_data is the returned read data port.

- The rd\_data\_valid port is the valid read data port. When it is high, it indicates the returned rd\_data is valid at this time.

- The rd\_data\_end port indicates the last set of returned data in the current burst\_mode, active-high.

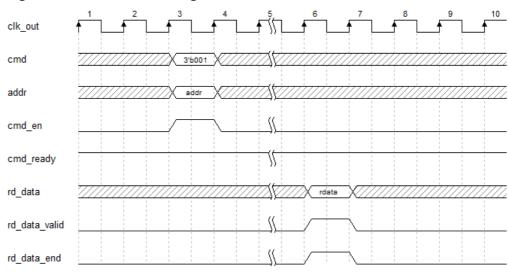

Similar to the write operation, when clock ratio is 1:2 and users configure the burst length with BC4, read data occupies one clk cycle, as shown in Figure 4-10.

Figure 4-10 Read Data Timing with 1:2 Clock Ratio and Burst Mode=BC4

Similar to the write operation, when clock ratio is 1:2 and users configure the burst length with BL8, read data occupies two clk cycles, as shown in Figure 4-11.

Figure 4-11 Read Data Timing with 1:2 Clock Ratio and Burst Mode=BL8

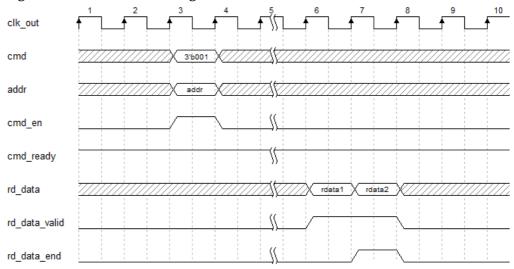

When clock ratio is 1:2 and users configure the burst mode with OTF (i.e., users can control the burst port to switch BC4 and BL8), when cmd\_en is valid, burst 0 indicates read BC4 and the read data occupies one clk cycle; burst 1 indicates read BL8 and the read data occupies two clk cycles, as shown in Figure 4-12.

Figure 4-12 Read Data Timing with 1:2 Clock Ratio and Burst Mode= OTF

When the clock ratio is 1:4, the read data is returned sequentially according to the read command order, as shown in Figure 4-13.

Figure 4-13 Read Data Timing in Non-continuous Burst Mode with 1:4 Clock Ratio

#### 4.4.6 Refresh

#### Refresh

The DDR3 SDRAM array needs to continually refresh to ensure the data is not lost. Therefore, Gowin DDR3 Memory Interface IP is required to send the refresh instruction to DDR3 SDRAM periodically. Gowin DDR3 Memory Interface IP requires ad interval of  $t_{REFI}$  time to generate refresh command; after the refresh command is generated, MC will precharge all banks after executing the last read/write command, and then execute Refresh command. The refresh operation has higher priority.

#### Self-Refresh

You can send a self-refresh request through the sr\_req port and configure DDR3 SDRAM with self-refresh mode. In the self-refresh mode, DDR3 SDRAM will automatically refresh the memory array without a refresh instruction from Gowin DDR3 Memory Interface IP.

Gowin DDR3 Memory Interface IP will return the sr\_ack signal to users after the self-refresh configuration of DDR3 SDRAM is completed, indicating that the DDR3 SDRAM is configured with self-refresh mode.

#### **User Refresh**

You can use this option to configure the refresh mode with user refresh mode. "USER\_REFRESH" needs to be configured with "ON." You can send a refresh request to MC through ref\_req port at any time without additional commands to MC through cmd port. When user refresh instruction is sent, ref\_req need to hold at high level for one cycle. After the refresh instruction is sent, MC will feedback ref\_ack signal which will hold at high level for one cycle, as shown in Figure 4-14.

#### **Figure 4-14 User Refresh Timing**

| clk_out |          | 89   |      |  |

|---------|----------|------|------|--|

| ref_req |          | <br> | <br> |  |

| ref_ack | <u> </u> |      |      |  |

The user refresh operation may affect the instructions that MC has received or is executing. Before user refresh operation, MC completes the command operation being executed first. You should consider the coordination between the user refresh and other instructions to avoid  $t_{\text{REFI}}$  violation.

Considering the worst case, you can operate user refresh with reference to the following formula. Command a certain time to complete the transmission, which can be roughly calculated by parameters such as  $t_{RCD}$ , CL, data transmission time,  $t_{RP}$ , etc. And the user refresh should be completed before the time parameter  $t_{REFI}$  is violated, so the maximum interval between two user refresh times can be calculated by following formula.

$$t_{REFI} - (t_{RCD} + (CL + 4) \times t_{CK} + t_{RP}) \times nBA$$

In application, if a user refresh starts, you need to start a user refresh immediately after the DDR3 SDRAM completes initialization to establish the time base for subsequent user refresh requests.

# **5** IP Usage Notes

#### 5.1 Clock and Reset

#### 5.1.1 Clock

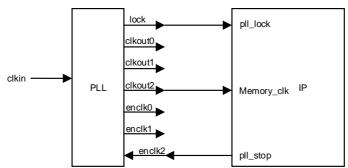

The IP has three clocks, two input clocks, clk and memory\_clk, and one output clock, clk\_out.

As shown in Figure 5-1, clk is used to generate some synchronization and control signals which act on the main body of the IP logic (PHY layer and Memory controller). clk is required to be a low-speed continuous clock with a recommended value of 50MHz, and the input of the on-board crystal can be connected to clk.

memory\_clk is the high speed clock, which uses HCLK resources to drive the PHY and is output to the DDR3 chip.

clk\_out is the frequency-divided clock of memory\_clk. When clk\_ratio is set to 4:1, clk\_out is the four-divided clock of memory\_clk; when clk\_ratio=2:1, clk\_out is the two-divided clock of memory\_clk, and it uses PCLK resources. clk\_out is used as the logic processing clock for IP and is output to user logic. The user's interface operation on the IP should be synchronized with clk\_out.

Figure 5-1 Clock

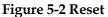

#### 5.1.2 Reset

The IP includes the input signals rst\_n and pll\_lock, as well as the output signal ddr\_rst. As shown in Figure 5-2, n is required to do a synchronization release under the clk before sending it to the IP. rst\_n will

reset the Sync\_mod module logic, and then Sync\_mod waits for pll\_lock. After pll\_lock is locked, Sync\_mod will output ddr\_rst as the global reset of the IP and send it to the user. Any reset logic can be connected to rst\_n, and pll\_lock can only be connected to the LOCK signal of the PLL. If pll\_lock is not connected to the LOCK signal of the PLL, the IP will not be able to detect whether the clock is stable, and DDR initialization failure is prone to occur.

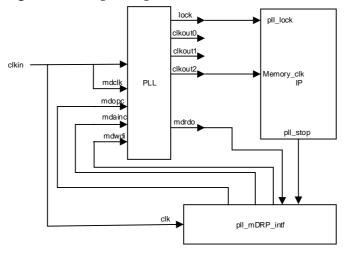

#### 5.2 pll\_stop

pll\_stop is a control signal for GW5A(S)(T) devices; it is a switch to control memory\_clk, active-low.

As shown in Figure 5-3 and Figure 5-4, when 138K devices are used, pll\_stop is directly connected to enclk2 of PLL.

When 25K devices are used, pll\_stop needs to be connected to the adapter module, pll\_mDRP\_intf, to indirectly control the clkout2 of PLL. The clk of pll\_mDRP\_intf is the same as the mdclk and clkin of PLL.

For other GW5A series of devices, the usage of pll\_stop will not be explained in details. It is necessary to check whether the target FPGA's PLL has an enable control enclk similar to that of the 138K. If it does, pll\_stop can be directly connected. Otherwise, control must be implemented via the mDRP interface.

Figure 5-3 138k pll\_stop

#### Figure 5-4 25K pll\_stop

pll\_mDRP\_intf module is included in the <u>reference design</u> of Gowin\_DDR3\_Memory\_Interface\_RefDesign, please download it from official website.

## 6 Port List

The I/O ports of the Gowin DDR3 Memory Interface IP are as shown in Table 6-1.

| Signal         | Data Width         | I/O    | Description                                                                                              |  |  |  |

|----------------|--------------------|--------|----------------------------------------------------------------------------------------------------------|--|--|--|

| User Interface |                    |        |                                                                                                          |  |  |  |

| addr           | ADDR_WIDTH         | Input  | Address input, configure<br>parameter to set the signal<br>width                                         |  |  |  |

| cmd            | 3                  | Input  | Command channel                                                                                          |  |  |  |

| cmd_en         | 1                  | Input  | Command and address enable<br>signals<br>0: invalid<br>1: valid                                          |  |  |  |

| cmd_ready      | 1                  | Output | High indicates Memory<br>Interface can receive<br>commands and addresses.                                |  |  |  |

| rd_data        | APP_DATA_WID<br>TH | Output | Read data channel                                                                                        |  |  |  |

| rd_data_end    | 1                  | Output | High indicates the end cycle of the current rd_data.                                                     |  |  |  |

| rd_data_valid  | 1                  | Output | rd_data valid signal:<br>0: invalid<br>1: valid                                                          |  |  |  |

| burst          | 1                  | Input  | OTF control port, BL8 mode<br>when 1'b1; BC4 mode when<br>1'b0, valid only in OTF mode                   |  |  |  |

| wr_data        | APP_DATA_WID<br>TH | Input  | Write data channel                                                                                       |  |  |  |

| wr_data_end    | 1                  | Input  | High level indicates that the current clock cycle is the last cycle of this wr_data.                     |  |  |  |

| wr_data_mask   | APP_MASK_WI<br>DTH | Input  | Each bit corresponds to one<br>byte of wr_data.<br>0: The corresponding wr_data<br>byte mask is invalid. |  |  |  |

Table 6-1 IO Port List of Gowin DDR3 Memory Interface IP

| Signal                  | Data Width            | I/O    | Description                                                                                                                                                                                                                 |

|-------------------------|-----------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                       |        | 1: The corresponding wr_data byte mask is valid.                                                                                                                                                                            |

| wr_data_rdy             | 1                     | Output | High indicates MC can receive the user data.                                                                                                                                                                                |

| wr_data_en              | 1                     | Input  | wr_data write enable signal:<br>0: Disable<br>1: Enable                                                                                                                                                                     |

| sr_req                  | 1                     | Input  | Self-refresh request                                                                                                                                                                                                        |

| sr_ack                  | 1                     | Output | Refresh the acknowledgement signal                                                                                                                                                                                          |

| ref_req                 | 1                     | Input  | User refresh request                                                                                                                                                                                                        |

| ref_ack                 | 1                     | Output | User refresh the<br>acknowledgement signal                                                                                                                                                                                  |

| clk                     | 1                     | Input  | Reference input clock,<br>generally PCB crystal input,<br>50M recommended.                                                                                                                                                  |

| memory_clk              | 1                     | Input  | Memory interface frequency<br>input by user; when GW2A<br>devices used, this clock can be<br>either the output clock of PLL<br>or other clock; when GW5A<br>devices used, this clock must<br>be output from clkout2 of PLL. |

| pll_stop 1              |                       | output | For the details, you can see <u>5.2 pll_stop</u>                                                                                                                                                                            |

| pll_lock                | 1                     | Input  | If memory_clk is PLL<br>multiplication input, this<br>interface is connected to the<br>pll_lock of PLL, if you do not<br>use PLL, this interface is<br>connected to high level.                                             |

| rst_n                   | 1                     | Input  | System reset input signal<br>0: Enable<br>1: Disable                                                                                                                                                                        |

| init_calib_comp<br>lete | 1                     | Output | Initialization completed signal                                                                                                                                                                                             |

| clk_out                 | 1                     | Output | User design clock                                                                                                                                                                                                           |

| ecc_err                 | APP_DATA_WID<br>TH/32 | Output | ECC indicates signal output                                                                                                                                                                                                 |

| ddr_rst                 | 1                     | Output | The reset signal that IP<br>processed is used for user<br>design, high reset.                                                                                                                                               |

| DDR3 SDRAM Ir           | nterface              |        |                                                                                                                                                                                                                             |

| O_ddr_addr              | ROW_WIDTH             | Output | Row address (activation<br>command), Column address<br>(read/write command)                                                                                                                                                 |

| O_ddr_bank              | BANK_WIDTH            | Output | Bank address                                                                                                                                                                                                                |

| Signal        | Data Width | I/O         | Description                                      |

|---------------|------------|-------------|--------------------------------------------------|

| O_ddr_cs_n    | CS_WIDTH   | Output      | Chip selected, active-low.                       |

| O_ddr_ras_n 1 |            | Output      | Row address selection signal                     |

| O_ddr_cas_n   | 1          | Output      | Column address selection signal                  |

| O_ddr_we_n    | 1          | Output      | Row write enable                                 |

| O_ddr_ck      | CK_WIDTH   | Output      | A clock signal provided to<br>DDR3 SDRAM         |

| O_ddr_ck_n    | CK_WIDTH   | Output      | Compose a differential signal<br>with ddr_ck     |

| O_ddr_cke     | CKE_WIDTH  | Output      | DDR3 SDRAM clock enable signal                   |

| O_ddr_odt     | ODT_WIDTH  | Output      | Terminating resistor control of<br>memory signal |

| O_ddr_reset_n | 1          | Output      | DDR3 SDRAM reset signal                          |

| O_ddr_dm      | DM_WIDTH   | Output      | DDR3 SDRAM data masking signal                   |

| IO_ddr_dq     | DQ_WIDTH   | Bidirection | DDR3 SDRAM data                                  |

| IO_ddr_dq     | DQS_WIDTH  | Bidirection | DDR3 SDRAM data strobe signal                    |

| IO_ddr_dqs_n  | DQS_WIDTH  | Bidirection | Compose a differential signal with ddr_dqs       |

## **7** Parameter Configuration

Gowin DDR3 Memory Interface IP supports DDR3 SDRAM devices. You need to configure various of static parameters and timing parameters of Gowin DDR3 Memory Interface according to the design requirements, as shown in Table 7-1 and Table 7-2.

| Name             | Description                                                                        | Options                                                                                                          |  |  |  |  |

|------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Memory Type      | Memory type                                                                        | MT41J128M16JT-125k<br>Custom                                                                                     |  |  |  |  |

| Memory Clock     | Chip Interface Clock<br>Frequency                                                  | Write according to the chip operating clock and demand                                                           |  |  |  |  |

| CLK Ratio        | Ratio of user interface<br>clock frequency to chip<br>interface clock<br>frequency | 1:4, 1:2                                                                                                         |  |  |  |  |

| DIMM Type        | Chip DIMM Type                                                                     | Components, RDIMMs, UDIMMs, SODIMMs                                                                              |  |  |  |  |

| Dq Width         | Dq Data Bit Width                                                                  | 8, 16, 24, 32, 40, 48, 56, 64, 72                                                                                |  |  |  |  |

| Dram Width       | Data bit width of single chip                                                      | 4, 8, 16                                                                                                         |  |  |  |  |

| Rand Address     | Rand Address                                                                       | Select 1 for single and dual rank devices                                                                        |  |  |  |  |

| Bank Address     | Memory BANK<br>address width                                                       | Select according to DDR3 SDRAM chip                                                                              |  |  |  |  |

| Row Address      | Memory line address width                                                          | Select according to DDR3 SDRAM chip                                                                              |  |  |  |  |

| Column Address   | Memory column<br>address width                                                     | Select according to DDR3 SDRAM chip                                                                              |  |  |  |  |

| Burst Mode       | Chip Burst Mode                                                                    | "4", "8", "OTF"; 4 or OTF is<br>supported when clock ratio is 1:2; 8<br>is supported when clock ratio is<br>1:4. |  |  |  |  |

| Burst Type       | Chip Burst Type                                                                    | "Sequential" "Interleaved"                                                                                       |  |  |  |  |

| CAS latency      | CAS delay time                                                                     | 5, 6, 7, 8                                                                                                       |  |  |  |  |

| Additive latency | Additive delay time                                                                | 0, CL-1, CL-2                                                                                                    |  |  |  |  |

Table 7-1 Static Parameter Options of Gowin DDR3 Memory Interface

| Name         | Description                                                                                                                          | Options                                                                  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| CW Latency   | CWL delay time                                                                                                                       | Choose according to the actual situation.                                |

| RTT NOM      | Nominal ODT value                                                                                                                    | "OFF": OFF<br>"20": 20<br>"30": 30<br>"40": 40<br>"60": 60<br>"120": 120 |

| RTT WR       | The Dynamic ODT<br>value in Multiple-RANK<br>used for the write<br>interface. For Single-<br>Component design,<br>RTT_WR is invalid. | "OFF": RTT_WR disabled<br>"120": RZQ/2<br>"60": RZQ/4                    |

| USER_REFRESH | Whether to control the refresh operation by the user                                                                                 | "ON", "OFF"                                                              |

#### Table 7-2 DDR3 Time Parameter

| Name              | Description                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>CK</sub>   | Memory interface clock period (ps)                                                                                                                                                |

| t <sub>CKE</sub>  | Minimum pulse time of CKE signal (ps)                                                                                                                                             |

| tFAW              | The interval between simultaneous activation commands of more than four lines in the same rank is allowed, so the minimum value should be no less than four times the $t_{RRD}$ . |

| t <sub>RAS</sub>  | Time from ACTIVE to PRECHARGE                                                                                                                                                     |

| t <sub>RCD</sub>  | Time from ACTIVE to READ/WRITE                                                                                                                                                    |

| t <sub>REFI</sub> | Memory refresh interval                                                                                                                                                           |

| t <sub>RFC</sub>  | The interval from REFRESH to ACTIVE/REFRESH                                                                                                                                       |

| t <sub>RP</sub>   | PRECHARGE cycle                                                                                                                                                                   |

| t <sub>RRD</sub>  | The interval from ACTIVE to ACTIVE                                                                                                                                                |

| t <sub>RTP</sub>  | The interval from READ to PRECHARGE                                                                                                                                               |

| t <sub>WTR</sub>  | The interval from WRITE to READ                                                                                                                                                   |

| AL                | Additive latency                                                                                                                                                                  |

| CL                | CAS latency                                                                                                                                                                       |

## **8** Interface Configuration

You can invoke and configure the Gowin DDR3 Memory Interface IP using the IP Core Generator tool in the IDE. This chapter takes AD3U160022G11 memory chip as an example, introduces the main configuration interface, configuration flow and the meaning of each configuration option (Take the clock ratio of 1:2 as an example).

1. Open IP Core Generator.

After creating the project, click the "Tools" tab in the upper left, click "IP Core Generator" to open Gowin IP Core Generator via the drop-down list, as shown in Figure 8-1.

#### Figure 8-1 Open IP Core Generator

| GOWIN FPGA Designer - (Design Summary)    |                 |                                                                                                       | - a × |

|-------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------|-------|

| File Edit Project Tools Window Help       |                 |                                                                                                       | _ @ × |

| 🕒 🗁 🔛 👘 💡 Start Page 🔰 🔀 👫                | :-: 🔢 🖂 🧠 🔡 🇢   |                                                                                                       |       |

| Process 🛛 Gowin Analyzer Oscilloscope 🖉 3 |                 |                                                                                                       |       |

| Design Summ 💱 Schematic Viewer 🔸          |                 | General                                                                                               |       |

|                                           | Project File:   | E:\memory\DDR3\Gowin_DDR3_Memory_Interface_RefDesign\DDR3_MC_PHY_1vs4_5a138k\project\ddr3_1v4_hs.gprj |       |

| Programmer                                | Synthesis Tool: | GowinSynthesis                                                                                        |       |

| FloorPlanner                              |                 |                                                                                                       |       |

| V Timing Co Timing Constraints Editor     |                 | Target Device                                                                                         |       |

| DSim Cloud                                | Part Number:    | GW5AST-LV138FPG676AES                                                                                 |       |

| Synthesis K Cotions_                      | Series:         | GWSAST                                                                                                |       |

| V O Place & Route                         | Device:         | GW5AST-138                                                                                            |       |

|                                           | Device Version: | 8                                                                                                     |       |

| Place & Route Report                      | Package:        | FCPBGA676A                                                                                            |       |

| Timing Analysis Report                    | Speed Grade:    | ES                                                                                                    |       |

| Ports & Pins Report                       | Core Voltage:   | LV                                                                                                    |       |

| Rogram Device                             |                 |                                                                                                       |       |

|                                           |                 |                                                                                                       |       |

| Design Process Hierarchy                  | 💡 Start Page 🖂  | Design Summary 🖸 📝 top.w 🔲 🔥 IP Core Generator 🗔                                                      |       |

| Console                                   |                 |                                                                                                       | 8 ×   |

| 8                                         |                 |                                                                                                       |       |

| Console Message                           |                 |                                                                                                       |       |

|                                           |                 |                                                                                                       |       |

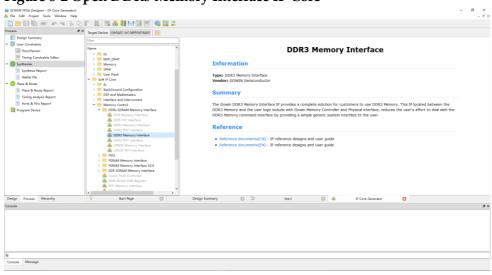

2. Open the DDR3 Memory Interface IP core.

Click DDR option, double-click DDR3 Memory Interface. The configuration interface of DDR3 Memory Interface IP core is as shown in Figure 8-2.

#### Figure 8-2 Open DDR3 Memory Interface IP Core

3. DDR3 Memory Interface IP Core Interface.

The port diagram of the DDR3 Memory Interface IP core is on the left, as shown in Figure 8-3.

The left is the ports of DDR3 Memory Controller and the user end. You can connect your design to the DDR3 Memory Interface IP to send/receive commands and data. The right is the interface of the PHY and DDR3 chip. You can save and access data by connecting the DDR3 Memory Interface IP and DDR3 chip. With different configuration information, the signal bit width and the signal number will change accordingly.

**Figure 8-3 IP Core Interface**

|                                                     |                               | General      |                          |                    |                   |

|-----------------------------------------------------|-------------------------------|--------------|--------------------------|--------------------|-------------------|

| • O_ddr_eddr(13.0)                                  | pl_stop                       | Device:      | GW5AST-138               | Device Version:    | В                 |

| O ddr ba(20)                                        | pl_ck                         | Part Number: | GW5AST-LV138FPG676AES    | Language:          | Verilog           |

|                                                     | cik 🖛                         | File Name:   | ddr3_memory_interface    | Module Name:       | /lemory_Interface |

| <ul> <li>O_ddr_cs_n</li> <li>O_ddr_nss_n</li> </ul> | wr_data_en                    | Create In:   | R3_MC_PHY_1vs4_5a138k\p  | oroject\src\ddr3_i | memory_interface  |

| O_ddr_cas_n                                         | wr_data_end +                 | Type Optic   | ons Timing Debug Se      | tting              |                   |

| O_ddr_we_n                                          | cmd_en                        | Select Mer   |                          |                    |                   |

| O_ddr_clk                                           | cmd[2.0]                      | Memory T     | -                        | •                  | CLK R             |

| • Ojddrjekje                                        | sr_ned -                      |              | Lock: 200MHz 🗘 (100 - 7  |                    |                   |

| O_ddr_cke                                           | bust                          | Memory C     | LOCK: 2001/HZ 🔽 (100 - 7 | 00) <-> 5000 ps    | DIMM T            |

| O_ddr_odt                                           | sr_ack                        | Data Bus     |                          |                    |                   |

| • Ojddrjessetje                                     | w_data_rdy                    | Dq Width:    | 16 • Dran                | n Width: 16        | ~                 |

| O_ddr_dqm(10)                                       | init_calib_complete           | Memory A     | ddress                   |                    |                   |

| IO_ddr_dq(150)                                      | rd_data_valid                 | Rank Addr    | ress: 1                  | Bank Address:      | 3                 |

| D_ddr_dqs[1:0]                                      | nd_data_and<br>nd_data[127.0] | Row Addre    | ess: 14 🔻                | Column Address:    | 10 -              |

| ➡ IO_ddr_dqs_n(10)                                  | dk_out 🔶                      |              |                          |                    |                   |

4. Configure General Information.

See the general information in the upper part of the configuration interface. The "Module Name" displays the top-level file name of the generated project, and the default is "ddr3\_memory\_interface\_top", and you can modify the name. The "File Name" displays the folder generated by the IP core, which contains the files required by DDR3 Memory Interface IP core, and the default is "DDR3 Memory\_Interface", and you can modify the path. "Create In" displays the path of IP core folder. The default is "\project path\src\DDR3\_Memory\_Interface", and you can modify the path, as shown in Figure 8-4.

Figure 8-4 Basic Information Configuration Interface

| 🗱 IP Customization |             |              |                                              |                 | ? ×                                        |

|--------------------|-------------|--------------|----------------------------------------------|-----------------|--------------------------------------------|

| DDR3 Memo          | ory Interfa | ce           |                                              |                 |                                            |

|                    |             | General      |                                              |                 |                                            |

|                    | pl_stop     | Device:      | GW5AST-138                                   | Device Version: | В                                          |

| O_ddr_addr(13:0)   | memory_ck   | Part Number: | GW5AST-LV138FPG676AES                        | Language:       | Verilog 🗸                                  |

|                    | plijbck 🖛   | File Name:   | ddr3_memory_interface                        | Module Name:    | DDR3_Memory_Interface_Top                  |

| ← 0_ddr_cs_n       | ck 🗲        | Create In:   | DR3\Gowin_DDR3_Memory_Interface_RefDesign\DI | DR3_MC_PHY_1vs  | 4_5a138k\project\src\ddr3_memory_interface |

#### 5. Type tab

In the Type tab, you need to configure the basic information for the DDR3 memory chip.

- Select Memory Option

- Data Bus Option

- Memory Address Option: In the Memory Address option, you can configure the Address information of the Rank, Bank, Row, and Column of the DDR3 Memory chips. After choosing the type of DDR3 Memory chip, GUI will automatically fill in these fields; if you choose the "Custom", you need to choose according to the DDR3 Memory type.

- Non-configurable items are grayed out.

| Customization                     |                              |              |                           |                   | ?                 |    |

|-----------------------------------|------------------------------|--------------|---------------------------|-------------------|-------------------|----|

| DR3 Mer                           | nory Inter                   | face         |                           |                   |                   | 5  |

|                                   |                              | General      |                           |                   |                   |    |

| O_ddr_addr(13.0)                  | pll_stop 🔶                   | Device:      | GW5AST-138                | Device Version:   | В                 |    |

|                                   | memory_dk ◀━━<br>pl_lock ◀━━ | Part Number: | GW5AST-LV138FPG676AES     | Language:         | Verilog           |    |

| O_ddr_ba(20)                      | dk 🖛                         | File Name:   | ddr3 memory interface     | ] <b>-</b> -      | /lemory Interface | То |

| <ul> <li>O_ddr_cs_n</li> </ul>    | nin 🔶                        |              |                           | 1                 |                   |    |

| - Ojddrjasja                      | wr_data_en wr data[127.0]    | Create In:   | R3_MC_PHY_1vs4_5a138k\p   | roject\src\ddr3_r | nemory_interface  |    |

| <ul> <li>O_ddr_cas_n</li> </ul>   | w_data_end -                 | Type Optic   | ons Timing Debug Set      | tina              |                   |    |

| <ul> <li>O_ddr_we_n</li> </ul>    | wr_data_mask(15.0)           |              | in in ing beauges         |                   |                   |    |

|                                   | ond_en                       | Select Mer   | mory                      |                   |                   | ŕ  |

| - O_ddr_dk                        | addr(27.0)                   | Memory T     | vpe: MT41J128M16JT-12     | •                 | CLK R             | at |

| - O_ddr_dk_n                      | s_req 🖛                      | -            |                           |                   |                   | -  |

| - O_ddr_dw                        | per_ben                      | Memory C     | CLock: 200MHz 🛨 (100 - 70 | 00) <-> 5000 ps   | DIMM T            | УI |

| -                                 | bust 🚛                       |              |                           |                   |                   |    |

| O_ddr_odt                         | sr_ack                       | Data Bus     |                           |                   |                   |    |

| - O_ddr_resist_n                  | w_data_rdy                   | Dq Width:    | 16 🔻 Dram                 | Width: 16         | -                 |    |

| <ul> <li>O_ddr_dqm(10)</li> </ul> | ini_calb_complete            |              |                           |                   |                   |    |

| o un udm(m)                       | cmd_ready                    | Memory A     | ddress                    |                   |                   |    |

| ↔ 10_ddr_dq(150)                  | nd_data_valid 🔶              | Rank Addr    | ress: 1 📫 I               | Bank Address:     | 3                 |    |

| ↔ 10_ddr_dqs(1.0)                 | rd_data_end                  |              |                           |                   |                   |    |

| and the state of the state        | rd_data (127.0)              | Row Addre    | ess: 14 🔻 (               | Column Address:   | 10 🔻              |    |

| + IO_ddr_dqs_n(10)                | ck_out →<br>ddr.st           |              |                           |                   |                   |    |

|                                   | •                            | <            |                           |                   |                   | >  |

|                                   | ۹. ۱                         | ۹.           |                           |                   |                   |    |

**.**... **TE** 1

- 6. Options tab is as shown in Figure 8-6, and take "MT41J128M16JT-125K" memory chip as an example.

- **Memory Options** -

- Generation Config Option; if it is checked, IBUF, OBUF, and the other primitives are not inserted in the generated IP, you can directly use ports to connect to the logic, and it is checked by default.

Figure 8-6 Options Tab

|                |                     | General      |          |          |          |                       |                 |                                           |

|----------------|---------------------|--------------|----------|----------|----------|-----------------------|-----------------|-------------------------------------------|

|                |                     | Device:      | GW5A     | ST-138   |          |                       | Device Version: | В                                         |

| ddr_addi(13.0) | pl_stop             | Part Number: | GW5A     | ST-LV138 | PG676A   | is .                  | Language:       | Verilog                                   |

| ddr,baj2.0j    | plijbek 🖛           | File Name:   | ddr3_n   | nemory_i | nterface |                       | Module Name:    | DDR3_Memory_Interface_Top                 |

|                | ck 🖛                | Create In:   | DR3\Ge   | win DDR  | 3 Memo   | v Interface RefDesign | DDR3 MC PHY 1vs | 4_5a138k\project\src\ddr3_memory_interfac |

| ddr_cs_n       | rst_n               |              | <u> </u> | -        | -        |                       |                 |                                           |

| ddr_ms_n       | wr_data_on +        | Type Opti    | ons T    | iming    | Debug S  | Setting               |                 |                                           |

| ddr.cas.n      | w data end 🖛        | Memory       | Intione  |          |          |                       |                 |                                           |

|                | wr_data_mask(15:0)  |              |          |          |          |                       |                 |                                           |

| ddr_we_n       | cmd_en 🖛            | Burst Mod    | le:      | 8        | Y        | Burst Type:           | SEQ 🔻           |                                           |

| ddr.clk        | cmd(2:0)            | CAS Laten    | cy:      | 5        | -        | CW Latency:           | 5 👻             |                                           |

|                | addr(27:0)          | Additive L   | atency:  | 0        | v        | Write Recovery:       | 6 👻             |                                           |

| kdr_clk_n      | si'sd               | SLOT_0_CC    | DNFIG:   | 8'600000 | 001      | SLOT_1_CONFIG:        | 8'b00000000     |                                           |

| ddr_cke        | kef_keq             | Rtt Nom:     |          | 40       | •        | Rtt Wr:               | OFF -           |                                           |

| kdr_odt        | track               | Addr Cmd     | Mode:    | 1T       | •        | OUTPUT DRV:           | LOW -           |                                           |

|                | ref_ack -           | User R       |          |          |          |                       |                 |                                           |

| ldr_mset_n     | wr_data_idy 🔶       | U User Re    | erresn   |          |          |                       |                 |                                           |

| idr_dqm(1:0)   | init_callb_complete | Generation   | n Config |          |          |                       |                 |                                           |

|                | cmd_mady 🛶          |              |          |          |          |                       |                 |                                           |

| ddr_dq(15:0)   | rd_data_valid 🔸     | 🗹 Disable    | I/O Ins  | ertion   |          |                       |                 |                                           |

| ddr_dqs[10]    | nd_data_end         |              |          |          |          |                       |                 |                                           |

| and add out    | rd_data(127:0)      |              |          |          |          |                       |                 |                                           |

| ddr_dqs_n(10)  | clk_out             |              |          |          |          |                       |                 |                                           |

|                | aarina 🛶            |              |          |          |          |                       |                 |                                           |

- 7. Timing tab

- Command and Address Timing option

- Refresh, Reset and Power Timing option

#### Figure 8-7 Timing Tab

|               |                                | General      |                    |                        |                      |                               |               |

|---------------|--------------------------------|--------------|--------------------|------------------------|----------------------|-------------------------------|---------------|

|               | pl_stop                        | Device:      | GW5AST-138         |                        | Device Version:      | В                             |               |

| ddr_add(12:0) | memory_ck                      | Part Number: | GW5AST-LV138FF     | G676AES                | Language:            | Verilog                       |               |

| ddr_baj2:0j   | piljack 🖛                      | File Name:   | ddr3_memory_in     | terface                | Module Name:         | DDR3_Memory_Interface_Top     |               |

|               | ck 🖛                           | Create In:   | DR3\Gowin DDR3     | Memory Interface RefDe | sign\DDR3_MC_PHY_1vs | 4_5a138k\project\src\ddr3_mem | ory interface |

| dr_cs_n       | rat_n                          |              | prio (001111_00110 |                        |                      |                               | ory_interface |

| irjasja       | wr_data_en 🖛                   | Type Optic   | ons Timing         | Debug Setting          |                      |                               |               |

|               | wr_data(127:0)                 |              |                    |                        |                      |                               |               |

| casin         | wr_data_end wr.data_mask(15:0) | Command      | and Address Timi   | ng                     |                      |                               |               |

| uwe_n         | cmd_en                         | tRTP Perior  | d: 7500ps 🗘        | tRP Period: 12         | 500ps 🗘              |                               |               |

| cik           | cmd(2:0)                       | tWTR Peric   | od: 7500ps ≑       | tRC Period: 550        | 000ps ≑              |                               |               |

|               | addr(27:0)                     | tRAS Perio   | d: 37500ps 🗘       | tRCD Period: 12        | 500ps 🗘              |                               |               |

| ik_n          | sr_req 🖛                       |              | d: 40000ps 🗘       | tRRD Period: 75        |                      |                               |               |

| ke            | ref_req 🖛                      | traw perio   | u: +0000ps 👻       | IKKD Period: 75        | oops 👻               |                               |               |

|               | burst 🗲                        | Refresh Re   | set and Power Do   | vn Timing              |                      |                               |               |

| dt            | srjack 🗭                       | tCKE Perio   | d: 75000ps 🔹       | tREFI Period: 7        | 800000ps 🗧           |                               |               |

| set_n         | wr.data.rdy                    |              | d: 160000ps 🗘      |                        | 12 🗘                 |                               |               |

|               | init calb complete             | tkrc Perior  |                    | IDEEK:                 | •                    |                               |               |

| ąm(1:0)       | cmd_mady                       |              |                    |                        |                      |                               |               |

| q(15:0)       | rd_data_valid 🔶                |              |                    |                        |                      |                               |               |

|               | rd_data_end                    |              |                    |                        |                      |                               |               |

| iqs(1:0)      | nd_data(127:0)                 |              |                    |                        |                      |                               |               |

| lqs_n[10]     | clk_out 🛶                      |              |                    |                        |                      |                               |               |

|               | ddryst 🛶                       |              |                    |                        |                      |                               |               |

- 8. Debug Setting tab

- This option is used to enable debug interface and debug parameters.

Figure 8-8 Debug Setting Tab

|                |                      | General                                       |                                                                                                |                   |                          |                         |                     |   |   |

|----------------|----------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------|-------------------|--------------------------|-------------------------|---------------------|---|---|

|                |                      | Device:                                       | GW2A-18C                                                                                       |                   |                          | Part Number:            | GW2A-LV18PG256C8/I7 |   | _ |

| ddr addr[13:0] | memory_ck            | Create In: :\memory\DDR\DDR3\DDR3 MC PHY 1vs- |                                                                                                | 4 hs\project\ddr3 | 3 1v4 hs\src\ddr3 memory | interface               |                     |   |   |

|                | pll_bck 4            | File Name: ddr3_memory_interface              |                                                                                                |                   | 1                        | DDR3_Memory_Interface_T |                     |   |   |

| _ba(2:0)       | ck 🖛                 |                                               |                                                                                                |                   |                          |                         | op                  | _ |   |

| n              | vr data en           | Language:                                     | Verilog                                                                                        |                   | •                        | Synthesis Tool:         | GowinSynthesis      |   |   |