## Gowin RiscV AE250

## **User Guide**

IPUG528-1.1E, 01/21/2020

#### Copyright© 2020 Guangdong Gowin Semiconductor Corporation. All Rights Reserved.

No part of this document may be reproduced or transmitted in any form or by any denotes, electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of GOWINSEMI.

#### Disclaimer

GOWINSEMI®, LittleBee®, Arora, and the GOWINSEMI logos are trademarks of GOWINSEMI and are registered in China, the U.S. Patent and Trademark Office and other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders, as described at www.gowinsemi.com.cn. GOWINSEMI assumes no liability and provides no warranty (either expressed or implied) and is not responsible for any damage incurred to your hardware, software, data, or property resulting from usage of the materials or intellectual property except as outlined in the GOWINSEMI Terms and Conditions of Sale. All information in this document should be treated as preliminary. GOWINSEMI may make changes to this document at any time without prior notice. Anyone relying on this documentation should contact GOWINSEMI for the current documentation and errata.

#### **Revision History**

| Date       | Version | Description                                                         |

|------------|---------|---------------------------------------------------------------------|

| 01/23/2019 | 1.0E    | Initial version published.                                          |

|            |         | The number of UART, SPI, IIC, PIT increased;                        |

| 01/21/2020 | 1.1E    | <ul> <li>Enable AHB and APB interfaces;</li> </ul>                  |

|            |         | C BIN file prestorage added;                                        |

|            |         | ACE and AXI removed;                                                |

|            |         | <ul> <li>The configuration options in chapter 5 updated;</li> </ul> |

|            |         | Figures and tables in chapter 4 to chapter 23 updated;              |

|            |         | IP name updated.                                                    |

## **Contents**

| Content                                            | si                                                                                                                                                                                                                                                                     |   |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| List of F                                          | iguresxvii                                                                                                                                                                                                                                                             |   |

| List of T                                          | ablesxx                                                                                                                                                                                                                                                                |   |

| 1 About                                            | This Guide1                                                                                                                                                                                                                                                            |   |

| 1.2 S<br>1.3 R<br>1.4 A                            | urpose                                                                                                                                                                                                                                                                 | • |

| 2 Overv                                            | ew3                                                                                                                                                                                                                                                                    | , |

| 3 Featur                                           | es and Performance4                                                                                                                                                                                                                                                    |   |

| 3.2 R                                              | eatures                                                                                                                                                                                                                                                                |   |

| 4 CPU C                                            | ore Overview6                                                                                                                                                                                                                                                          | , |

| 4.2 B<br>4.3 M<br>4.4 P<br>4.5 D                   | 25(F) Processor Features 6 ock Diagram 8 ajor Components 8 peline Stages and Activities 9 esign Hierarchy 10 AHB Platform 10                                                                                                                                           | ; |

| 5 Proce                                            | ssor Configuration Options12                                                                                                                                                                                                                                           |   |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6 | PU Core Configuration       12         ISA       13         Privilege Architecture       13         Bus Interface       15         Micro Architecture       15         Trace Interface       16         Device Regions       16         Write-through Regions       17 |   |

|                                                    |                                                                                                                                                                                                                                                                        |   |

|    | 5.2 Local Memory Configuration                    | 17 |

|----|---------------------------------------------------|----|

|    | 5.2.1 Instruction Local Memory                    | 17 |

|    | 5.2.2 Data Local Memory (DLM)                     | 18 |

|    | 5.2.3 Slave Port                                  | 18 |

|    | 5.3 Cache Configuration                           | 19 |

|    | 5.3.1 Cache                                       | 19 |

|    | 5.3.2 Instruction Cache                           | 19 |

|    | 5.3.3 Data Cache                                  | 19 |

|    | 5.4 Debug Configuration                           | 20 |

|    | 5.4.1 Debug Support                               | 20 |

|    | 5.4.2 DEBUG_VEC                                   | 20 |

|    | 5.4.3 Number of Trigger                           | 20 |

|    | 5.4.4 Program Buffer Size                         | 20 |

|    | 5.4.5 System Bus Access Support                   | 21 |

| 6  | Signals Description                               | 22 |

|    | 6.1 General Signals                               | 22 |

|    | 6.2 Interrupt Signals                             | 22 |

|    | 6.3 Debug Signals                                 | 23 |

|    | 6.4 Trace Signals                                 | 23 |

|    | 6.5 AHB Interface Signals                         | 23 |

|    | 6.6 Instruction Local Memory Interface Signals    | 24 |

|    | 6.7 Data Local Memory Interface Signals           | 25 |

|    | 6.8 Instruction Cache Interface Signals           | 27 |

|    | 6.9 Data Cache Interface Signals                  | 29 |

|    | 6.10 AHB Slave Port Signals                       | 32 |

|    | 6.11 BTB Interface Signals                        | 32 |

| 7  | Reset and Clocking Scheme                         | 34 |

|    | 7.1 Reset                                         | 34 |

|    | 7.2 Clock Domains                                 | 34 |

| 8  | Instruction Set Overview                          | 36 |

|    | 8.1 Introduction                                  | 36 |

|    | 8.2 Integer Registers                             |    |

|    | 8.3 Atomic Instructions                           |    |

|    | 8.3.1 Load-Reserved/Store-Conditional Instruction | 37 |

|    | 8.3.2 Atomic Memory Operation Instruction         |    |

|    | 8.4 Misaligned Memory Access                      |    |

|    | 8.4.1 Limitation                                  |    |

|    | 8.5 Floating Point ISA Extension                  | 37 |

|    | 8.5.1 FPU Features                                | 37 |

| o. | Physical Memory Attributes                        | 20 |

| IJ | ୮                                                 | วฮ |

| 9.1 Introduction                                      | 39 |

|-------------------------------------------------------|----|

| 9.2 Device Regions                                    | 40 |

| 9.3 Write-through Regions                             | 40 |

| 10 Local Memory                                       | 41 |

| 10.1 Introduction                                     | 41 |

| 10.2 Local Memory Spaces                              | 41 |

| 10.3 Local Memory Address Range                       | 42 |

| 10.4 Local Memory Usage Constraints                   | 43 |

| 10.5 Local Memory Interface                           | 43 |

| 11 Local Memory Slave Port                            | 45 |

| 11.1 Introduction                                     | 45 |

| 11.2 Latency of Transfer                              | 45 |

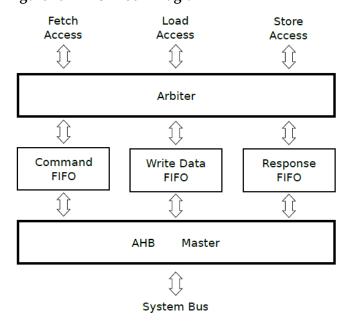

| 11.3 Basic Transfer                                   | 46 |

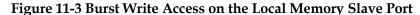

| 11.4 Burst Transfer                                   | 46 |

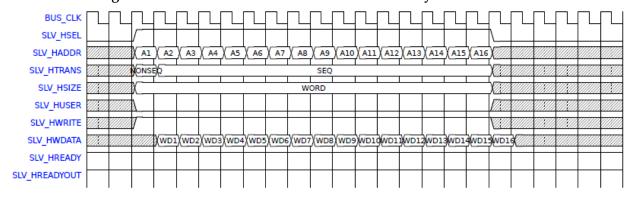

| 11.5 Support for Soft Error Protection                | 47 |

| 11.6 Local Memory Slave Port Operation under WFI Mode | 48 |

| 12 Caches                                             | 49 |

| 12.1 Introduction                                     | 49 |

| 12.2 Cache Access Latency                             | 50 |

| 12.3 I-Cache Fill Operation                           | 50 |

| 12.4 D-Cache Fill Operations                          | 51 |

| 12.5 D-Cache Eviction Operations                      | 51 |

| 12.6 FENCE/FENCE.I Operations                         | 51 |

| 13 Bus Interface Unit                                 | 52 |

| 13.1 Introduction                                     | 52 |

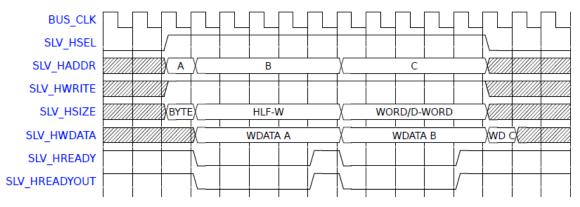

| 13.2 BIU Block Diagram                                | 52 |

| 13.3 Supported Transaction Types                      | 53 |

| 13.4 Atomic Operations                                | 53 |

| 13.5 Low Latency AHB Access Mode                      | 53 |

| 14 Trap                                               | 54 |

| 14.1 Introduction                                     | 54 |

| 14.2 Interrupt                                        | 54 |

| 14.3 Exception                                        | 55 |

| 14.4 Trap Handling                                    | 55 |

| 15 Reset and Non-Maskable Interrupts                  | 57 |

| 15.1 Reset                                            | 57 |

| 15.2 Non-Maskable Interrupts                          | 57 |

| 16 Power Management                                   | 58 |

| 16.1 Wait-For-Interrupt Mode                                    | 58 |

|-----------------------------------------------------------------|----|

| 17 Memory Subsystem Error Protection                            | 59 |

| 17.1 Introduction                                               | 59 |

| 17.1.1 Memory Subsystem Error Protection Scheme                 | 59 |

| 17.1.2 Error Protected Memory Subsystem                         | 59 |

| 17.1.3 Read-Modify-Write Operations                             | 60 |

| 17.2 Parity/ECC Control Mode and Access types                   | 60 |

| 17.2.1 Parity/ECC Checking Disabled                             | 60 |

| 17.2.2 Generating Exceptions on Uncorrectable Parity/ECC Errors | 60 |

| 17.2.3 Generating Exceptions on Parity/ECC Errors               |    |

| 17.2.4 Error Handling in Caches                                 | 61 |

| 17.2.5 Error Handling in ILM and DLM                            | 62 |

| 17.2.6 Behavior of Parity/ECC-Supported Local Memory Accesses   | 62 |

| 18 Control and Status Registers                                 | 64 |

| 18.1 Introduction                                               | 64 |

| 18.1.1 System Register Type                                     | 64 |

| 18.1.2 Reset Value                                              | 64 |

| 18.1.3 CSR Listing                                              | 64 |

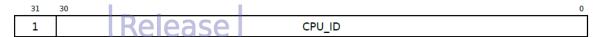

| 18.2 Machine Information Registers                              | 68 |

| 18.2.1 Machine Vendor ID Register                               | 68 |

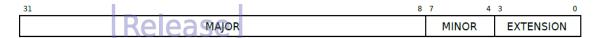

| 18.2.2 Machine Architecture ID Register                         | 69 |

| 18.2.3 Machine Implementation ID Register                       | 69 |

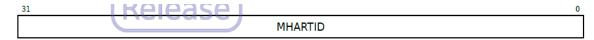

| 18.2.4 Hart ID Register                                         | 69 |

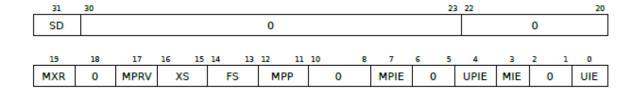

| 18.3 Machine Trap Related CSRs                                  | 70 |

| 18.3.1 Machine Status                                           | 70 |

| 18.3.2 Machine ISA Register                                     | 72 |

| 18.3.3 Machine Interrupt Enable                                 | 74 |

| 18.3.4 Machine Interrupt Pending                                | 76 |

| 18.3.5 Machine Trap Vector Base Address                         | 78 |

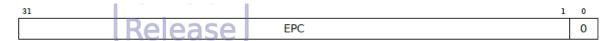

| 18.3.6 Machine Exception Program Counter                        | 79 |

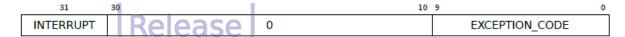

| 18.3.7 Machine Cause Register                                   | 79 |

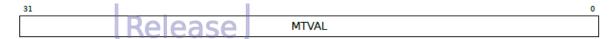

| 18.3.8 Machine Trap Value                                       | 81 |

| 18.3.9 Machine Scratch Register                                 | 81 |

| 18.3.10 Machine Extended Status                                 | 82 |

| 18.3.11 Machine Detailed Trap Cause                             | 82 |

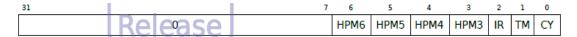

| 18.4 Counter Related CSRs                                       | 83 |

| 18.4.1 Machine Cycle Counter                                    | 83 |

| 18.4.2 Machine Instruction-Retired Counter                      | 84 |

| 18.4.3 Machine Performance Monitoring Counter                   | 84 |

| 18.4.4 Machine Performance Monitoring Event Selector            | 84 |

| 18.4.5 Machine Counter Enable                                   | 88 |

| 18 4 6 Machine Counter Write Enable                             | 89 |

| 18.4.7 Machine Counter Interrupt Enable                | 89  |

|--------------------------------------------------------|-----|

| 18.4.8 Machine Counter Mask for Machine Mode           | 90  |

| 18.4.9 Machine Counter Mask for Supervisor Mode        | 90  |

| 18.4.10 Machine Counter Mask for User Mode             | 90  |

| 18.4.11 Machine Counter Overflow Status                | 91  |

| 18.5 Configuration Control & Status Registers          | 91  |

| 18.5.1 Instruction Cache/Memory Configuration Register | 91  |

| 18.5.2 Data Cache/Memory Configuration Register        | 94  |

| 18.5.3 Misc. Configuration Register                    | 97  |

| 18.6 Trigger Registers                                 | 100 |

| 18.6.1 Trigger Select                                  | 100 |

| 18.6.2 Trigger Data 1                                  | 101 |

| 18.6.3 Trigger Data 2                                  | 102 |

| 18.6.4 Trigger Data 3                                  | 102 |

| 18.6.5 Trigger Info                                    | 103 |

| 18.6.6 Trigger Contorl                                 | 103 |

| 18.6.7 Machine Context                                 | 104 |

| 18.6.8 Match Control                                   | 104 |

| 18.6.9 Instruction Count                               | 106 |

| 18.6.10 Interrupt Trigger                              | 107 |

| 18.6.11 Exception Trigger                              | 108 |

| 18.7 Debug and Trigger Registers                       | 109 |

| 18.7.1 Debug Control and Status Register               | 109 |

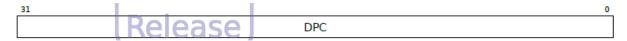

| 18.7.2 Debug Program Counter                           | 112 |

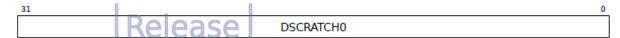

| 18.7.3 Debug Scratch Register 0                        | 113 |

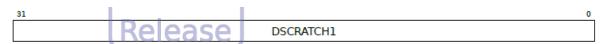

| 18.7.4 Debug Scratch Register 1                        | 113 |

| 18.7.5 Exception Redirection Register                  | 113 |

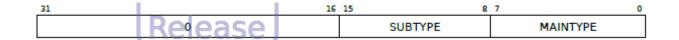

| 18.7.6 Debug Detailed Cause                            | 116 |

| 18.8 Memory and Miscellaneous Registers                | 118 |

| 18.8.1 Instruction Local Memory Base Register          | 118 |

| 18.8.2 Data Local Memory Base Register                 | 119 |

| 18.8.3 ECC Code Register                               | 120 |

| 18.8.4 NMI Vector Base Address Register                | 121 |

| 18.8.5 Performance Throttling Control Register         | 122 |

| 18.8.6 Cache Control Register                          | 122 |

| 18.8.7 Machine Miscellaneous Control Register          | 125 |

| 18.8.8 Machine CCTL Begin Address                      | 127 |

| 18.8.9 Machine CCTL Command                            | 128 |

| 18.8.10 Machine CCTL Data                              | 129 |

| 18.8.11 User CCTL Begin Address                        | 130 |

| 18.8.12 User CCTL Command                              | 131 |

| 18.9 Hardware Stack Protection and Recording Registers |     |

| 18.9.1 Machine Hardware Stack Protection Control       | 132 |

| 18.9.2 Machine SP Bound Register                       | 134 |

| 1     | 18.9.3 Machine SP Base Register                                         | . 134 |

|-------|-------------------------------------------------------------------------|-------|

| 1     | 18.10 CoDense Registers                                                 | 135   |

| 1     | 18.10.1 Instruction Table Base Address Register                         | 135   |

| 1     | 18.11 Physical Memory Protection Unit Configuration & Address Registers | . 136 |

| 1     | 18.11.1 PMP Configuration Registers                                     | . 136 |

| 1     | I8.11.2 PMP Address Register                                            | . 138 |

| 19 Ir | nstruction Latency                                                      | 140   |

| 1     | 19.1 ALU Instructions                                                   | . 140 |

|       | 19.2 Load Instructions                                                  |       |

| 1     | 19.3 Multiply Instructions                                              | 141   |

| 1     | 19.4 Divide and Remainder Instructions                                  | 141   |

|       | 19.5 Branch and Jump Instruction                                        |       |

| 1     | 19.6 Trap Return Instruction                                            | . 142 |

| 20 A  | E250 AHB Platform                                                       | 143   |

|       | 20.1 I/O Signal                                                         |       |

|       | 20.2 AE250 Memory Map                                                   |       |

|       | 20.3 Interrupt Assignment                                               |       |

|       | 20.4 Functional Description                                             |       |

|       | 20.4.1 ATCBMC200 – AHB Bus Matrix                                       |       |

|       | 20.4.2 ATCAPBBRG100 – AHB-to-APB Bridge                                 |       |

|       | 20.4.3 ATCUART100 – UART Controller                                     |       |

|       | 20.4.4 ATCSPI200 – SPI Controller                                       |       |

| 2     | 20.4.5 ATCIIC100 – I2C Controller                                       | 150   |

|       | 20.4.6 ATCWDT200 – Watchdog Timer                                       |       |

|       | 20.4.7 ATCRTC100 – Real-Time Clock                                      |       |

|       | 20.4.8 ATCPIT100 – PIT Controller                                       |       |

|       | 20.4.9 ATCGPIO100 – GPIO Controller                                     |       |

|       | 20.4.10 ATCRAMBRG200 – RAM Bridge                                       |       |

|       | 20.4.11 ATCDMAC100 – DMA Controller                                     |       |

|       | 20.5 System Management Unit                                             |       |

|       | 20.5.1 Summary of Registers                                             |       |

|       | 20.5.2 SYSTEM ID & Revision Register (SYSTEMVER) (0x00)                 |       |

|       | 20.5.3 Wake-up and Reset Status Register (WRSR) (0x10)                  |       |

|       | 20.5.4 SMU Command Register (SMUCR) (0x14)                              |       |

|       | 20.5.5 Wake-up and Reset Mask Register (WRMASK) (0x1c)                  |       |

|       | 20.5.6 Clock Enable Register (CER) (0x20)                               |       |

|       | 20.5.7 Clock Ratio Register (CRR) (0x24)                                |       |

|       | 20.5.8 Scratch Pad Register (SCRATCH) (0x40)                            |       |

| 2     | 20.5.9 Reset Vector (RESET_VECTOR) (0x50)                               | . 160 |

| 21 P  | latform-Level Interrupt Controller (PLIC)                               | 161   |

| 2     | P1.1 Introduction                                                       | 161   |

IPUG528-1.1E

|    | 21.2 Support for Preemptive Priority Interrupt               | 162 |

|----|--------------------------------------------------------------|-----|

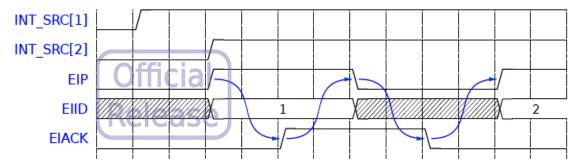

|    | 21.2.1 Interrupt Claims with Preemptive Priority             | 163 |

|    | 21.2.2 Interrupt Completion with Preemptive Priority         | 163 |

|    | 21.3 Vectored Interrupts                                     | 163 |

|    | 21.3.1 Vector Mode Protocol                                  | 164 |

|    | 21.4 PLIC Configuration Options                              | 165 |

|    | 21.4.1 Number of Interrupts                                  | 165 |

|    | 21.4.2 Number of Targets                                     | 165 |

|    | 21.4.3 Maximum Interrupt Priority                            | 165 |

|    | 21.4.4 Edge Trigger                                          | 165 |

|    | 21.4.5 Asynchronous Interrupt Source                         | 166 |

|    | 21.4.6 Address Width of PLIC Bus Interface                   | 166 |

|    | 21.4.7 Data Width of PLIC Bus Interface                      | 166 |

|    | 21.4.8 Support For Vectored PLIC Extension                   | 166 |

|    | 21.4.9 Bus Type of PLIC                                      | 166 |

|    | 21.5 PLIC Registers                                          | 166 |

|    | 21.5.1 Memory Map                                            | 166 |

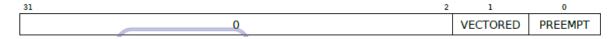

|    | 21.5.2 Feature Enable Register                               | 167 |

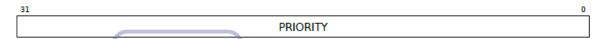

|    | 21.5.3 Interrupt Source Priority                             | 168 |

|    | 21.5.4 Interrupt Pending                                     | 168 |

|    | 21.5.5 Interrupt Trigger Type                                | 169 |

|    | 21.5.6 Number of Interrupt and Target Configuration Register | 169 |

|    | 21.5.7 Version & Maximum Priority Configuration Register     | 170 |

|    | 21.5.8 Interrupt Enable Bits for Target m                    | 170 |

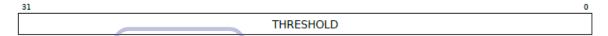

|    | 21.5.9 Priority Threshold for Target m                       | 170 |

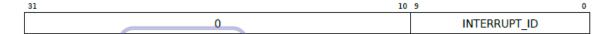

|    | 21.5.10 Claim and Complete Register for Target m             | 171 |

|    | 21.5.11 Preempted Priority Stack Registers for Target m      | 171 |

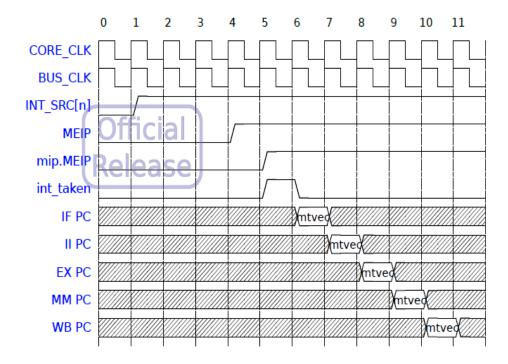

|    | 21.6 Interrupt Latency                                       | 172 |

|    | 21.7 Interface Signals                                       | 173 |

| 22 | 2 Machine Timer                                              | 175 |

|    | 22.4 Introduction                                            | 475 |

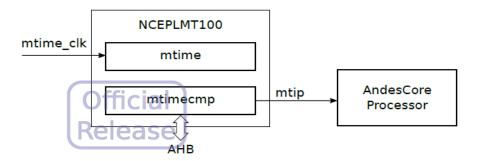

|    | 22.1 Introduction                                            |     |

|    | 22.2 Machine Timer Registers                                 |     |

|    | 22.3 Interface Signals                                       | 177 |

| 23 | 3 Debug Subsystem                                            | 179 |

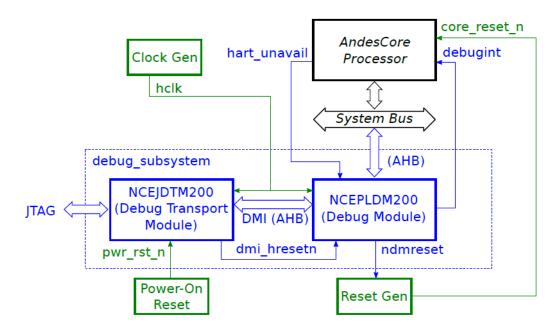

|    | 23.1 Overview                                                | 179 |

|    | 23.2 Integration Requirements                                | 180 |

|    | 23.3 Debug Subsystem Configuration Options                   | 181 |

|    | 23.4 NCEPLDM200                                              | 181 |

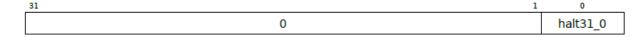

|    | 23.4.1 Abstract Data 0–3 (data0–3)                           | 182 |

|    | 23.4.2 Debug Module Control (dmcontrol)                      | 182 |

|    | 23.4.3 Debug Module Status (dmstatus)                        | 183 |

|    | 23.4.4 Hart Info (hartinfo)                                  | 185 |

|    | 23.4.5 Halt Summary (haltsum)                         | 186   |

|----|-------------------------------------------------------|-------|

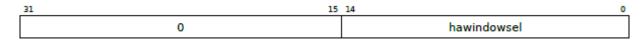

|    | 23.4.6 Hart Array Window Select (hawindowsel)         | 186   |

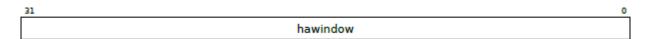

|    | 23.4.7 Hart Array Window (hawindow)                   | 186   |

|    | 23.4.8 Abstract Control and Status (abstractcs)       | 187   |

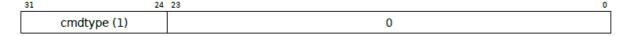

|    | 23.4.9 Abstract Command                               | 187   |

|    | 23.4.10 Abstract Command Autoexec (abstractauto)      | 190   |

|    | 23.4.11 Device Tree Addr 0–3 (devtreeaddr0–3)         | 191   |

|    | 23.4.12 Program Buffer 0–15 (progbuf0–15)             | 191   |

|    | 23.4.13 Authentication Data (authdata)                | 191   |

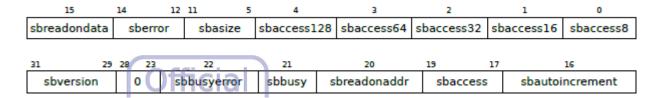

|    | 23.4.14 System Bus Access Control and Status (sbcs)   | 191   |

|    | 23.4.15 System Bus Address (sbaddress0–2)             | 194   |

|    | 23.4.16 System Bus Data (sbdata0-3)                   | 194   |

|    | 23.4.17 Interface Signals                             | 194   |

|    | 23.4.18 Non-polling access to Debug Module            | 197   |

|    | 23.5 NCEJDTM200                                       | 197   |

|    | 23.5.1 Interface Signal                               | 198   |

|    | 23.5.2 BYPASS                                         | 198   |

|    | 23.5.3 IDCODE                                         | 198   |

|    | 23.5.4 DTM Control and Status (dtmcs)                 | 199   |

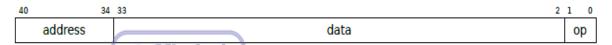

|    | 23.5.5 Debug Module Interface Access (dmi)            | 199   |

| 24 | 4 ATCWDT200                                           | 201   |

| 24 | *A1CWD1200                                            | 201   |

|    | 24.1 Introduction                                     | 201   |

|    | 24.1.1 Features                                       | 201   |

|    | 24.1.2 Block Diagram                                  | 201   |

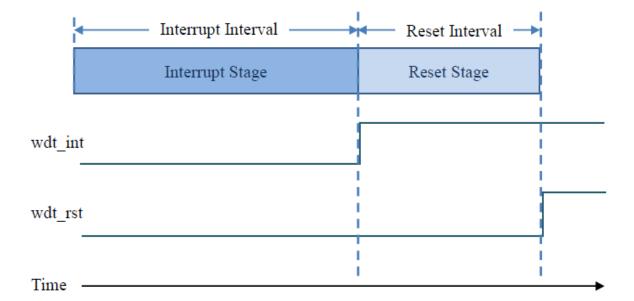

|    | 24.1.3 Function Description                           | 202   |

|    | 24.2 Signal Description                               | 203   |

|    | 24.3 Programming Model                                | 204   |

|    | 24.3.1 Summary of Registers                           | 204   |

|    | 24.3.2 Register Description                           | 204   |

|    | 24.3.3 ID and Revision Register (0x00)                | 204   |

|    | 24.3.4 Control Register (0x10)                        | 205   |

|    | 24.3.5 Restart Register (0x14)                        | 206   |

|    | 24.3.6 Write Enable Register (0x18)                   | 207   |

|    | 24.3.7 Status Register (0x1C)                         | 207   |

|    | 24.4 Hardware Configuration Options                   | 207   |

|    | 24.4.1 Magic Number for Write Protection              | 207   |

|    | 24.4.2 Magic Number for Restarting the Watchdog Timer | 208   |

|    | 24.4.3 Duration of Watchdog Interrupt Timer Interval  | 208   |

|    | 24.5 Programming Sequence                             | 208   |

|    | 24.5.1 Setup and Enable the Watchdog Timer:           | 208   |

|    | 24.5.2 Restart the Watchdog Timer                     | 208   |

|    | 24.5.3 Disable the Watchdog Timer                     | 209   |

| 25 | 5 ATCRTC100                                           | 240   |

| ZJ | <i>,</i>                                              | ∠ I U |

|    | 25.1 Introduction                                             | . 210 |

|----|---------------------------------------------------------------|-------|

|    | 25.1.1 Description                                            | . 210 |

|    | 25.1.2 Features                                               | . 210 |

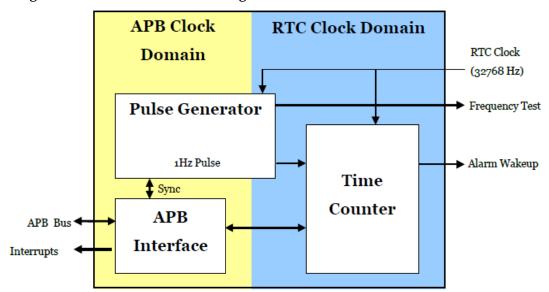

|    | 25.1.3 Block Diagram                                          | . 210 |

|    | 25.2 Signal Description                                       | . 211 |

|    | 25.3 Programming Model                                        | . 212 |

|    | 25.3.1 Summary of Registers                                   | . 212 |

|    | 25.3.2 Register Description                                   | . 213 |

|    | 25.3.3 ID and Revision Register (0x00)                        | . 213 |

|    | 25.3.4 Counter Register (0x10)                                | . 213 |

|    | 25.3.5 Alarm Register (0x14)                                  | . 214 |

|    | 25.3.6 Control Register (0x18)                                | . 214 |

|    | 25.3.7 Status Register (0x1C)                                 | . 215 |

|    | 25.3.8 Digital Trimming Register (0x20)                       | . 216 |

|    | 25.4 Hardware Configuration Options                           | . 217 |

|    | 25.4.1 Day Counter Bits                                       | . 217 |

|    | 25.4.2 Half-second Interrupt Support                          | . 218 |

|    | 25.5 Programming Sequence                                     | . 218 |

|    | 25.5.1 Adjust Time and Interrupts on the Hour                 | . 218 |

|    | 25.5.2 Trigger an Alarm Interrupt at a Specific Time          | . 218 |

|    | 25.5.3 Trigger an Alarm Wakeup Signal at a Specific Time      | . 218 |

|    | 25.5.4 Hardware Digital Trimming                              | . 218 |

|    | 25.5.5 Determining Trimming Value by Measuring Frequency      | . 220 |

|    | 25.5.6 Determining Trimming Value by Observing Time Deviation | . 220 |

|    | 25.5.7 Trimming Capabilities                                  | . 221 |

| 26 | ATCPIT100                                                     | 222   |

| 20 | ATCFIT 100                                                    | 223   |

|    | 26.1 Introduction                                             | . 223 |

|    | 26.1.1 Features                                               | . 223 |

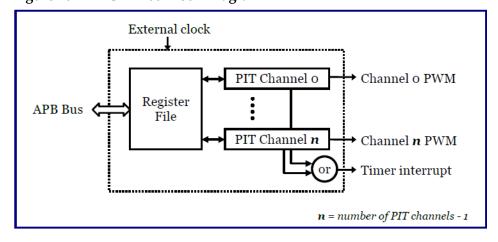

|    | 26.1.2 Block Diagram                                          | . 223 |

|    | 26.1.3 Function Description                                   | . 224 |

|    | 26.2 Signal Description                                       | . 224 |

|    | 26.3 Programming Model                                        | . 225 |

|    | 26.3.1 Summary of Registers                                   | . 225 |

|    | 26.3.2 Register Description                                   | . 226 |

|    | 26.3.3 ID and Revision Register (0x00)                        | . 226 |

|    | 26.3.4 Configuration Register (0x10)                          | . 227 |

|    | 26.3.5 Interrupt Enable Register (0x14)                       | . 228 |

|    | 26.3.6 Interrupt Status Register (0x18)                       | . 229 |

|    | 26.3.7 Channel Enable Register (0x1C)                         | . 230 |

|    | 26.3.8 Chn Control Register (0x20 + n * 0x10)                 | . 231 |

|    | 26.3.9 Chn Reload Register (0x24 + n * 0x10)                  | . 232 |

|    | 26.3.10 Chn Counter Register (0x28 + n * 0x10)                | . 233 |

|    | 26.4 Hardware Configuration Options                           | . 234 |

| 26.4.1 Number of PIT Channels                        | 234 |

|------------------------------------------------------|-----|

| 26.5 Programming Sequence                            | 234 |

| 26.5.1 Generate 2 Periodic Interrupts with Channel 0 | 234 |

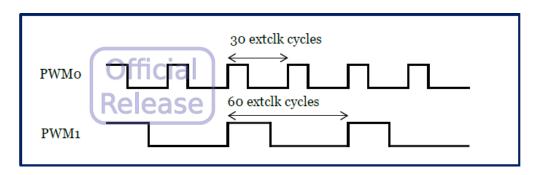

| 26.5.2 Generate 2 Aligned PWM Output                 | 235 |

| 26.5.3 Changing the PIT Modes                        | 235 |

| 27 ATCBUSDEC200                                      | 236 |

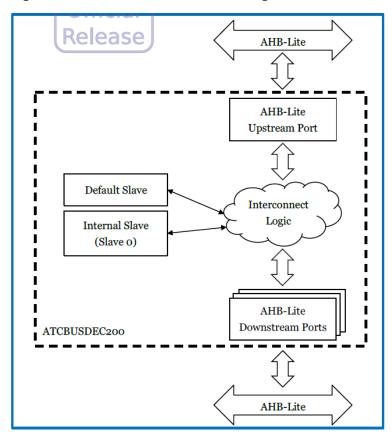

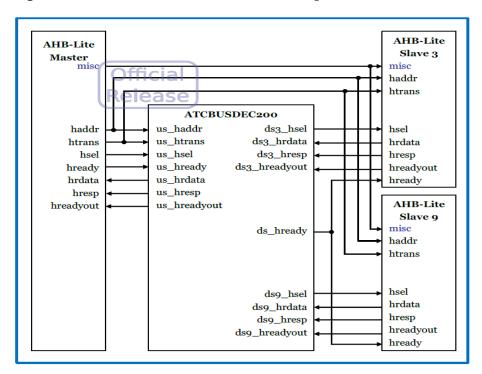

| 27.1 Introduction                                    | 236 |

| 27.1.1 Features                                      | 236 |

| 27.1.2 Block Diagram                                 | 236 |

| 27.1.3 Interconnect Logic                            | 237 |

| 27.1.4 Internal Slave                                | 237 |

| 27.1.5 Default Slave                                 | 237 |

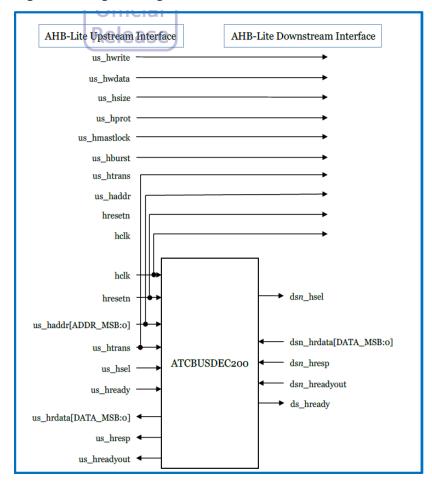

| 27.2 Signal Description                              | 238 |

| 27.3 Programming Model                               | 239 |

| 27.3.1 Summary of Registers                          | 239 |

| 27.3.2 Register Description                          | 239 |

| 27.3.3 ID and Revision Register                      | 240 |

| 27.3.4 Base/Size Register                            | 240 |

| 27.4 Hardware Configuration Options                  | 241 |

| 27.4.1 AHB-Lite Bus Address Width                    | 241 |

| 27.4.2 AHB-Lite Address Decode Width                 | 241 |

| 27.4.3 AHB-Lite Bus Data Width                       | 242 |

| 27.4.4 AHB-Lite Slave Ports                          | 242 |

| 27.4.5 AHB-Lite Slave Size                           | 242 |

| 27.4.6 AHB-Lite Slave Base Address Offset            | 243 |

| 27.4.7 AHB-Lite Default Slave Error Response         | 243 |

| 27.5 Integration Guideline                           | 243 |

| 27.6 Access Latencies                                | 244 |

| 28 ATCBMC200                                         | 245 |

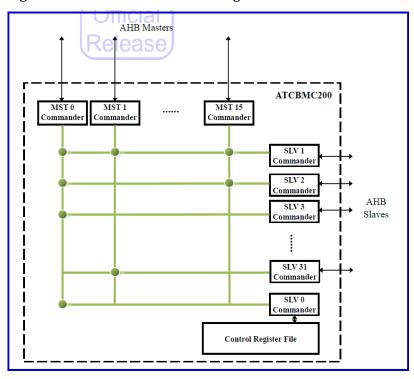

| 28.1 Introduction                                    | 245 |

| 28.1.1 Features                                      | 245 |

| 28.1.2 Block Diagram                                 | 245 |

| 28.1.3 Function Description                          | 246 |

| 28.1.4 MST Commander                                 | 246 |

| 28.1.5 SLV Commander                                 | 246 |

| 28.1.6 Bus Matrix                                    | 246 |

| 28.1.7 AHB Slave Grouping                            | 247 |

| 28.2 Signal Description                              | 247 |

| 28.3 Programming Model                               | 250 |

| 28.3.1 Summary of Registers                          | 250 |

| 28.3.2 Register Description                          | 251 |

| 28.3.3 ID and Revision Register (0x00)               | 251 |

| 28.3.4 Priority Register (0x10)                             | 251 |

|-------------------------------------------------------------|-----|

| 28.3.5 Control Register (0x14)                              | 252 |

| 28.3.6 Interrupt Status Register (0x18)                     | 253 |

| 28.3.7 Base/Size Register of AHB Slave 1–10 (0x20–0x44)     | 255 |

| 28.3.8 Base/Size Register of AHB Slave 11–15 (0x48–0x58)    | 256 |

| 28.4 Hardware Configuration Options                         | 257 |

| 28.4.1 Address Width                                        | 257 |

| 28.4.2 Number of AHB Master Ports                           | 257 |

| 28.4.3 Number of AHB Slave Ports                            | 257 |

| 28.4.4 Master and Slave Ports Connectivity                  | 257 |

| 28.4.5 Slave Base Address                                   | 258 |

| 28.4.6 Slave Size                                           | 258 |

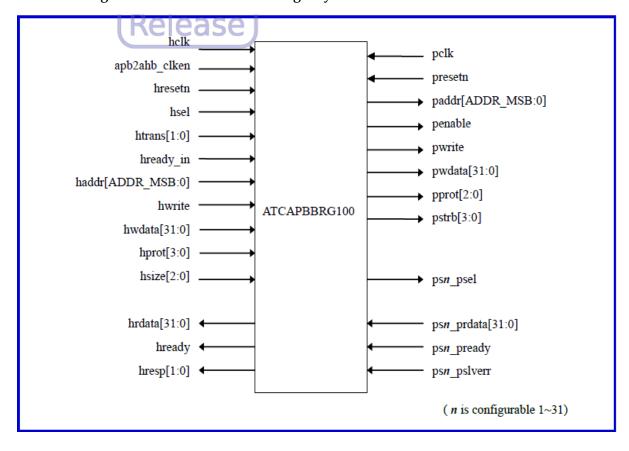

| 29 ATCAPBBRG100                                             | 260 |

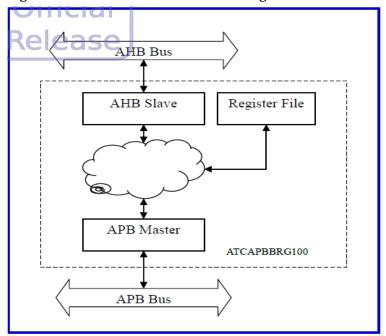

| 29.1 Introduction                                           | 260 |

| 29.1.1 Features                                             |     |

| 29.1.2 Block Diagram                                        |     |

| 29.1.3 Function Description                                 |     |

| 29.2 Signal Description                                     |     |

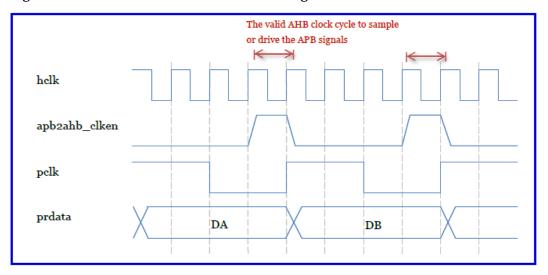

| 29.2.1 Clock Enable Signal                                  |     |

| 29.3 Programming Model                                      |     |

| 29.3.1 Summary of Registers                                 |     |

| 29.3.2 Register Description                                 | 265 |

| 29.3.3 ID and Revision Register (0x00)                      | 265 |

| 29.3.4 Control Register (0x14)                              | 265 |

| 29.3.5 Base/Size Register of Slave 1~n (0x20 + (n-1) * 0x4) | 266 |

| 29.4 Hardware Configuration Options                         | 268 |

| 29.4.1 Address Width                                        | 268 |

| 29.4.2 Address Decode Width                                 | 268 |

| 29.4.3 APB Slave Ports                                      | 269 |

| 29.4.4 APB Slave Size                                       | 269 |

| 29.4.5 APB Slave Base Address Offset                        | 269 |

| 29.5 Access Latencies                                       | 269 |

| 30 ATCAPBDEC100                                             | 271 |

| 30.1 Introduction                                           | 271 |

| 30.1.1 Features                                             | 271 |

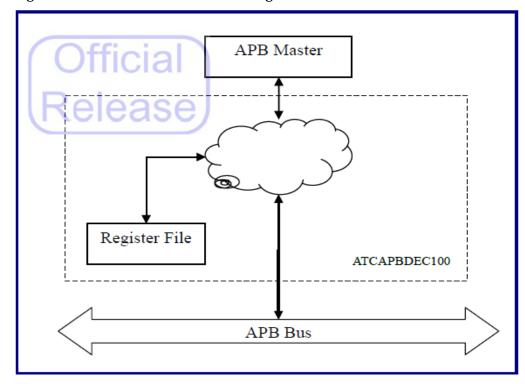

| 30.1.2 Block Diagram                                        | 271 |

| 30.1.3 Function Description                                 | 272 |

| 30.2 Signal Description                                     | 272 |

| 30.3 Programming Model                                      | 274 |

| 30.3.1 Summary of Registers                                 | 274 |

| 30.3.2 Register Description                                 |     |

| 30.3.3 ID and Revision Register (0x00)                      | 274 |

|    | 30.3.4 Base/Size Register of Slave 1~ n (0x20 + (n-1) * 0x4)        | 274 |

|----|---------------------------------------------------------------------|-----|

|    | 30.4 Hardware Configuration Options                                 | 276 |

|    | 30.4.1 Hardware Configuration Options                               | 276 |

|    | 30.4.2 Address Decode Width                                         | 276 |

|    | 30.4.3 APB Slave Ports                                              | 277 |

|    | 30.4.4 APB Slave Size                                               | 277 |

|    | 30.4.5 APB Slave Base Address Offset                                | 277 |

| 31 | ATCDMAC100                                                          | 278 |

|    | 31.1 Introduction                                                   | 278 |

|    | 31.1.1 Features                                                     | 278 |

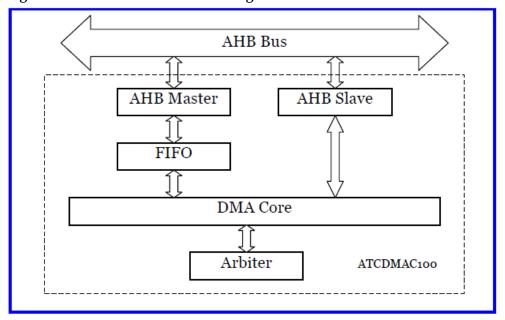

|    | 31.1.2 Block Diagram                                                | 278 |

|    | 31.1.3 Function Description                                         | 279 |

|    | 31.1.4 Channel Arbitration                                          | 280 |

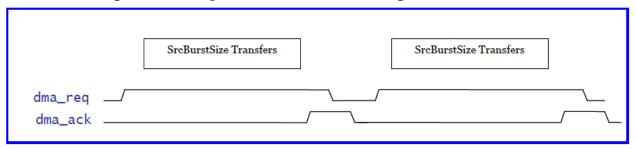

|    | 31.1.5 Hardware Handshaking                                         | 280 |

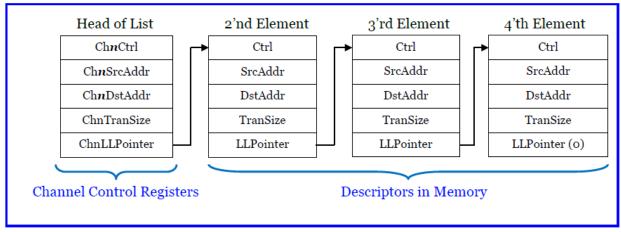

|    | 31.1.6 Chain Transfer                                               | 281 |

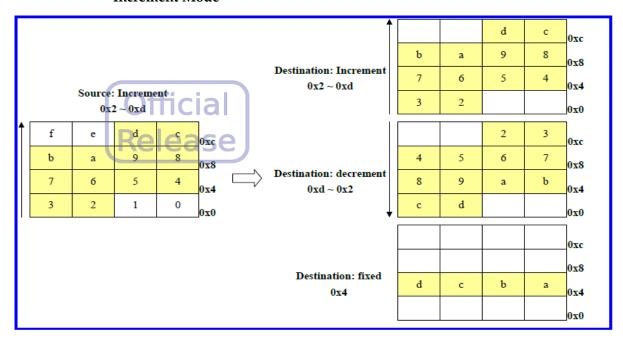

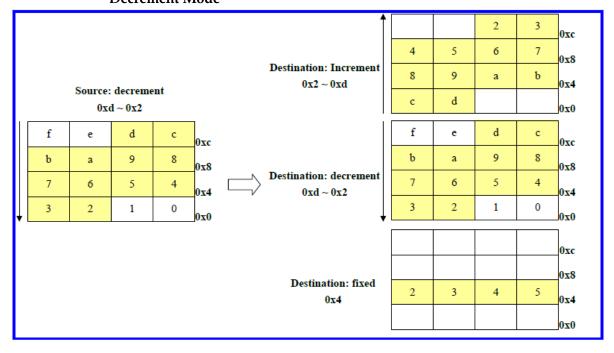

|    | 31.1.7 Data Order                                                   | 282 |

|    | 31.2 Signal Description                                             | 284 |

|    | 31.3 Programming Model                                              | 286 |

|    | 31.3.1 Register Summary                                             | 286 |

|    | 31.3.2 Register Description                                         | 287 |

|    | 31.3.3 ID and Revision Register (Offset 0x00)                       | 287 |

|    | 31.3.4 DMAC Configuration Register (Offset 0x10)                    | 288 |

|    | 31.3.5 DMAC Control Register (Offset 0x20)                          | 289 |

|    | 31.3.6 Interrupt Status Register (Offset 0x30)                      | 289 |

|    | 31.3.7 Channel Enable Register (Offset 0x34)                        | 290 |

|    | 31.3.8 Channel Abort Register (Offset 0x40)                         | 290 |

|    | 31.3.9 Channel n Control Register (Offset 0x44+n*0x14)              | 291 |

|    | 31.3.10 Channel n Source Address Register (Offset 0x48+n*0x14)      | 294 |

|    | 31.3.11 Channel n Destination Address Register (Offset 0x4C+n*0x14) |     |

|    | 31.3.12 Channel n Transfer Size Register (Offset 0x50+n*0x14)       |     |

|    | 31.3.13 Channel n Linked List Pointer Register (Offset 0x54+n*0x14) |     |

|    | 31.4 Hardware Configuration Options                                 | 295 |

|    | 31.4.1 Number of DMA Channels                                       | 295 |

|    | 31.4.2 FIFO Size                                                    | 295 |

|    | 31.4.3 DMA Request/Acknowledge Number                               | 295 |

|    | 31.4.4 DMA Request Synchronization Support                          | 295 |

|    | 31.4.5 Chain Transfer Support                                       | 295 |

|    | 31.4.6 Address Width                                                |     |

|    | 31.5 Programming Sequence                                           |     |

|    | 31.5.1 Transfer without Chain Transfer                              |     |

|    | 31.5.2 Chain Transfer                                               | 297 |

| 22 | ATCGPIO100                                                          | 300 |

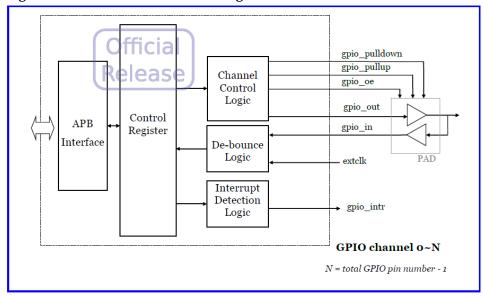

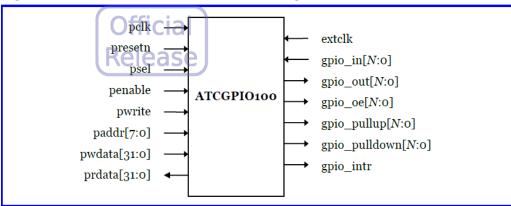

|    | 32.1 Introduction                                                | 300 |

|----|------------------------------------------------------------------|-----|

|    | 32.1.1 Description                                               | 300 |

|    | 32.1.2 Features                                                  | 300 |

|    | 32.1.3 Block Diagram                                             | 300 |

|    | 32.1.4 Function Description                                      | 301 |

|    | 32.2 Signal Description                                          | 301 |

|    | 32.3 Programming Model                                           | 302 |

|    | 32.3.1 Summary of Registers                                      | 302 |

|    | 32.3.2 Register Description                                      | 304 |

|    | 32.3.3 ID and Revision Register (Offset 0x00)                    | 304 |

|    | 32.3.4 Configuration Register (Offset 0x10)                      | 304 |

|    | 32.3.5 Channel Data-In Register (Offset 0x20)                    | 305 |

|    | 32.3.6 Channel Data-Out Register (Offset 0x24)                   | 305 |

|    | 32.3.7 Channel Direction Register (Offset 0x28)                  | 305 |

|    | 32.3.8 Channel Data-Out Clear Register (Offset 0x2C)             | 305 |

|    | 32.3.9 Channel Data-Out Set Register (Offset 0x30)               | 305 |

|    | 32.3.10 Pull Enable Register (Offset 0x40)                       | 305 |

|    | 32.3.11 Pull Type Register (Offset 0x44)                         | 306 |

|    | 32.3.12 Interrupt Enable Register (Offset 0x50)                  | 306 |

|    | 32.3.13 Interrupt Mode Register (Offset 0x54, 0x58, 0x5C, 0x60): | 306 |

|    | 32.3.14 Channel Interrupt Status Register (Offset 0x64):         | 310 |

|    | 32.4 Hardware Configuration Options                              | 311 |

|    | 32.4.1 GPIO Channel Number                                       | 311 |

|    | 32.4.2 Pull Support                                              | 311 |

|    | 32.4.3 Interrupt                                                 | 311 |

|    | 32.4.4 De-bounce                                                 | 311 |

|    | 32.5 Programming Sequence                                        | 311 |

|    | 32.5.1 Output Channel Programming                                | 311 |

|    | 32.5.2 Input Channel Programming                                 | 311 |

|    | 32.5.3 Basic Input Channel                                       | 312 |

|    | 32.5.4 Input Channel with Additional Functions                   | 312 |

| 22 | ATCIIC100                                                        | 212 |

| 33 | ATCHC 100                                                        | 313 |

|    | 33.1 Introduction                                                | 313 |

|    | 33.1.1 Features                                                  | 313 |

|    | 33.1.2 Block Diagram                                             |     |

|    | 33.1.3 I <sup>2</sup> C Master                                   | 314 |

|    | 33.1.4 I <sup>2</sup> C Slave                                    | 314 |

|    | 33.1.5 General Call Address                                      | 314 |

|    | 33.1.6 Auto Clock Stretch                                        | 315 |

|    | 33.1.7 Auto-ACK                                                  | 315 |

|    | 33.1.8 Timing Parameter Multiplier                               | 315 |

|    | 33.2 Signal Description                                          | 315 |

|    | 33.3 Programming Model                                           | 316 |

|    | 33.3.1 Summary of Registers                       | 316         |

|----|---------------------------------------------------|-------------|

|    | 33.3.2 ID and Revision Register                   | 317         |

|    | 33.3.3 Configuration Register                     | 318         |

|    | 33.3.4 Interrupt Enable Register                  | 318         |

|    | 33.3.5 Status Register                            | 319         |

|    | 33.3.6 Address Register                           | 321         |

|    | 33.3.7 Data Register                              | 322         |

|    | 33.3.8 Control Register                           | 322         |

|    | 33.3.9 Command Register                           | 324         |

|    | 33.3.10 Setup Register                            | 324         |

|    | 33.3.11 Timing Parameter Multiplier Register      | 327         |

|    | 33.4 RTL Configuration                            | 327         |

|    | 33.4.1 Data FIFO Size                             | 327         |

|    | 33.5 Programming Sequence                         | 327         |

|    | 33.5.1 Timing Setup Guide                         | 327         |

|    | 33.5.2 Spike Suppression Width                    | 328         |

|    | 33.5.3 Data Setup Time                            | 328         |

|    | 33.5.4 Data Hold Time                             | 329         |

|    | 33.5.5 I <sup>2</sup> C-Bus Clock Frequency:      | 329         |

|    | 33.5.6 Timing Parameter Multiplier                | 331         |

|    | 33.5.7 Master Mode                                | 332         |

|    | 33.5.8 Data Transmit without DMA                  | 332         |

|    | 33.5.9 Data Receive without DMA                   | 333         |

|    | 33.5.10 Arbitration Lost in the Multi-Master Mode | 335         |

|    | 33.5.11 Slave Mode                                | 335         |

|    | 33.5.12 Data Transaction without DMA:             | 335         |

|    | 33.5.13 Data transaction with DMA                 | 336         |

| 34 | ATCSPI200                                         | <b>3</b> 38 |

| 04 |                                                   |             |

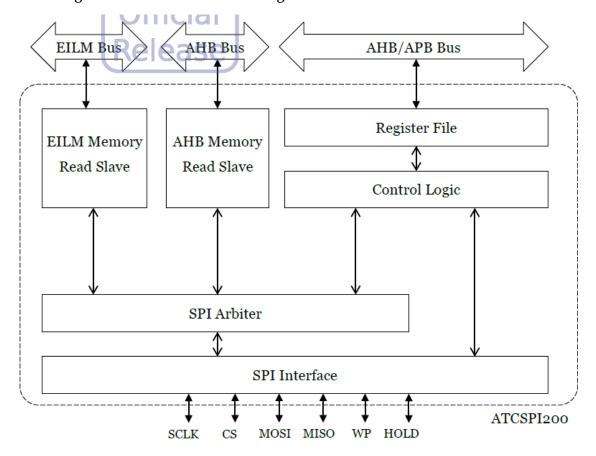

|    | 34.1 Introduction                                 |             |

|    | 34.1.1 Features                                   |             |

|    | 34.1.2 Block Diagram                              |             |

|    | 34.1.3 Master Mode                                |             |

|    | 34.1.4 Slave Mode                                 |             |

|    | 34.1.5 Dual I/O Mode                              |             |

|    | 34.1.6 Quad I/O Mode                              |             |

|    | 34.2 Signal Description                           |             |

|    | 34.3 Programming Model                            |             |

|    | 34.3.1 Summary of Registers                       |             |

|    | 34.3.2 Register Description                       |             |

|    | 34.3.3 ID and Revision Register (0x00)            |             |

|    | 34.3.4 SPI Transfer Format Register (0x10)        |             |

|    | 34.3.5 SPI Direct IO Control Register (0x14)      |             |

|    | 34.3.6 SPI Transfer Control Register (0x20)       | 352         |

|    | 34.3.7 SPI Command Register (0x24)                                      | 356 |

|----|-------------------------------------------------------------------------|-----|

|    | 34.3.8 SPI Address Register (0x28)                                      | 356 |

|    | 34.3.9 SPI Data Register (0x2C)                                         | 356 |

|    | 34.3.10 SPI Control Register (0x30)                                     | 358 |

|    | 34.3.11 SPI Status Register (0x34)                                      | 359 |

|    | 34.3.12 SPI Interrupt Enable Register (0x38)                            | 360 |

|    | 34.3.13 SPI Interrupt Status Register (0x3C)                            | 361 |

|    | 34.3.14 SPI Interface Timing Register (0x40)                            | 361 |

|    | 34.3.15 SPI Memory Access Control Register (0x50)                       | 362 |

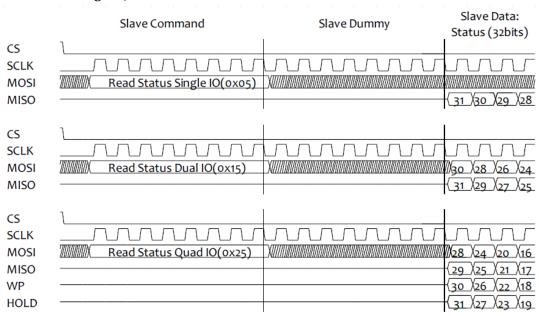

|    | 34.3.16 SPI Slave Status Register (0x60)                                | 364 |

|    | 34.3.17 SPI Slave Data Count Register (0x64)                            | 365 |

|    | 34.3.18 Configuration Register (0x7C)                                   | 366 |

|    | 34.4 Hardware Configuration Options                                     | 366 |

|    | 34.4.1 Address Width                                                    | 367 |

|    | 34.4.2 Dual I/O Mode                                                    | 367 |

|    | 34.4.3 Quad I/O Mode                                                    | 367 |

|    | 34.4.4 TX FIFO Depth                                                    | 367 |

|    | 34.4.5 RX FIFO Depth                                                    | 367 |

|    | 34.4.6 Direct IO Control                                                | 367 |

|    | 34.4.7 Memory-Mapped Access Support                                     | 368 |

|    | 34.4.8 Slave Mode                                                       | 368 |

|    | 34.4.9 AHB Register Port                                                | 368 |

|    | 34.4.10 Memory-Mapped AHB/EILM Read                                     | 368 |

|    | 34.4.11 SPI Interface Timing Parameters                                 | 368 |

|    | 34.5 Programming Sequence                                               | 369 |

|    | 34.5.1 SPI Write with DMA                                               | 369 |

|    | 34.5.2 SPI Read with DMA:                                               | 370 |

|    | 34.5.3 Stopping SPI Activities Initiated by the Memory-Mapped Interface | 371 |

|    | 34.5.4 Receiving Data from SPI Masters                                  | 372 |

|    | 34.5.5 Transmitting Data to SPI Masters                                 | 373 |

|    | 34.6 Integration Guideline                                              | 375 |

|    | 34.6.1 SCLK Frequency                                                   | 376 |

|    | 34.6.2 Time between the Edges of SPI CS to the First Edge of SCLK       | 376 |

|    | 34.6.3 Clock Enable Signal                                              | 376 |

|    | 34.6.4 Clock Gating Cell                                                | 377 |

|    | 34.6.5 DFT Considerations                                               | 379 |

| 35 | ATCUART100                                                              | 381 |

|    | 35.1 Introduction                                                       | 381 |

|    | 35.1.1 Features                                                         | 381 |

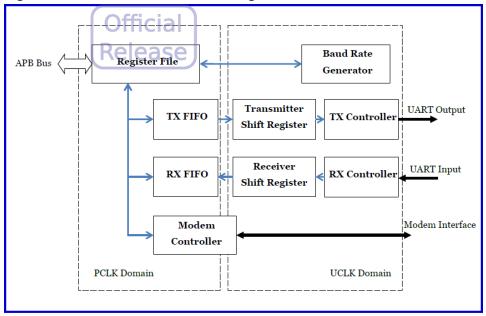

|    | 35.1.2 Block Diagram                                                    | 381 |

|    | 35.1.3 Transmitter                                                      | 382 |

|    | 35.1.4 Receiver                                                         | 382 |

|    | 35 1 5 Baud Rate Generator                                              | 383 |

| 35.1.6 Modem Controller                                    | 384 |

|------------------------------------------------------------|-----|

| 35.1.7 Loopback Mode                                       | 385 |

| 35.1.8 DMA Operation                                       | 386 |

| 35.2 Signal Description                                    | 386 |

| 35.3 Programming Model                                     | 388 |

| 35.3.1 Summary of Registers                                | 388 |

| 35.3.2 ID and Revision Register (0x00)                     | 389 |

| 35.3.3 Hardware Configure Register (0x10)                  | 390 |

| 35.3.4 Over Sample Control Register (0x14)                 | 390 |

| 35.3.5 Receiver Buffer Register (when DLAB = 0) (0x20)     | 390 |

| 35.3.6 Transmitter Holding Register (when DLAB = 0) (0x20) | 391 |

| 35.3.7 Interrupt Enable Register (when DLAB = 0) (0x24)    | 391 |

| 35.3.8 Divisor Latch LSB (when DLAB = 1) (0x20)            | 392 |

| 35.3.9 Divisor Latch MSB (when DLAB = 1) (0x24)            | 392 |

| 35.3.10 Interrupt Identification Register (0x28)           | 393 |

| 35.3.11 FIFO Control Register (0x28)                       | 395 |

| 35.3.12 Line Control Register (0x2C)                       | 396 |

| 35.3.13 Modem Control Register (0x30)                      | 397 |

| 35.3.14 Line Status Register (0x34)                        | 398 |

| 35.3.15 Modem Status Register (0x38)                       | 400 |

| 35.3.16 Scratch Register (0x3C)                            | 401 |

| 35.4 Hardware Configuration Options                        | 401 |

| 35.4.1 The Depth of FIFO                                   | 401 |

| 35.4.2 The Same Clock Source                               | 401 |

| 35.5 Programming Sequence                                  | 401 |

| 35.5.1 UART Setup                                          | 401 |

| 35.5.2 Data Transfer without DMA                           | 402 |

| 35.5.3 Data Transfer with DMA                              | 402 |

| 35.5.4 Receiving Data                                      | 403 |

| 35.5.5 Data Receive without DMA                            | 403 |

| 35.5.6 Data receive with DMA                               | 403 |

IPUG528-1.1E xvi

# **List of Figures**

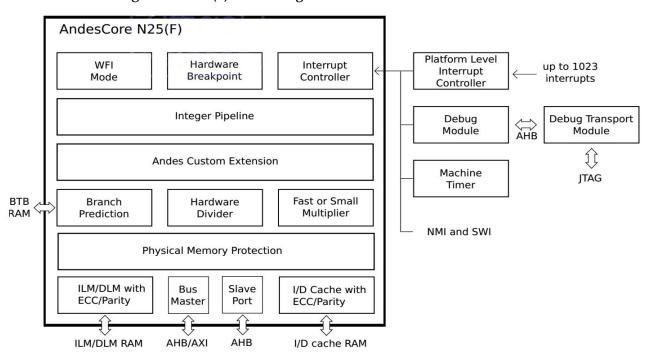

| Figure 4-1 N25(F) Block Diagram                               | 8     |

|---------------------------------------------------------------|-------|

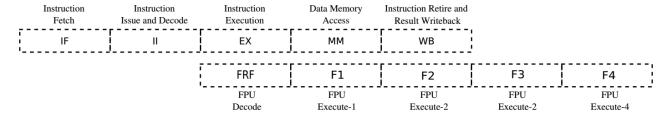

| Figure 4-2 Pipeline Stages and Activities                     | 9     |

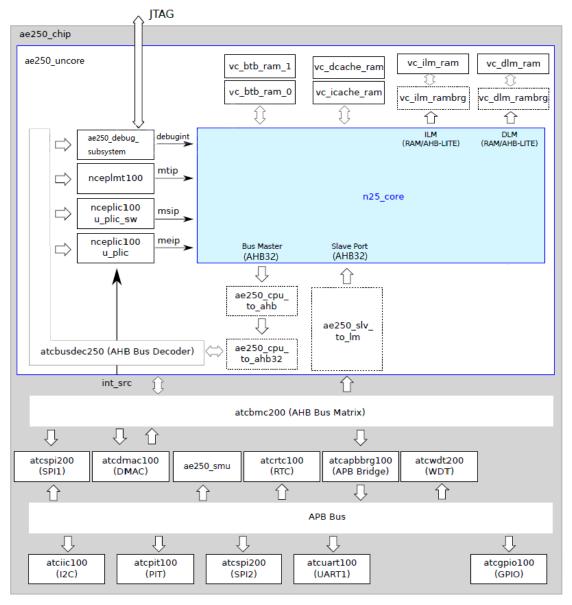

| Figure 4-3 Design Hierarchy                                   | . 11  |

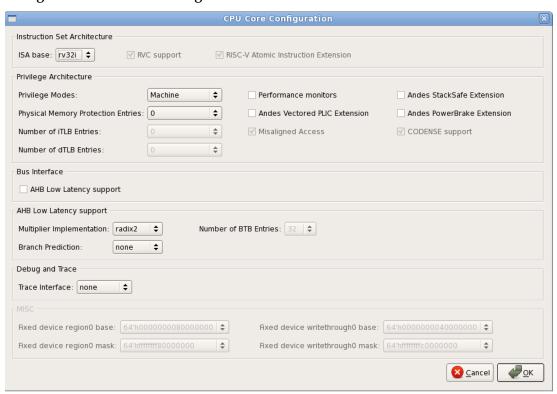

| Figure 5-1 CPU Core Configuration GUI                         | .12   |

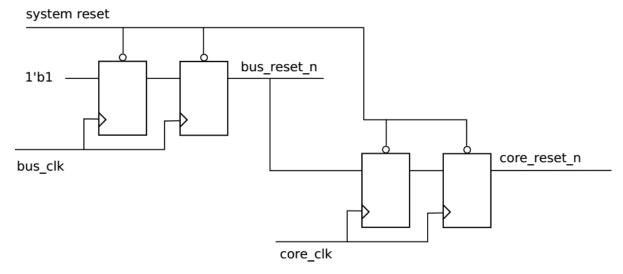

| Figure 7-1 Suggested Design for Reset Synchronization         | 34    |

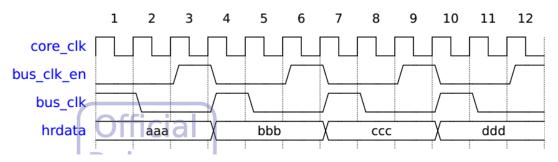

| Figure 7-2 BUS_CLK_EN Waveform for N:1 (3:1) Clock Ratio      | 35    |

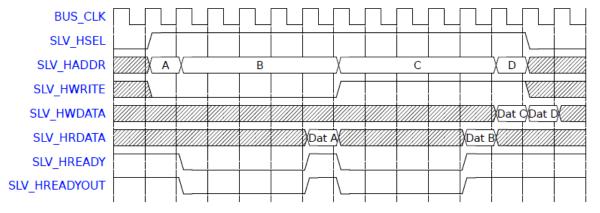

| Figure 11-1 Single Access on the Local Memory Slave Port      | 46    |

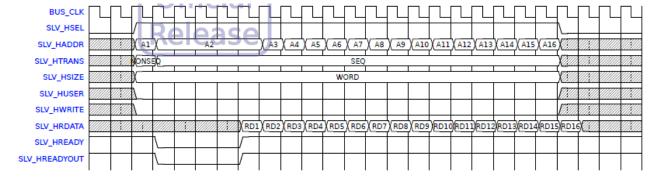

| Figure 11-2 Burst Read Access on the Local Memory Slave Port  | 47    |

| Figure 11-3 Burst Write Access on the Local Memory Slave Port | 47    |

| Figure 11-4 Various Size Write Transfers with ECC             | 48    |

| Figure 13-1 BIU Block Diagram                                 | 52    |

| Figure 21-1 NCEPLIC100 Block Diagram                          | 162   |

| Figure 21-2 NCEPLIC100 Vector Mode Protocol                   | 164   |

| Figure 21-3 Minimum Interrupt Latency                         | . 173 |

| Figure 22-1 NCEPLMT100 Block Diagram                          | 176   |

| Figure 23-1 Debug Subsystem Block Diagram                     | . 179 |

| Figure 24-1 ATCWDT200 Block Diagram                           | 202   |

| Figure 24-2 Stages of the Watchdog Timer                      | 202   |

| Figure 25-1 ATCRTC100 Block Diagram                           | 211   |

| Figure 26-1 ATCPIT100 Block Diagram                           | 223   |

| Figure 26-2 PWM Example Waveform                              | 235   |

| Figure 27-1 ATCBUSDEC200 Block Diagram                        | 237   |

| Figure 27-2 Signal Diagram                                    | . 238 |

IPUG528-1.1E

| Figure 27-3 ATCBUSDEC200 Connection Example                                                  | 244   |

|----------------------------------------------------------------------------------------------|-------|

| Figure 28-1 ATCBMC200 Block Diagram                                                          | 246   |

| Figure 28-2 ATCBMC200 I/O Signals                                                            | 248   |

| Figure 29-1 ATCAPBBRG100 Block Diagram                                                       | 261   |

| Figure 29-2 ATCAPBBRG100 Logic Symbol                                                        | 262   |

| Figure 29-3 ATCAPBBRG100 Clock Enable Signal for 4:1 AHB-to-APB Clock Ratio                  | 264   |

| Figure 30-1 ATCAPBDEC100 Block Diagram                                                       | 272   |

| Figure 30-2 ATCAPBDEC100 Input/Output Signals                                                | 273   |

| Figure 31-1 ATCDMAC100 Block Diagram                                                         | 279   |

| Figure 31-2 Example of DMA Data Transfers                                                    | 280   |

| Figure 31-3 Example of Hardware Handshaking                                                  | 281   |

| Figure 31-4 Linked List Structure for Chain Transfers                                        | 281   |

| Figure 31-5 Data Order at the Destination when the Source Address Mode is the Increment Mod  | e 283 |

| Figure 31-6 Data Order at the Destination when the Source Address Mode is the Decrement Mode |       |

| Figure 31-7 Data Order at the Destination when the Source Address Mode is the Fixed Mode     | 284   |

| Figure 31-8 ATCDMAC100 Interfaces                                                            | 284   |

| Figure 32-1 ATCGPIO100 Block Diagram                                                         | 301   |

| Figure 32-2 ATCGPIO100 Pin Connection Diagram                                                | 301   |

| Figure 33-1 ATCIIC100 Block Diagram                                                          | 314   |

| Figure 34-1 ATCSPI200 Block Diagram                                                          | 339   |

| Figure 34-2 SPI Transfer Format                                                              | 340   |

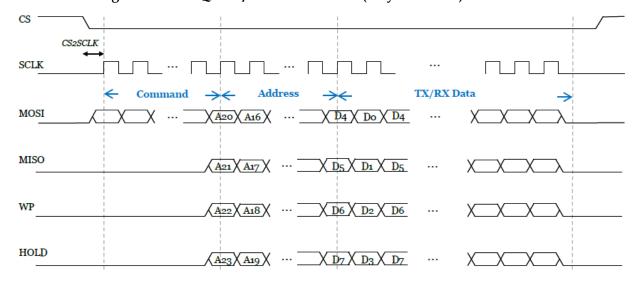

| Figure 34-3 Timing Diagram of Status-Reading Commands (MSB First, DataMerge=0)               | 341   |

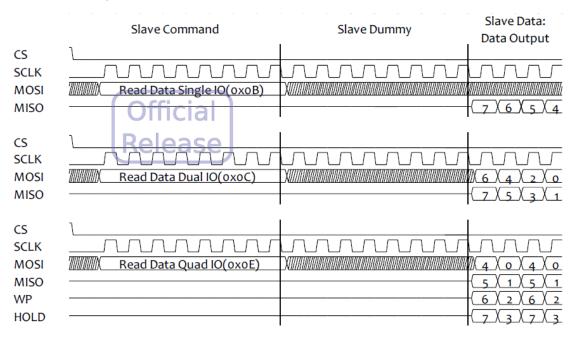

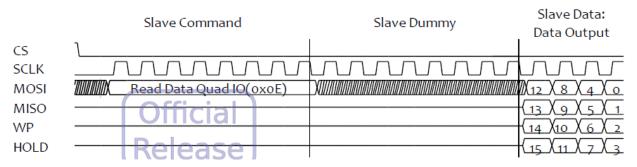

| Figure 34-4 Timing Diagram of Data-Reading Commands (MSB First, Merge Mode)                  | 342   |

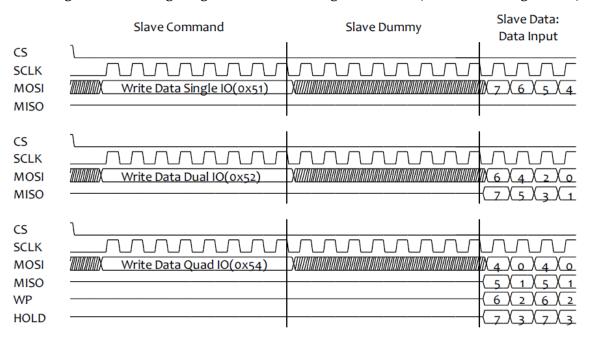

| Figure 34-5 Timing Diagram of Data-Writing Commands (MSB First, Merge Mode)                  | 342   |

| Figure 34-6 Timing Diagram of Data-Reading Commands (MSB First, Data Length = 16 Bits)       | 343   |

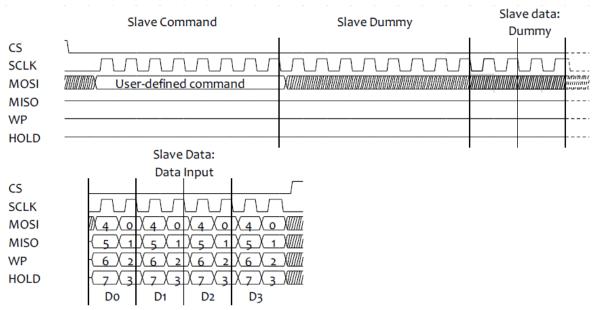

| Figure 34-7 Timing Diagram of Slave User-Defined Command (MSB First, Merge Mode, TransMale)  |       |

| Figure 34-8 SPI Dual I/O Transfer (3-byte address)                                           |       |

| rigure 54 0 01 1 Buar 1/0 Transier (5 byte address)                                          | 344   |

IPUG528-1.1E xviii

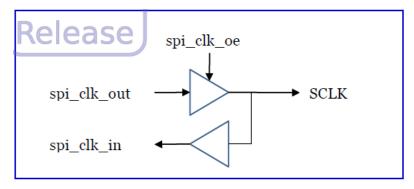

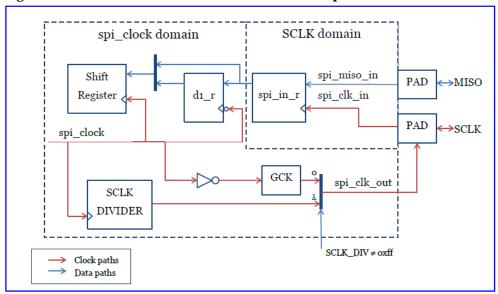

| Figure 34-10 SCLK I/O Pad                                                 | 376 |

|---------------------------------------------------------------------------|-----|

| Figure 34-11 Relation Between SCLK Domain and spi_clock Domain            | 376 |

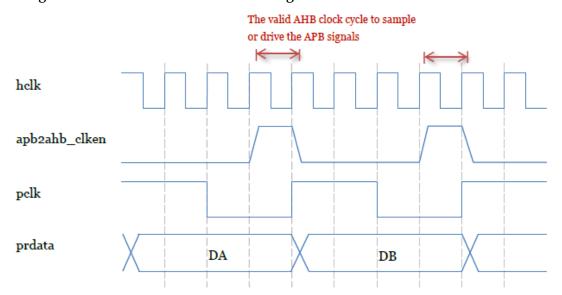

| Figure 34-12 ATCSPI200 Clock Enable Signal for 4:1 AHB-to-APB Clock Ratio | 377 |

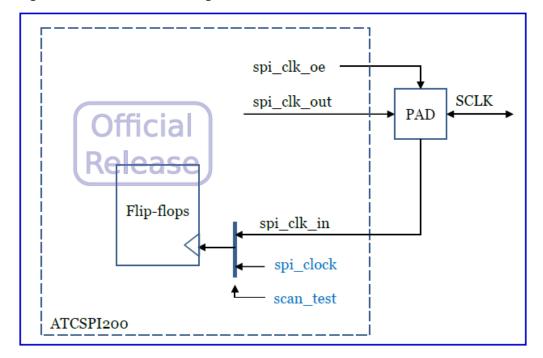

| Figure 34-13 Clock Gating Logic for Simulation and Synthesis              | 378 |

| Figure 34-14 Clock Gating Cell Diagram with Waveform                      | 379 |

| Figure 34-15 ATCSPI200 Design for ATPG Test                               | 380 |

| Figure 35-1 ATCUART100 Block Diagram                                      | 382 |

| Figure 35-2 Relationship between MCR and MSR in the Loopback Mode         | 385 |

IPUG528-1.1E xix

## **List of Tables**

|      | Table 1-1 Abbreviations and Terminology              | 2  |

|------|------------------------------------------------------|----|

|      | Table 2-1 Gowin RiscV AE250                          | 3  |

|      | Table 3-1 Gowin RiscV AE250 Resources Utilization    | 5  |

|      | Table 4-1 Major Components                           | 8  |

|      | Table 5-1 Supported Combination of Privilege Modes   | 13 |

|      | Table 6-1 General Signals                            | 22 |

|      | Table 6-2 Interrupt Signals                          | 22 |

|      | Table 6-3 Debug Signals                              | 23 |

|      | Table 6-4 Trace Signals                              | 23 |

|      | Table 6-5 AHB Interface Signals                      | 24 |

|      | Table 6-6 Instruction Local Memory Interface Signals | 24 |

|      | Table 6-7 Instruction Local Memory Address Bit-Width | 25 |

|      | Table 6-8 Instruction Local Memory Data Bit-Width    | 25 |

|      | Table 6-9 ILM Byte Write Enable Mapping              | 25 |

|      | Table 6-10 Data Local Memory Interface Signals       | 26 |

|      | Table 6-11 Data Local Memory Address Bit-Width       | 26 |

|      | Table 6-12 Data Local Memory Data Bit-Width          | 26 |

|      | Table 6-13 DLM Byte Write Enable Mapping             | 26 |

|      | Table 6-14 Instruction Cache Interface Signals       | 27 |

|      | Table 6-15 I-Cache Tag Address Bit-Width             | 27 |

|      | Table 6-16 I-Cache Tag Data Bit-Width                | 28 |

|      | Table 6-17 I-Cache Data Address Bit-Width            | 29 |

|      | Table 6-18 Data Cache Interface Signals              | 29 |

|      | Table 6-19 D-Cache Tag Address Bit-Width             | 30 |

|      | Table 6-20D-Cache Tag Data Bit-Width                 | 30 |

|      | Table 6-21D-Cache Data Address Bit-Width             | 31 |

| IPUC | G528-1.1E                                            | XX |

| Table 6-22 D-Cache Data Bit-Width                                         | 31 |

|---------------------------------------------------------------------------|----|

| Table 6-23 D-Cache Byte Write Enable Mapping                              | 32 |

| Table 6-24 AHB Slave Port Signals                                         | 32 |

| Table 6-25 BTB Memory Interface Signals                                   | 33 |

| Table 6-26 BTB RAM Address Bit-Width                                      | 33 |

| Table 8-1 Integer Registers                                               | 36 |

| Table 9-1 Normal Memory Attribute                                         | 39 |

| Table 9-2 Memory Access Ordering                                          | 40 |

| Table 10-1 Priorities for Instruction Fetches                             | 42 |

| Table 10-2 Priorities for Data Accesses                                   | 42 |

| Table 10-3 Local Memory Address Range (for ILM and DLM)                   | 43 |

| Table 10-4 Possible AHB-Lite Transactions Used by Local Memory Interfaces | 44 |

| Table 10-5 Instruction Local Memory Protection Control Signal             | 44 |

| Table 10-6 Data Local Memory Protection Control Signal                    | 44 |

| Table 11-1 Local Memory Slave Port Selection                              | 45 |

| Table 11-2 Local Memory Slave Port Transfer Latency                       | 46 |

| Table 12-1 Configuration Choices for the Instruction Cache                | 49 |

| Table 12-2 Configuration Choices for the Data Cache                       | 49 |

| Table 12-3 Access Latency of the Instruction Cache                        | 50 |

| Table 12-4 Access Latency of the Data Cache                               | 50 |

| Table 12-5 Effects of FENCE/FENCE.I Instructions                          | 51 |

| Table 13-1 AHB Transactions Used by BIU                                   | 53 |

| Table 17-1 Handling Correctable Errors in Caches                          | 62 |

| Table 17-2 Handling Uncorrectable Errors in Caches                        | 62 |

| Table 17-3 Local Memory Parity/ECC Error Handling                         | 62 |

| Table 17-4 Parity/ECC Behavior for Local Memory Operations                | 63 |

| Table 17-5 Types of Parity/ECC Error Exception                            | 63 |

| Table 18-1 Machine Information Registers                                  | 64 |

| Table 18-2 Machine Trap Related Registers                                 | 65 |

| Table 18-3 Counter Related Registers                                      | 65 |

| Table 18-4 Configuration Control & Status Registers                       | 66 |

| Table 18-5 Trigger Registers                                              | 66 |

| Table 18-6 Debug Registers                                                        | 66  |

|-----------------------------------------------------------------------------------|-----|

| Table 18-7 Memory and Miscellaneous Registers                                     | 67  |

| Table 18-8 Hardware Stack Protection and Recording Registers                      | 67  |

| Table 18-9 CoDense Registers                                                      | 67  |

| Table 18-10 PMP Registers                                                         | 68  |

| Table 18-11 RISC-V Definition of the Extensions Field                             | 73  |

| Table 18-12 Possible Values of mcause After Trap                                  | 80  |

| Table 18-13 Possible Values of mcause after Reset                                 | 80  |

| Table 18-14 Possible Values of mcause after NMI                                   | 80  |

| Table 18-15 Possible Values of mcause after Vector Interrupt                      | 80  |

| Table 18-16 Event Selectors                                                       | 85  |

| Table 18-17 Virtual Address in DPC upon Debug Mode Entry                          | 113 |

| Table 18-18 CCTL Command Definition                                               | 129 |

| Table 18-19 CCTL Commands Using the mcctldata Register                            | 130 |

| Table 18-20 User CCTL Command Definition                                          | 132 |

| Table 18-21 AE250 NAPOT range encoding in PMP address and configuration registers | 139 |

| Table 19-1 Load Instruction Latency                                               | 141 |

| Table 19-2 Multiply Instruction Latency: Radix Multiplier                         | 141 |

| Table 19-3 Multiply Instruction Latency: Fast Multiplier                          | 141 |

| Table 20-1 I/O Signal                                                             | 143 |

| Table 20-2 AE250 Memory Map                                                       | 146 |

| Table 20-3 AE250 Interrupt Assignment                                             | 148 |

| Table 20-4 PLIC Interrupt Source                                                  | 148 |

| Table 20-5 DMA Hardware Handshake ID                                              | 153 |

| Table 20-6 SMU Register Summary                                                   | 153 |

| Table 21-1 PLIC Configuration Parameters                                          | 165 |

| Table 21-2 AndeStar-V5 PLIC Memory Map                                            | 167 |

| Table 21-3 Meaning of Trigger Type                                                | 169 |

| Table 21-4 General Signals of NCEPLIC100                                          | 174 |

| Table 21-5 AHB Interface Signals of NCEPLIC100                                    | 174 |

| Table 22-1 NCEPLMT100 Memory Map                                                  | 176 |

|                                                                                   |     |

| Table 22-3 AHB Interface Signals of NCEPLMT100            | . 177 |

|-----------------------------------------------------------|-------|

| Table 23-1 System Memory Map of NCEPLDM200                | . 181 |

| Table 23-2 DMI Memory Map of NCEPLDM200                   | . 182 |

| Table 23-3 Use of Data Registers in PLDM                  | . 188 |

| Table 23-4 System Bus Address Register                    | . 194 |

| Table 23-5 System Bus Data Register                       | . 194 |

| Table 23-6 TAP Instruction NCEJDTM200                     | . 198 |

| Table 24-1 Signal Description of ATCWDT200                | 203   |

| Table 24-2 Summary of registers                           | 204   |

| Table 24-3 ID and Revision Register                       | 205   |

| Table 24-4 Control Register                               | 205   |

| Table 24-5 Restart Register                               | . 207 |

| Table 24-6 Write Enable Register                          | . 207 |

| Table 24-7 Status Register (0x1C)                         | 207   |

| Table 25-1 Signal Description of ATCRTC100                | . 212 |

| Table 25-2 Summary of Registers                           | . 213 |

| Table 25-3 ID and Revision Register                       | . 213 |

| Table 25-4 Counter Register                               | . 214 |

| Table 25-5 Alarm Register                                 | . 214 |

| Table 25-6 Control Register                               | . 215 |

| Table 25-7 Interrupt Status Register                      | . 216 |

| Table 25-8 Digital Trimming Register                      | . 217 |

| Table 25-9 Trimming Capabilities                          | . 222 |

| Table 26-1 Effective Devices of Channel Modes             | . 224 |

| Table 26-2 Signal Description of ATCPIT100                | . 225 |

| Table 26-3 Summary of registers                           | . 226 |

| Table 26-4 ID and Revision Register                       | . 227 |

| Table 26-5 Configuration Register                         | . 227 |

| Table 26-6 Interrupt Enable Register                      | . 228 |

| Table 26-7 Interrupt Status Register                      | . 229 |

| Table 26-8 Channel Enable Register                        | 230   |

| Table 26-9 Channel 0~3 Control Register (0x20 + n * 0x10) | . 231 |

| Table 26-10 Reload Register for 32-bit Timer Mode (ChMode=1)                               | . 232 |

|--------------------------------------------------------------------------------------------|-------|

| Table 26-11 Reload Register for 16-bit Timers Mode (ChMode=2)                              | . 232 |

| Table 26-12 Reload Register for 8-bit Timers Mode (ChMode=3)                               | . 233 |

| Table 26-13 Reload Register for PWM Mode (ChMode=4)                                        | . 233 |

| Table 26-14 Reload Register for Mixed PWM/16-bit Timer Mode (ChMode=6)                     | . 233 |

| Table 26-15 Reload Register for Mixed PWM/8-bit Timers Mode (ChMode=7)                     | . 233 |

| Table 27-1 ATCBUSDEC200 Signal Description                                                 | . 239 |

| Table 27-2 Register Summary                                                                | . 239 |

| Table 27-3 ID and Revision Register (0x00)                                                 | . 240 |

| Table 27-4 Base/Size Register of Downstream Port 1~n (0x1c + n*0x4) in 24-bit Address Mode | . 240 |

| Table 27-5 Base/Size Register of Downstream Port 1~n (0x1c + n*0x4) in 32-bit Address Mode | . 241 |

| Table 27-6 ATCBUSDEC200 Access Latencies                                                   | . 244 |

| Table 28-1 Programmability of Base Address and Size Registers for AHB Slave 1–15           | . 247 |

| Table 28-2 ATCBMC200 Signal Definition                                                     | . 249 |

| Table 28-3 ATCBMC200 Register Summary                                                      | . 250 |

| Table 28-4 ID and Revision Register                                                        | . 251 |

| Table 28-5 Priority Register                                                               | . 252 |

| Table 28-6 Control Register                                                                | . 252 |

| Table 28-7 Interrupt Status Register                                                       | . 253 |

| Table 28-8 Base/Size Register of AHB Slave 1–10 in 24-bit Mode                             | . 255 |

| Table 28-9 Base/Size Register of AHB Slave 1–10 in 32-bit Mode                             | . 255 |

| Table 28-10 Base/Size Register of AHB Slave 11–15 in 24-bit Mode                           | . 256 |

| Table 28-11 Base/Size Register of AHB Slave 11–15 in 32-bit Mode                           | . 256 |

| Table 28-12 Slave Sizes Encoding Table                                                     | . 259 |

| Table 29-1 ATCAPBBRG100 Signal Definition                                                  | . 263 |

| Table 29-2 ATCAPBBRG100 Register Summary                                                   | . 265 |

| Table 29-3 ID and Revision Register                                                        | . 265 |

| Table 29-4 Configuration Register                                                          | . 266 |

| Table 29-5 Base/Size Register of Slave 1~n in 24-bit mode                                  | . 267 |

| Table 29-6 Base/Size Register of Slave 1~n in 32-bit mode                                  | . 268 |

| Table 29-7 ATCAPBBRG100 Access Latencies                                                   | . 270 |

| Table 30-1 ATCAPRDEC100 Signal Definition                                                  | 273   |

IPUG528-1.1E xxiv

| Table 30-2 ATCAPBDEC100 Register Summary                              | 274   |

|-----------------------------------------------------------------------|-------|

| Table 30-3 ID and Revision Register                                   | 274   |

| Table 30-4 Base/Size Register of Slave 1~n in the 24-bit Mode         | 275   |

| Table 30-5 Base/Size Register of Slave 1~n in the 32-bit Mode         | 276   |

| Table 31-1 Format of Linked List Descriptor                           | 282   |

| Table 31-2 ATCDMAC100 Signal Definition                               | 285   |

| Table 31-3 ATCDMAC100 Register Summary                                | 287   |

| Table 31-4 ID and Revision Register                                   | . 288 |

| Table 31-5 DMAC Configuration Register                                | 288   |

| Table 31-6 DMAC Control Register                                      | . 289 |

| Table 31-7 Interrupt Status Register                                  | 289   |

| Table 31-8 Channel Enable Register                                    | 290   |

| Table 31-9 Channel Abort Register                                     | 290   |

| Table 31-10 Channel n Control Register                                | . 291 |