# Gowin\_EMPU\_M1 硬件设计 参考手册

IPUG531-1.5,2020-03-03

#### 版权所有© 2020 广东高云半导体科技股份有限公司

未经本公司书面许可,任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部,并不得以任何形式传播。

#### 免责声明

本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止发言或其它方式授予任何知识产权许可。除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。高云半导体不承诺对这些文档进行适时的更新。

# 版本信息

| 日期         | 版本  | 说明                                                                                                                                                                                                             |  |  |  |  |  |

|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 2019/02/19 | 1.0 | 初始版本。                                                                                                                                                                                                          |  |  |  |  |  |

| 2019/07/18 | 1.1 | MCU 硬件设计支持扩展外部设备 CAN、Ethernet、SPI-Flash、RTC、DualTimer、TRNG、I2C、SPI、SD-Card。                                                                                                                                    |  |  |  |  |  |

| 2019/08/18 | 1.2 | <ul> <li>MCU 硬件设计与软件编程设计支持扩展外部设备 DDR3 Memory;</li> <li>修复已知 ITCM、DTCM Size 和 IDE 问题。</li> </ul>                                                                                                                |  |  |  |  |  |

| 2019/09/27 | 1.3 | <ul> <li>MCU硬件设计与软件编程设计支持外部设备 SPI-Flash 的读、写和擦除功能;</li> <li>MCU 软件编程设计支持外部设备 I2C 一次连续多字节读、写功能;</li> <li>修复已知 MCU 软件编程设计中 AHB2 扩展接口和 APB2 扩展接口地址映射问题;</li> <li>修复已知 MCU 软件编程设计中 DDR3 Memory 连续读、写问题。</li> </ul> |  |  |  |  |  |

| 2019/12/06 | 1.4 | ● MCU 硬件设计与软件编程设计支持外部设备 PSRAM;<br>● 更新 MCU 编译软件 GMD V1.0;<br>● 更新 RTOS 参考设计;<br>● 增加 AHB2 和 APB2 扩展总线接口硬件和软件参考设计。                                                                                              |  |  |  |  |  |

| 2020/03/03 | 1.5 | <ul> <li>MCU 硬件设计支持外部设备 SD-Card 的读、写功能;</li> <li>修复已知 synplify Pro 综合时,外部设备 DDR3 的数据读、写问题;</li> <li>支持 FPGA 器件 GW2A-18C/GW2AR-18C/GW2A-55C。</li> </ul>                                                         |  |  |  |  |  |

i

# 目录

| 目 | 录                             | i   |

|---|-------------------------------|-----|

| 图 | 目录                            | iii |

| 表 | 目录                            | . v |

| 1 | 硬件架构                          | .1  |

|   | 1.1 系统架构                      | 1   |

|   | 1.2 系统特征                      | 2   |

|   | 1.2.1 Cortex-M1 子系统           | 2   |

|   | 1.2.2 AHB-Lite Extension 子系统  | 3   |

|   | 1.3 系统端口                      | 3   |

|   | 1.3.1 Cortex-M1 端口            | 3   |

|   | 1.3.2 AHB-Lite Extension 端口   | 5   |

|   | 1.4 系统资源统计                    | 8   |

| 2 | 硬件设计流程                        | . 9 |

|   | 2.1 硬件环境                      | 9   |

|   | 2.2 软件环境                      | 9   |

|   | 2.3 软核生成器                     | 9   |

|   | 2.4 下载软件                      | 9   |

|   | 2.5 设计流程                      | 9   |

| 3 | 工程模板                          | 11  |

|   | 3.1 工程创建                      | 11  |

|   | 3.1.1 新建工程                    | 11  |

|   | 3.1.2 设定工程名称和路径               | 11  |

|   | 3.1.3 选择器件                    | 12  |

|   | 3.1.4 完成工程创建                  | 12  |

|   | 3.2 硬件设计                      | 13  |

|   | 3.2.1 Cortex-M1 硬件设计          | 14  |

|   | 3.2.2 AHB-Lite Extension 硬件设计 | 19  |

|   | 3.3 用户设计                      | 37  |

| 1 | <u> </u>                  | 42   |

|---|---------------------------|------|

|   | 3.8 下载                    | . 40 |

|   | 3.7 布局布线                  | . 40 |

|   | 3.6 综合                    | . 39 |

|   | 3.5.3 Dual-Purpose Pin 配置 | . 39 |

|   | 3.5.2 Post-Place File 配置  | . 38 |

|   | 3.5.1 项层模块配置              | . 37 |

|   | 3.5 配置                    | . 37 |

|   | 3.4 约束                    | . 37 |

# 图目录

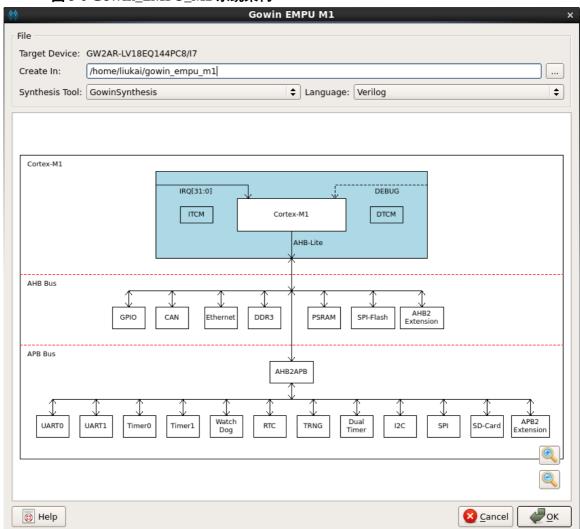

| 图 1-1 Gowin_EMPU_M1 系统架构 | . 1  |

|--------------------------|------|

| 图 3-1 新建 FPGA Design 工程  | . 11 |

| 图 3-2 设定工程名称和路径          | . 12 |

| 图 3-3 选择器件               | . 12 |

| 图 3-4 完成工程创建             | . 13 |

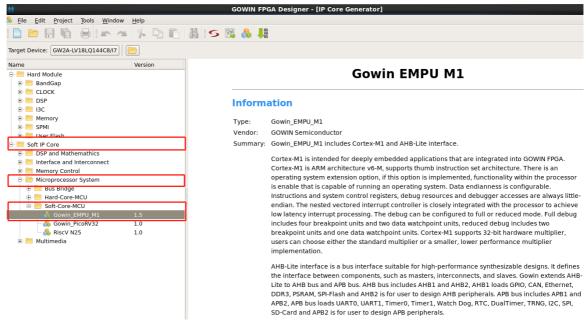

| 图 3-5 选择 Gowin_EMPU_M1   | . 13 |

| 图 3-6 Gowin_EMPU_M1 系统架构 | . 14 |

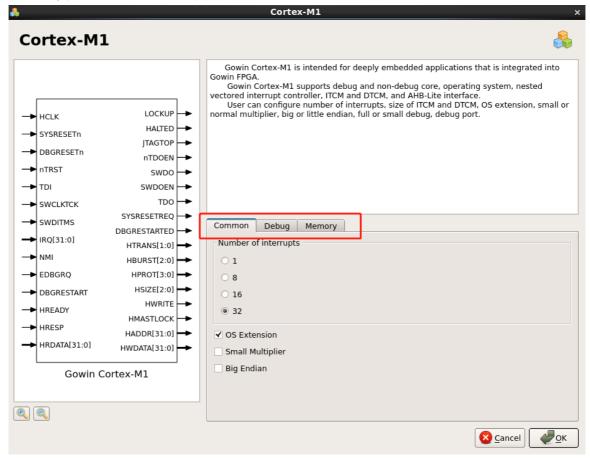

| 图 3-7 Cortex-M1 配置页面     | . 15 |

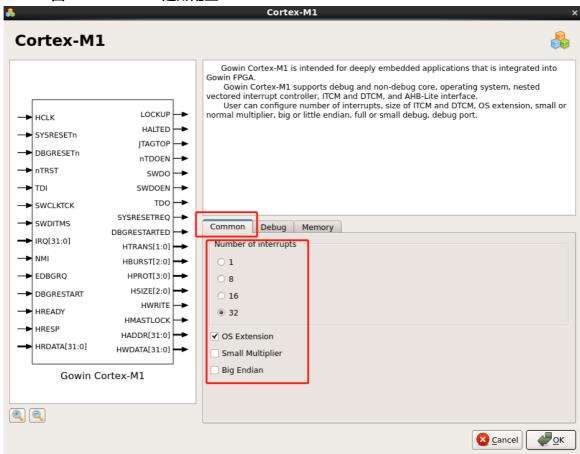

| 图 3-8 Cortex-M1 通用配置     | . 16 |

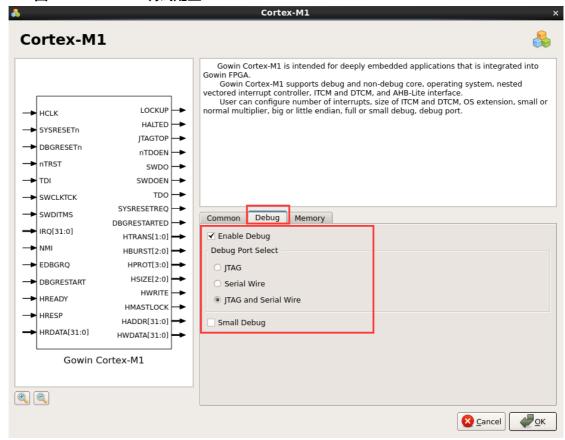

| 图 3-9 Cortex-M1 调试配置     | . 17 |

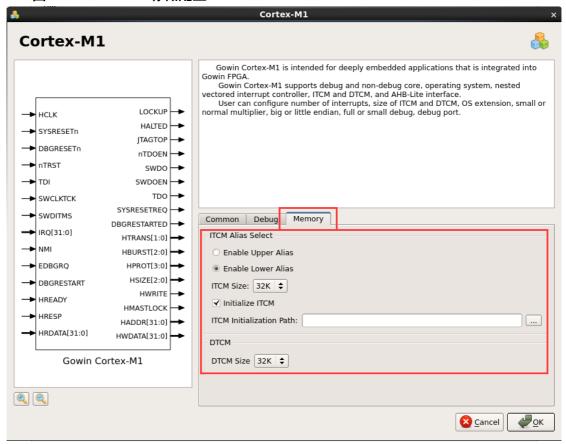

| 图 3-10 Cortex-M1 存储配置    | . 18 |

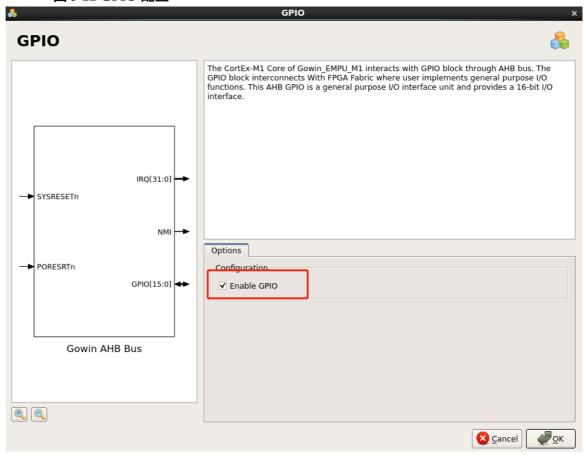

| 图 3-11 GPIO 配置           | . 20 |

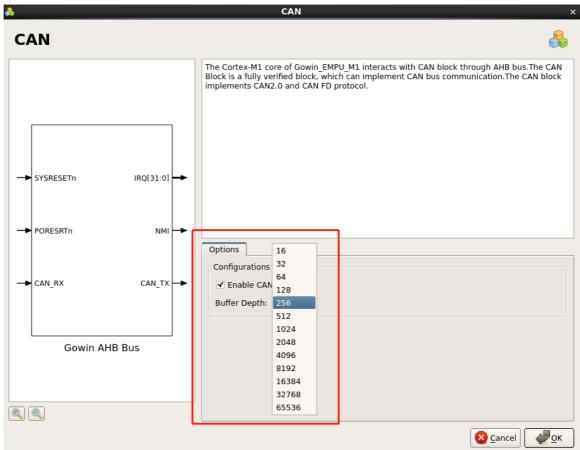

| 图 3-12 CAN 配置            | . 21 |

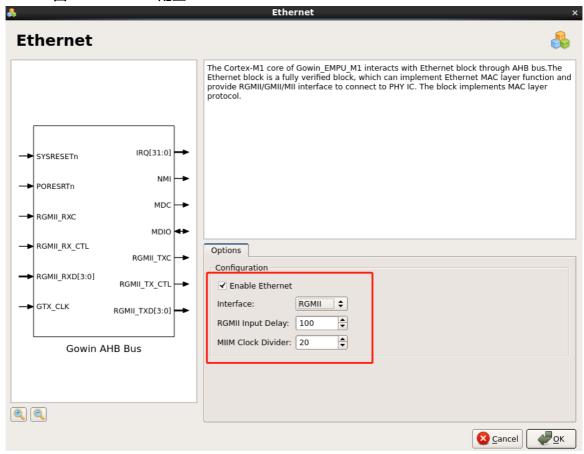

| 图 3-13 Ethernet 配置       | . 22 |

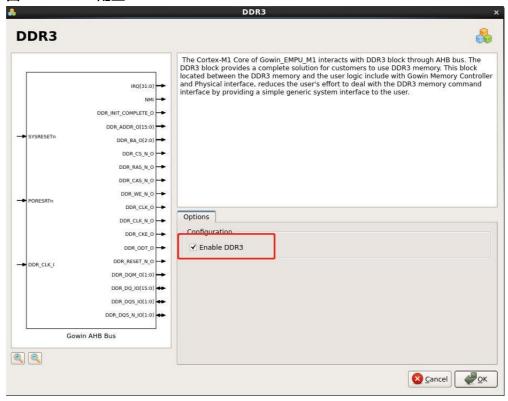

| 图 3-14 DDR3 配置           | . 23 |

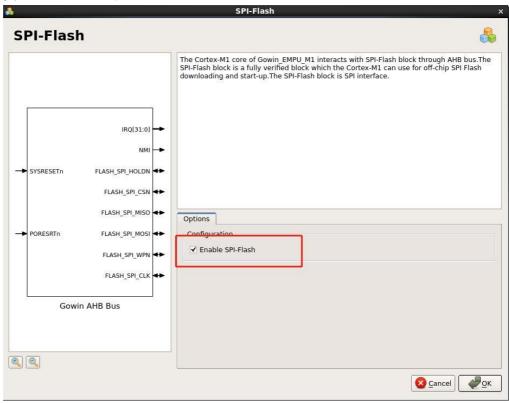

| 图 3-15 SPI-Flash 配置      | . 24 |

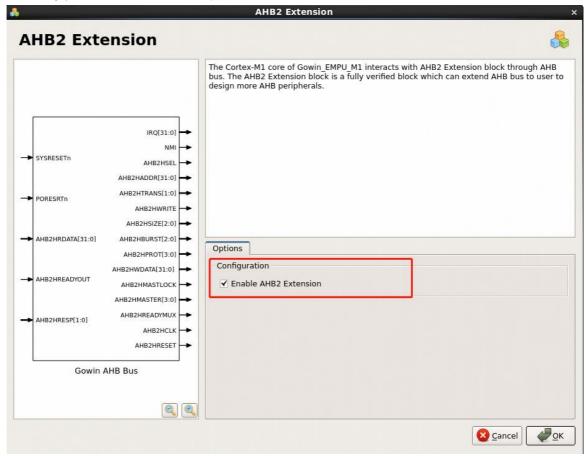

| 图 3-16 AHB2 Extension 配置 | . 25 |

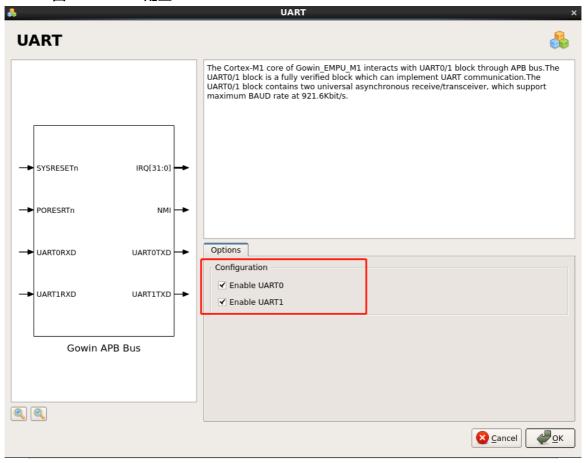

| 图 3-17 UART 配置           | . 26 |

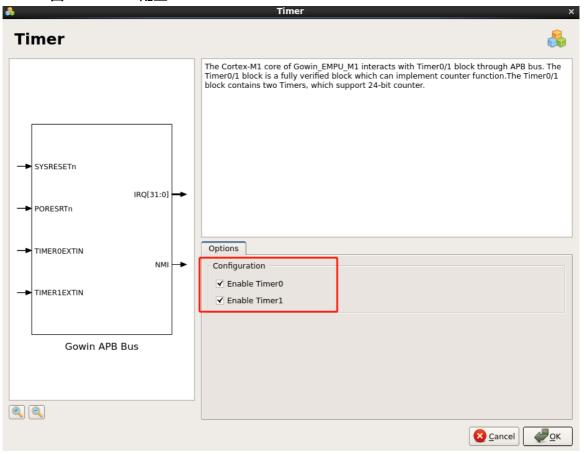

| 图 3-18 Timer 配置          | . 27 |

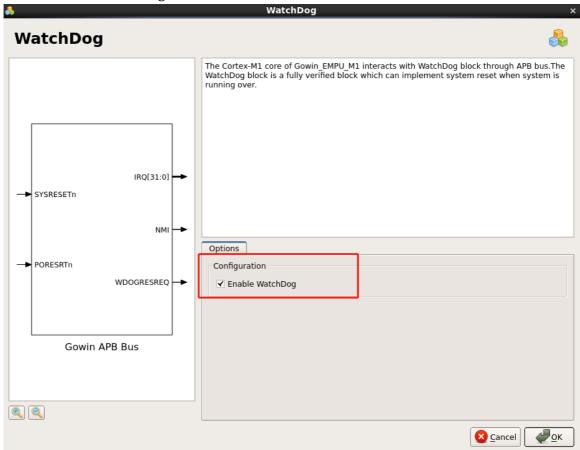

| 图 3-19 WatchDog 配置       | . 28 |

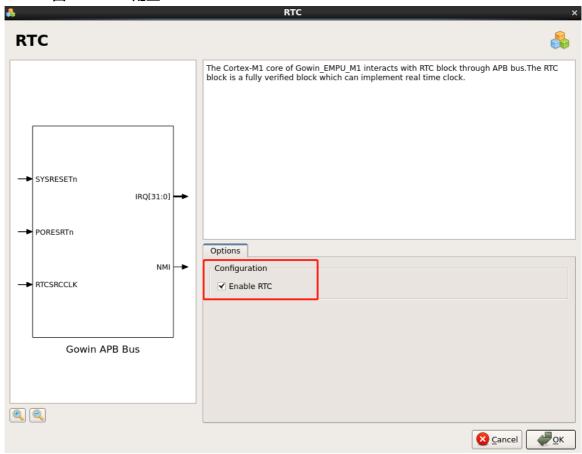

| 图 3-20 RTC 配置            | . 29 |

| 图 3-21 DualTimer 配置      | . 30 |

| 图 3-22 TRNG 配置           | . 31 |

| 图 3-23 I2C 配置            | . 32 |

| 图 3-24 SPI 配置            | . 33 |

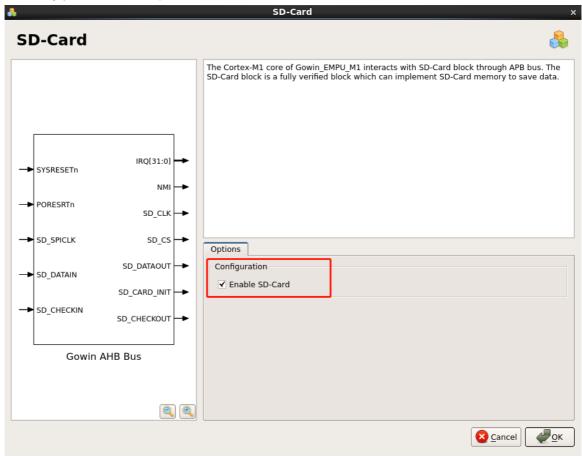

| 图 3-25 SD-Card 配置        | . 34 |

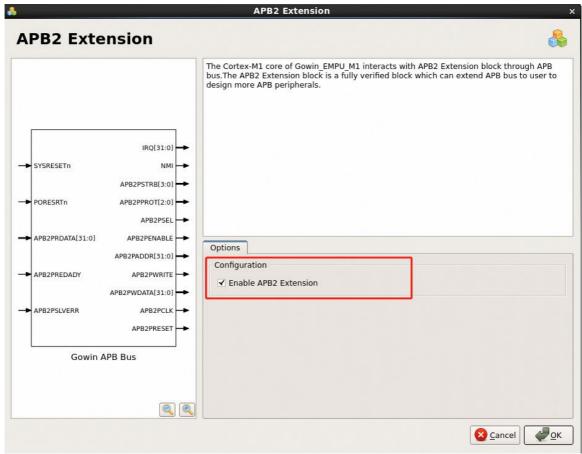

| 图 3-26 APB2 Extension 配置 | . 35 |

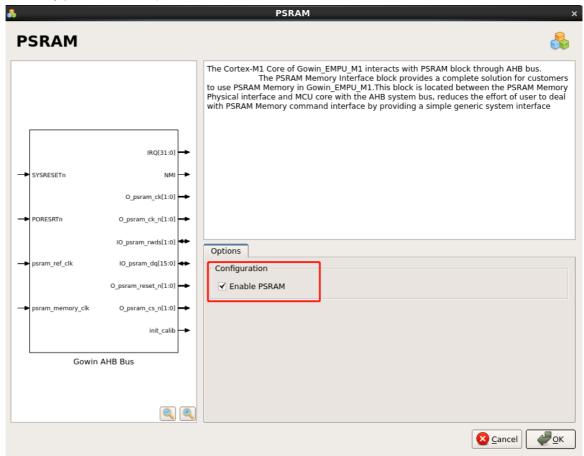

| 图 3-27 PSRAM 配置          | . 36 |

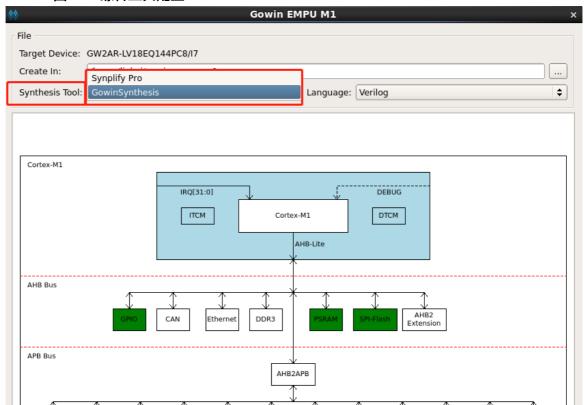

| 图 3-28 综合工具配置            | . 37 |

| 图 | 3-29 J | 项层模块配置                   | 38 |

|---|--------|--------------------------|----|

| 图 | 3-30 F | Post-Place File 配置3      | 38 |

| 图 | 3-31 [ | Dual-Purpose Pin 配置      | 39 |

| 图 | 3-32 🗐 | 综合                       | 39 |

| 图 | 3-33 F | Place & Route            | 10 |

| 图 | 3-34 ( | GW1N 系列 Configure Device | 11 |

| 夂 | 3-35 ( | GW2A 系列 Configure Device | 11 |

# 表目录

| 表 1-1 Cortex-M1 端口            | 3  |

|-------------------------------|----|

| 表 1-2 AHB-Lite Extension 端口   | 5  |

| 表 1-3 Gowin_EMPU_M1 系统资源统计    | 8  |

| 表 3-1 Cortex-M1 配置选项          | 14 |

| 表 3-2 AHB-Lite Extension 配置选项 | 19 |

IPUG531-1.5 v

# 1 硬件架构

# 1.1 系统架构

Gowin\_EMPU\_M1 包括三级结构,如图 1-1 所示。

Cortex-M1 DEBUG IRQ[31:0] ITCM Cortex-M1 DTCM AHB-Lite AHB Bus AHB2 GPI0 Ethernet CAN DDR3 **PSRAM**  ${\tt SPI-Flash}$ Extension APB Bus AHB2APB APB2 **UARTO** UART1 Timer0 Timer1 WatchDog RTC TRNG DualTimer I2C SD-Card Extension

图 1-1 Gowin\_EMPU\_M1 系统架构

第一级,Cortex-M1及ITCM、DTCM。

第二级, AHB 总线及 GPIO、CAN、Ethernet、DDR3 Memory、PSRAM、SPI-Flash、AHB2 Extension Bus。

第三级, APB 总线及 UART0、UART1、Timer0、Timer1、Watch Dog、

IPUG531-1.5 1(42)

1 硬件架构 1.2 系统特征

RTC、TRNG、DualTimer、I2C、SPI、SD-Card、APB2 Extension Bus。

# 1.2 系统特征

Gowin\_EMPU\_M1 包括两个子系统:

- Cortex-M1 内核子系统:

- AHB-Lite 扩展 AHB 总线和 APB 总线,及外设接口子系统。

#### 1.2.1 Cortex-M1 子系统

#### 处理器内核

- ARM architecture v6-M Thumb 指令集架构,支持 16-bit Thumb 和 32-bit Thumb2 指令集:

- 可配置扩展操作系统;

- 系统异常处理;

- 中断异常处理和正常线程模式;

- 栈指针,正常是一个栈指针,扩展操作系统时两个栈指针;

- 大小端格式。

- 可配置数据大小端格式

- 指令和系统控制寄存器小端格式

- 调试系统小端格式

#### **NVIC**

- 可配置外部中断数量,1、8、16、32;

- 4 个优先级等级;

- 进入中断处理时自动保存处理器状态,中断处理结束时自动恢复状态。

#### 调试系统

通过配置选项控制调试系统开关。

- 如果关闭调试系统,则 Cortex-M1 内核不支持调试系统

- 如果打开调试系统,则 Cortex-M1 内核支持调试系统

- 可配置完整(full)模式和简化(reduced)模式

- 完整模式: 4 个 BreakPoint Unit 和 2 个 Data Watchpoint;

- 简化模式: 2 个 BreakPoint Unit 和 1 个 Data Watchpoint;

- 可配置 DAP 端口

- JTAG/SW

- JTAG

- SW

IPUG531-1.5 2(42)

1.3 系统端口

#### Memory

● ITCM: 指令存储器,可配置大小,Upper 或 Lower alias 方式和读入初始值;

● DTCM:数据存储器,可配置大小。

#### 32 位硬件乘法器

- Normal 模式

- Small 模式

### 1.2.2 AHB-Lite Extension 子系统

- AHB 总线,及GPIO、CAN、Ethernet、DDR3 Memory、PSRAM、SPI-Flash、AHB2 Extension;

- APB 总线,及 UART0、UART1、Timer0、Timer1、Watch Dog、RTC、DualTimer、TRNG、I2C、SPI、SD-Card、APB2 Extension。

# 1.3 系统端口

### 1.3.1 Cortex-M1 端口

Cortex-M1 端口如表 1-1 所示。

表 1-1 Cortex-M1 端口

| 名称           | I/O | 位宽     | 描述                              |

|--------------|-----|--------|---------------------------------|

| HCLK         | in  | 1      | System clock                    |

| SYSRESETn    | in  | 1      | System reset                    |

| DBGRESETn    | in  | 1      | Power on debug reset            |

| LOCKUP       | out | 1      | Core is in lockup state         |

| HALTED       | out | 1      | Core is in Halt debug state     |

| nTRST        | in  | 1      | JTAG reset                      |

| SWCLKTCK     | in  | 1      | Serial wire and JTAG clock      |

| SWDITMS      | in  | 1      | SW Data / JTAG Test Mode Select |

| TDI          | in  | 1      | JTAG data input                 |

| JTAGNSW      | out | 1      | JTAG = 1, serial wire = 0       |

| JTAGTOP      | out | 1      | State controller indicator      |

| TDO          | out | 1      | JTAG data output                |

| nTDOEN       | out | 1      | JTAG data out enable            |

| SWDO         | out | 1      | Serial wire data out            |

| SWDOEN       | out | 1      | Serial data output enable       |

| IRQ          | in  | [31:0] | External interrupts             |

| NMI          | in  | 1      | Non-maskable interrupt          |

| SYSRESETREQ  | out | 1      | System reset require            |

| EDBGRQ       | in  | 1      | External debug request          |

| DBGRESTART   | in  | 1      | Restart from halt request       |

| DBGRESTARTED | out | 1      | Restart from halt acknowledge   |

| HREADY       | in  | 1      | Slave ready signal              |

| HRESP        | in  | 1      | Slave response signal           |

| HRDATA       | in  | [31:0] | Data from slave to master       |

| HTRANS       | out | [1:0]  | Transfer type                   |

| HBURST       | out | [2:0]  | Burst type                      |

| HPROT        | out | [3:0]  | Transfer protection bits        |

IPUG531-1.5 3(42)

| HSIZE     | out | [2:0]  | Transfer size                 |

|-----------|-----|--------|-------------------------------|

| HWRITE    | out | 1      | Transfer direction            |

| HMASTLOCK | out | 1      | Transfer is a locked transfer |

| HADDR     | out | [31:0] | Transfer address              |

| HWDATA    | out | [31:0] | Data from master to slave     |

IPUG531-1.5 4(42)

# 1.3.2 AHB-Lite Extension 端口

AHB-Lite Extension 端口如表 1-2 所示。

表 1-2 AHB-Lite Extension 端口

| 名称           | I/O   | 位宽     | 描述                | 所属模块                     |

|--------------|-------|--------|-------------------|--------------------------|

| SYSRESETn    | in    | 1      | 系统复位              | -                        |

| PORESETn     | in    | 1      | 上电复位              | -                        |

| IRQ          | out   | [31:0] | 外部中断              | -                        |

| NMI          | out   | 1      | Non-Maskable 中断   | -                        |

| GPIO         | inout | [15:0] | 通用输入输出端口          | GPIO                     |

| UART0RXD     | in    | 1      | UART0 接收端口        | UART0                    |

| UART0TXD     | out   | 1      | UART0 发送端口        | UARTO                    |

| UART1RXD     | int   | 1      | UART1 接收端口        | UART1                    |

| UART1TXD     | out   | 1      | UART1 发送端口        | UARTI                    |

| TIMER0EXTIN  | in    | 1      | Timer0 外部中断       | Timer0                   |

| TIMER1EXTIN  | in    | 1      | Timer1 外部中断       | Timer1                   |

| WDOGRESREQ   | out   | 1      | Watch Dog 复位请求    | Watch Dog                |

| RTCSRCCLK    | in    | 1      | RTC 时钟源 32.768KHz | RTC                      |

| SCL          | inout | 1      | 串行时钟              | I2C                      |

| SDA          | inout | 1      | 串行数据              | 120                      |

| MOSI         | out   | 1      | 主设备输出/从设备输入       |                          |

| MISO         | in    | 1      | 主设备输入/从设备输出       | SPI                      |

| SCLK         | out   | 1      | 时钟信号              | SFI                      |

| NSS          | out   | 1      | 从设备选择信号           |                          |

| SD_SPICLK    | in    | 1      | SPI 时钟信号          |                          |

| SD_CLK       | out   | 1      | SD 时钟信号           |                          |

| SD_CS        | out   | 1      | 片选信号              |                          |

| SD_DATAIN    | in    | 1      | 数据输入              | SD-Card                  |

| SD_DATAOUT   | out   | 1      | 数据输出              | SD-Calu                  |

| SD_CARD_INIT | out   | 1      | 初始化"0"            |                          |

| SD_CHECKIN   | in    | 1      | 输入检查              |                          |

| SD_CHECKOUT  | out   | 1      | 输出检查              |                          |

| CAN_RX       | in    | 1      | 数据输入              | CAN                      |

| CAN_TX       | out   | 1      | 数据输出              | CAN                      |

| RGMII_TXC    | out   | 1      | RGMII 发送时钟        |                          |

| RGMII_TX_CTL | out   | 1      | RGMII 发送控制        | Ethernet RGMII Interface |

| RGMII_TXD    | out   | [3:0]  | RGMII 发送数据        |                          |

| RGMII_RXC    | in    | 1      | RGMII 接收时钟        |                          |

| RGMII_RX_CTL | in    | 10     | RGMII 接收控制        |                          |

IPUG531-1.5 5(42)

| 名称                  | I/O   | 位宽     | 描述                      | 所属模块                    |

|---------------------|-------|--------|-------------------------|-------------------------|

| RGMII_RXD           | in    | [3:0]  | RGMII 接收数据              |                         |

| GTX_CLK             | in    | 1      | RGMII 125MHz 时钟输<br>入   |                         |

| GMII_RX_CLK         | in    | 1      | GMII 接收时钟               |                         |

| GMII_RX_DV          | in    | 1      | GMII 接收使能               |                         |

| GMII_RXD            | in    | [7:0]  | GMII 接收数据               |                         |

| GMII_RX_ER          | in    | 1      | GMII 接收错误               |                         |

| GTX_CLK             | in    | 1      | GMII 125MHz 时钟输入        | Ethernet GMII Interface |

| GMII_GTX_CLK        | out   | 1      | GMII 发送时钟               |                         |

| GMII_TXD            | out   | [7:0]  | GMII 发送数据               |                         |

| GMII_TX_EN          | out   | 1      | GMII 发送使能               |                         |

| GMII_TX_ER          | out   | 1      | GMII 发送错误               |                         |

| MII_RX_CLK          | in    | 1      | MII 接收时钟                |                         |

| MII_RXD             | in    | [3:0]  | MII 接收数据                |                         |

| MII_RX_DV           | in    | 1      | MII 接收使能                |                         |

| MII_RX_ER           | in    | 1      | MII 接收错误                |                         |

| MII_TX_CLK          | in    | 1      | MII 发送时钟                | The area of Mill before |

| MII_TXD             | out   | [3:0]  | MII 发送数据                | Ethernet MII Interface  |

| MII_TX_EN           | out   | 1      | MII 发送使能                |                         |

| MII_TX_ER           | out   | 1      | MII 发送错误                |                         |

| MII_COL             | in    | 1      | MII 冲突信号                |                         |

| MII_CRS             | in    | 1      | MII 载波信号                |                         |

| MDC                 | out   | 1      | 管理通道时钟                  | Eth a mark              |

| MDIO                | inout | 1      | 管理通道数据                  | Ethernet                |

| DDR_CLK_I           | in    | 1      | 50MHz 时钟输入              |                         |

| DDR_INIT_COMPLETE_O | out   | 1      | 初始化完成信号                 |                         |

| DDR_ADDR_O          | out   | [15:0] | Row 地址、Column 地址        |                         |

| DDR_BA_O            | out   | [2:0]  | Bank 地址                 |                         |

| DDR_CS_N_O          | out   | 1      | 片选信号                    |                         |

| DDR_RAS_N_O         | out   | 1      | Row 地址选通信号              |                         |

| DDR_CAS_N_O         | out   | 1      | Column 地址选通信号           |                         |

| DDR_WE_N_O          | out   | 1      | Row 写使能                 | DDR3                    |

| DDR_CLK_O           | out   | 1      | 提供给 DDR3 SDRAM<br>的时钟信号 |                         |

| DDR_CLK_N_O         | out   | 1      | 与 DDR_CLK_O 组成差<br>分信号  |                         |

| DDR_CKE_O           | out   | 1      | DDR3 SDRAM 时钟使<br>能信号   |                         |

| DDR_ODT_O           | out   | 1      | 内存信号端接电阻控制              |                         |

| DDR_RESET_N_O       | out   | 1      | DDR3 SDRAM 复位信          |                         |

IPUG531-1.5 6(42)

| 名称               | I/O   | 位宽     | 描述                                                 | 所属模块           |

|------------------|-------|--------|----------------------------------------------------|----------------|

|                  |       |        | 号                                                  |                |

| DDR DQM O        | out   | [1:0]  | DDR3 SDRAM 数据屏                                     |                |

| DDR_DQ_IO        | inout | [15:0] | 蔽信号<br>DDR3 SDRAM 数据                               |                |

|                  | _     |        | DDR3 SDRAM 数据选                                     |                |

| DDR_DQS_IO       | inout | [1:0]  | 通信号                                                |                |

| DDR_DQS_N_IO     | inout | [1:0]  | 与 DDR_DQS_IO 组成<br>差分信号                            |                |

| O_psram_ck       | out   | [1:0]  | 提供给 PSRAM 的时钟<br>信号                                |                |

| O_psram_ck_n     | out   | [1:0]  | 与 <b>O_</b> psram_ck 组成差<br>分信号                    |                |

| IO_psram_rwds    | inout | [1:0]  | PSRAM 数据选通信号<br>及掩码信号                              |                |

| IO_psram_dq      | inout | [15:0] | PSRAM 数据                                           |                |

| O_psram_reset_n  | out   | [1:0]  | PSRAM 复位信号                                         | PSRAM          |

| O_psram_cs_n     | out   | [1:0]  | 片选,低有效                                             | 1 Old twi      |

| init_calib       | out   | 1      | 初始化完成信号                                            |                |

| psram_ref_clk    | in    | 1      | 参考输入时钟,一般为板<br>载晶振时钟                               |                |

| psram_memory_clk | in    | 1      | 用户输入颗粒工作时钟,<br>一般为 PLL 倍频出来的<br>高速时钟,也可以不使用<br>PLL |                |

| FLASH_SPI_HOLDN  | inout | 1      | NC                                                 |                |

| FLASH_SPI_CSN    | inout | 1      | 从设备选择信号                                            |                |

| FLASH_SPI_MISO   | inout | 1      | 主设备输入/从设备输出                                        | SPI-Flash      |

| FLASH_SPI_MOSI   | inout | 1      | 主设备输出/从设备输入                                        | Of 1-1 lasti   |

| FLASH_SPI_WPN    | inout | 1      | NC                                                 |                |

| FLASH_SPI_CLK    | inout | 1      | 时钟信号                                               |                |

| APB2PSTRB        | out   | [3:0]  | APB2 PSTRB                                         |                |

| APB2PPROT        | out   | [2:0]  | APB2 PPROT                                         |                |

| APB2PSEL         | out   | 1      | APB2 PSEL                                          |                |

| APB2PENABLE      | out   | 1      | APB2 PENABLE                                       |                |

| APB2PADDR        | out   | [31:0] | APB2 PADDR                                         |                |

| APB2PWRITE       | out   | 1      | APB2 PWRITE                                        | ADD2 Extension |

| APB2PWDATA       | out   | [31:0] | APB2 PWDATA                                        | APB2 Extension |

| APB2PRDATA       | in    | [31:0] | APB2 PRDATA                                        |                |

| APB2PREADY       | in    | 1      | APB2 PREADY                                        |                |

| APB2PSLVERR      | in    | 1      | APB2 PSLVERR                                       |                |

| APB2PCLK         | out   | 1      | APB2 PCLK                                          |                |

| APB2PRESET       | out   | 1      | APB2 RESET                                         |                |

IPUG531-1.5 7(42)

1.4 系统资源统计

| 名称            | I/O | 位宽     | 描述             | 所属模块             |

|---------------|-----|--------|----------------|------------------|

| AHB2HSEL      | out | 1      | AHB2 HSEL      |                  |

| AHB2HADDR     | out | [31:0] | AHB2 HADDR     |                  |

| AHB2HTRANS    | out | [1:0]  | AHB2 HTRANS    |                  |

| AHB2HWRITE    | out | 1      | AHB2 HWRITE    |                  |

| AHB2HSIZE     | out | [2:0]  | AHB2 HSIZE     |                  |

| AHB2HBURST    | out | [2:0]  | AHB2 HBURST    |                  |

| AHB2HPROT     | out | [3:0]  | AHB2 HPROT     |                  |

| AHB2HWDATA    | out | [31:0] | AHB2 HWDATA    | - AHB2 Extension |

| AHB2HMASTLOCK | out | 1      | AHB2 HMASTLOCK |                  |

| AHB2HREADYMUX | out | 1      | AHB2 HREADYMUX |                  |

| AHB2HRDATA    | in  | [31:0] | AHB2 HRDATA    |                  |

| AHB2HREADYOUT | in  | 1      | AHB2 HREDAYOUT |                  |

| AHB2HRESP     | in  | [1:0]  | AHB2 HRESP     |                  |

| AHB2HMASTER   | out | [3:0]  | AHB2 MASTER    |                  |

| AHB2HCLK      | out | 1      | AHB2 HCLK      |                  |

| AHB2HRESET    | out | 1      | AHB2 RESET     |                  |

# 1.4 系统资源统计

Gowin\_EMPU\_M1 系统资源统计,如表 1-3 所示。

表 1-3 Gowin\_EMPU\_M1 系统资源统计

| Resources Configuration                                      | LUTs  | Registers | BSRAMs | DSP<br>Macros |

|--------------------------------------------------------------|-------|-----------|--------|---------------|

| Cortex-M1 Minimum and No Peripherals                         | 2478  | 813       | 8      | 0             |

| Cortex-M1 Default and No Peripherals                         | 5211  | 2324      | 32     | 2             |

| Cortex-M1 Default and Peripherals (GPIO/UART/Timer/WatchDog) | 6936  | 3108      | 32     | 2             |

| Cortex-M1 Default and All Peripherals                        | 21214 | 13002     | 48     | 2             |

IPUG531-1.5 8(42)

2.1 硬件设计流程 2.1 硬件环境

# 2硬件设计流程

# 2.1 硬件环境

- DK-START-GW2A18 V2.0

GW2A-LV18PG256C8/I7

- DK-START-GW1N9 V1.1 GW1N-LV9LQ144C6/I5

- DK-START-GW2A55 V1.3 GW2A-LV55PG484C8/I7

- DK-START-GW2AR18 V1.1 GW2AR-LV18ELQ144PC6/I5

# 2.2 软件环境

Gowin V1.9.5 Beta 及以上版本。

# 2.3 软核生成器

Gowin 云源软件提供软核生成器 IP Core Generator,用于配置和产生Cortex-M1 和 AHB-Lite Extension 硬件设计。

IP Core Generator 软件使用方法请参考 <u>SUG284</u>, Gowin IP Core Generator 用户指南。

# 2.4 下载软件

Gowin\_EMPU\_M1 支持 Programmer 软件下载码流文件。

Programmer 软件使用方法请参考 <u>SUG502</u>,Gowin Programmer 用户指南。

# 2.5 设计流程

Gowin EMPU M1 硬件设计流程:

1. IP Core Generator 软核生成器配置 Cortex-M1、APB Bus Peripherals 和 AHB Bus Peripherals,产生 Gowin\_EMPU\_M1 硬件设计,导入工程;

IPUG531-1.5 9(42)

2.5 设计流程

2. 实例化 Gowin\_EMPU\_M1,导入用户设计,连接用户设计与Gowin\_EMPU\_M1;

- 3. 物理约束和时序约束;

- 4. Synplify\_Pro 或 GowinSynthesis 综合;

- 5. Place & Route 布局布线,产生码流文件;

- 6. Programmer 下载码流到 GW1N-9/GW1NR-9/GW2A-18/GW2A-18C/GW2AR-18/GW2AR-18C/GW2A-55/GW2A-55C。

IPUG531-1.5 10(42)

**3** 工程模板 **3.1** 工程创建

# **3**工程模板

# 3.1 工程创建

# 3.1.1 新建工程

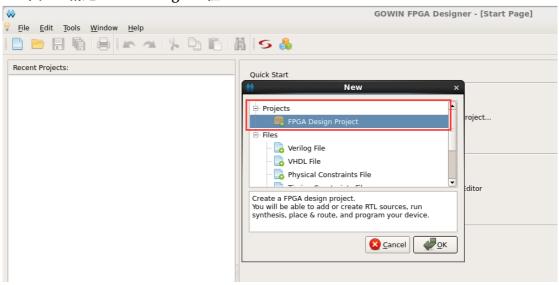

双击 "GOWIN FPGA Designer",选择菜单栏 "File > New... > FPGA Design Project" 如图 3-1 所示。

图 3-1 新建 FPGA Design 工程

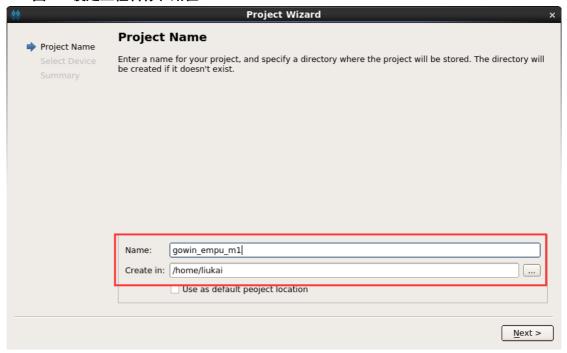

# 3.1.2 设定工程名称和路径

输入工程名称,选择工程路径,如图 3-2 所示。

IPUG531-1.5 11(42)

3 工程模板 3.1 工程创建

图 3-2 设定工程名称和路径

# 3.1.3 选择器件

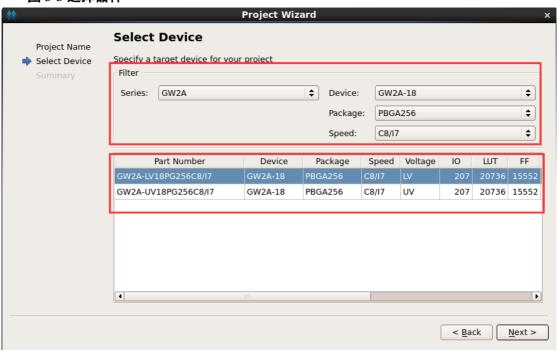

选择器件、封装和速度等,如图 3-3 所示。

图 3-3 选择器件

# 3.1.4 完成工程创建

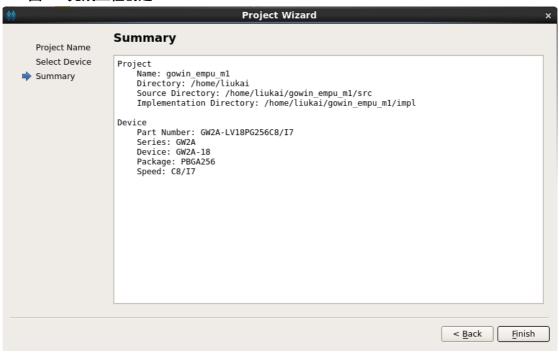

如图 3-4 所示,完成新建工程。

IPUG531-1.5 12(42)

#### 图 3-4 完成工程创建

# 3.2 硬件设计

使用 IP Core Generator 产生 Gowin EMPU M1 硬件设计。

图 3-5 选择 Gowin\_EMPU\_M1

打开 Gowin\_EMPU\_M1, Gowin\_EMPU\_M1 系统架构如图 3-6 所示, 包括 Cortex-M1 和 AHB Lite Extension (APB Bus Peripherals 和 AHB Bus

IPUG531-1.5

#### Peripherals)选择配置。

#### 图 3-6 Gowin\_EMPU\_M1 系统架构

# 3.2.1 Cortex-M1 硬件设计

Cortex-M1 硬件设计配置选项如表 3-1。

表 3-1 Cortex-M1 配置选项

| 配置选项                 | 描述                                                                               |

|----------------------|----------------------------------------------------------------------------------|

| Number of interrupts | 配置 Cortex-M1 外部中断数量,可选择 1 或 8 或 16 或 32,默认为 32。                                  |

| OS Extension         | 配置 Cortex-M1 是否支持操作系统,默认为支持。                                                     |

| Small Multiplier     | 配置 Cortex-M1 small 模式硬件乘法器,默认为 normal 模式。                                        |

| Big Endian           | 配置 Cortex-M1 数据大端格式,默认为小端格式。                                                     |

| Enable Debug         | 使能 Cortex-M1 Debug 功能,默认为使能 Debug。                                               |

| Debug Port Select    | 配置调试器接口,可以选择 JTAG 或 Serial Wire 或 JTAG and Serial Wire,默认为 JTAG and Serial Wire。 |

| Small Debug          | 配置 Small 模式调试器,默认为 Full 模式调试器。                                                   |

| ITCM Alias Select    | 配置 ITCM Alias,可以选择 Upper 或 Lower,默认为 Lower Alias。                                |

| ITCM Size            | 配置 ITCM 的大小,可以选择 1KB 或 2KB 或 4KB 或 8KB 或 16KB 或 32KB                             |

IPUG531-1.5 14(42)

| 配置选项                     | 描述                                                              |  |

|--------------------------|-----------------------------------------------------------------|--|

|                          | 或 64KB 或 128KB 或 256KB。                                         |  |

|                          | ● GW1N-9/GW1NR-9 系列最大选择 32KB,默认为 16KB;                          |  |

|                          | ● GW2A-18/GW2A-18C/GW2AR-18/GW2AR-18C 系列最大选择 64KB,<br>默认为 32KB; |  |

|                          | ● GW2A-55/GW2A-55C 系列最大选择 256KB,默认为 64KB。                       |  |

| Initialize ITCM          | 使能 ITCM 初始化,默认为禁用。                                              |  |

| ITCM Initialization Path | ITCM 初始值文件路径。                                                   |  |

| DTCM Size                | 配置 DTCM 的大小,可以选择 1KB 或 2KB 或 4KB 或 8KB 或 16KB 或 32KB            |  |

|                          | 或 64KB 或 128KB 或 256KB。                                         |  |

|                          | ● GW1N-9/GW1NR-9 系列最大选择 32KB,默认为 16KB;                          |  |

|                          | ● GW2A-18/GW2A-18C/GW2AR-18/GW2AR-18C 系列最大选择 64KB,              |  |

|                          | 默认为 32KB;                                                       |  |

|                          | ● GW2A-55/GW2A-55C 系列最大选择 256KB,默认为 64KB。                       |  |

双击 Cortex-M1, 打开 Cortex-M1 的配置页面,如图 3-7 所示,包括通用配置、调试配置和存储配置。

图 3-7 Cortex-M1 配置页面

#### 通用配置

选择通用配置选项卡,如图 3-8 所示,可以配置中断数量、操作系统扩展、乘法器模式和数据存储格式。

IPUG531-1.5 15(42)

图 3-8 Cortex-M1 通用配置

- 中断数量配置 可以选择 1 或 8 或 16 或 32,可以配置 1 个或 8 个或 16 个或 32 个外部 中断,默认为 32 个。

- 操作系统扩展配置 如果选择,则 Cortex-M1 扩展支持操作系统,默认为支持操作系统扩展。

- 乘法器模式配置 如果选择,则 Cortex-M1 支持 Small 乘法器,否则支持 Normal 乘法器, 默认为 Normal 乘法器。

- 数据存储格式配置 如果选择,则 Cortex-M1 支持数据大端格式,否则支持数据小端格式, 默认为小端格式。

#### 调试配置

选择调试配置选项卡,如图 3-9 所示,可以配置使能调试、调试接口和调试器模式。

IPUG531-1.5

图 3-9 Cortex-M1 调试配置

#### Enable Debug

如果选择 Enable Debug, Cortex-M1 支持调试功能, 否则 Cortex-M1 不支持调试功能, 默认为使能 Debug。

- 调试接口配置 可以选择 JTAG 或 Serial Wire 或 JTAG and Serial Wire,默认为 JTAG and Serial Wire。

- 调试器模式配置 如果选择,则 Cortex-M1 支持 Small 模式调试器,否则支持 Full 模式调 试器,默认为 Full 模式调试器。

#### 存储配置

选择存储配置选项卡,如图 3-10 所示,可以配置 ITCM 和 DTCM。

IPUG531-1.5 17(42)

图 3-10 Cortex-M1 存储配置

#### ● ITCM 配置

- ITCM Alias 配置可以选择 Enable Upper 或 Lower Alias, 默认为 Lower Alias:

- Lower Alias: 地址空间中 ITCM 的起始地址为 0x00000000;

- Upper Alias: 地址空间中 ITCM 的起始地址为 0x10000000。

#### ● ITCM Size 配置

- 可以选择 1KB 或 2KB 或 4KB 或 8KB 或 16KB 或 32KB 或 64KB 或 128KB 或 256KB:

- GW1N-9/GW1NR-9系列ITCM Size 最大选择为32KB,默认为16KB;

- GW2A-18/GW2A-18C/GW2AR-18/GW2AR-18C 系列 ITCM Size 最大选择为 64KB,默认为 32KB;

- GW2A-55/GW2A-55C 系列 ITCM Size 最大选择为 256KB,默认为 64KB。

#### ● ITCM Initialization 配置

- 如果选择 Initialize ITCM,则支持 ITCM 初始化,可以在 ITCM Initialization Path 导入 ITCM 初始值文件路径;

- 如果选择使用片外 SPI-Flash 下载启动方式,ITCM 初始值根据不同

IPUG531-1.5

的 ITCM Size 导入不同的 bootload 文件路径:

#### 注!

ITCM Initialization Path 导入的路径,不能有以数字命名的文件夹路径。

#### ● DTCM 配置

- DTCM Size 配置可以选择 1KB 或 2KB 或 4KB 或 8KB 或 16KB 或 32KB 或 64KB 或 128KB 或 256KB;

- GW1N-9/GW1NR-9 系列 DTCM Size 最大选择为 32KB,默认为 16KB:

- GW2A-18/GW2A-18C/GW2AR-18/GW2AR-18C 系列 DTCM Size 最大选择为 64KB,默认为 32KB;

- GW2A-55/GW2A-55C 系列 DTCM Size 最大选择为 256KB, 默认为 64KB。

#### ■ ITCM 与 DTCM 配置限制

- GW1N-9/GW1NR-9 系列,ITCM 或 DTCM 最大可配置为 32KB,如果ITCM 或 DTCM 某个存储器已配置为 32KB,则另一个存储器最大只能配置为 16KB;

- GW2A-18/GW2A-18C/GW2AR-18/GW2AR-18C 系列, ITCM 或 DTCM 最大可配置为 64KB, 如果 ITCM 或 DTCM 某个存储器已配 置为 64KB,则另一个存储器最大只能配置为 16KB;

- GW2A-55/GW2A-55C 系列,ITCM 或 DTCM 最大可配置为 256KB, 如果 ITCM 或 DTCM 某个存储器已配置为 256KB,则另一个存储器 最大只能配置为 16KB。

### 3.2.2 AHB-Lite Extension 硬件设计

AHB-Lite Extension 配置选项如表 3-2 所示。

表 3-2 AHB-Lite Extension 配置选项

| 配置选项                  | 描述                                         |

|-----------------------|--------------------------------------------|

| Enable GPIO           | 使能 GPIO,默认关闭。                              |

| Enable CAN            | 使能 CAN,默认关闭。                               |

| Buffer Depth          | CAN 选择 Buffer Depth,默认值为 256。              |

| Enable Ethernet       | 使能 Ethernet,默认关闭。                          |

| Interface             | Ethernet 选择 Interface (RGMII/GMII/MII),默认为 |

|                       | RGMII。                                     |

| RGMII Input Delay     | RGMII input delay,默认值为 100。                |

| MIIM Clock Divider    | MIIM clock divider, 默认值为 20。               |

| Enable DDR3           | 使能 DDR3 Memory,默认关闭。                       |

| Enable PSRAM          | 使能 PSRAM,默认关闭。                             |

| Enable SPI-Flash      | 使能 SPI-Flash 下载功能和 Memory 读、写、擦除功能,        |

|                       | 默认关闭。                                      |

| Enable AHB2 Extension | 使能 AHB2 扩展接口,默认关闭。                         |

| Enable UART0          | 使能串口 0, 默认关闭。                              |

| Enable UART1          | 使能串口 1,默认关闭。                               |

IPUG531-1.5 19(42)

| 配置选项                  | 描述                 |

|-----------------------|--------------------|

| Enable Timer0         | 使能定时器 0,默认关闭。      |

| Enable Timer1         | 使能定时器 1,默认关闭。      |

| Enable WatchDog       | 使能看门狗,默认关闭。        |

| Enable RTC            | 使能 RTC,默认关闭。       |

| Enable TRNG           | 使能 TRNG,默认关闭。      |

| Enable DualTimer      | 使能 DualTimer,默认关闭。 |

| Enable I2C            | 使能 I2C,默认关闭。       |

| Enable SPI            | 使能 SPI,默认关闭。       |

| Enable SD-Card        | 使能 SD-Card,默认关闭。   |

| Enable APB2 Extension | 使能 APB2 扩展接口,默认关闭。 |

#### GPIO 配置

双击打开 GPIO,可以选择配置 GPIO,如图 3-11 所示。

默认关闭,如果选择 Enable GPIO,则 Gowin\_EMPU\_M1 支持 GPIO。

#### 图 3-11 GPIO 配置

#### CAN 配置

- 双击打开 CAN,可以选择配置 CAN,如图 3-12 所示;

- 默认关闭,如果选择 Enable CAN,则 Gowin\_EMPU\_M1 支持 CAN;

IPUG531-1.5 20(42)

- 如果已经选择 Enable CAN,则可以配置 Buffer Depth;

- 选择 Buffer Depth, 配置 Buffer Depth, 默认值为 256。

#### 图 3-12 CAN 配置

#### Ethernet 配置

- 双击打开 Ethernet, 可以选择配置 Ethernet, 如图 3-13 所示:

- 默认关闭,如果选择 Enable Ethernet,则 Gowin\_EMPU\_M1 支持 Ethernet:

- 如果已经选择 Enable Ethernet,则可以配置 Interface、RGMII Input Delay、MIIM Clock Divider。

- 选择 Interface,可以选择配置 RGMII、GMII、MII 或 GMII/MII,默 认为 RGMII:

- 如果选择 Interface 为 RGMII,则可以选择配置 RGMII Input Delay, 默认值为 100;

- 选择 MIIM Clock Divider,可以配置 MIIM Clock Divider,默认值为 20。

- 如果 Interface 选择 RGMII 或 GMII,则端口 GTX\_CLK 必须接入 125MHz 时钟输入。

IPUG531-1.5 21(42)

图 3-13 Ethernet 配置

#### DDR3 配置

- 双击打开 DDR3,可以选择配置 DDR3,如图 3-14 所示;

- 默认关闭, 如果选择 Enable DDR3, 则 Gowin EMPU M1 支持 DDR3;

- DDR3 内部时钟频率 150MHz;

- DDR3 端口 DDR\_CLK\_I 必须接入 50MHz 时钟输入。

IPUG531-1.5 22(42)

#### 图 3-14 DDR3 配置

#### SPI-Flash 配置

- SPI-Flash 支持下载功能,和 Memory 读、写、擦除功能;

- 双击打开 SPI-Flash,可以选择配置 SPI-Flash,如图 3-15 所示;

- 默认关闭,如果选择 Enable SPI-Flash,则 Gowin\_EMPU\_M1 支持 SPI-Flash;

- 如果 Gowin\_EMPU\_M1 使用片外 SPI-Flash 下载启动方式,则必须选择 Enable SPI-Flash。

IPUG531-1.5 23(42)

#### 图 3-15 SPI-Flash 配置

#### AHB2 Extension 配置

- 双击打开 AHB2 Extension,可以选择配置 AHB2 Extension,如图 3-16 所示;

- 默认关闭,如果选择 Enable AHB2 Extension,则 Gowin\_EMPU\_M1 支持 AHB2 Extension,用户可以在此接口自行连接扩展的 AHB 外部设备。

IPUG531-1.5 24(42)

图 3-16 AHB2 Extension 配置

#### UART 配置

- ▼ 双击打开 UART0 或 UART1,可以选择配置 UART0 或 UART1,如图

3-17 所示;

- 默认关闭,如果选择 Enable UARTO,则 Gowin\_EMPU\_M1 支持 UARTO;

- 默认关闭,如果选择 Enable UART1,则 Gowin\_EMPU\_M1 支持 UART1。

IPUG531-1.5 25(42)

#### 图 3-17 UART 配置

#### Timer 配置

- 双击打开 Timer0 或 Timer1,可以选择配置 Timer0 或 Timer1,如图 3-18 所示;

- 默认关闭,如果选择 Enable Timer0,则 Gowin\_EMPU\_M1 支持 Timer0;

- 默认关闭,如果选择 Enable Timer1,则 Gowin\_EMPU\_M1 支持 Timer1。

IPUG531-1.5 26(42)

图 3-18 Timer 配置

#### WatchDog 配置

- 双击打开 WatchDog,可以选择配置 WatchDog,如图 3-19 所示;

- 默认关闭,如果选择 Enable WatchDog,则 Gowin\_EMPU\_M1 支持 WatchDog。

IPUG531-1.5 27(42)

图 3-19 WatchDog 配置

#### RTC 配置

- 双击打开 RTC,可以选择配置 RTC,如图 3-20 所示;

- 默认关闭,如果选择 Enable RTC,则 Gowin\_EMPU\_M1 支持 RTC。

IPUG531-1.5 28(42)

图 3-20 RTC 配置

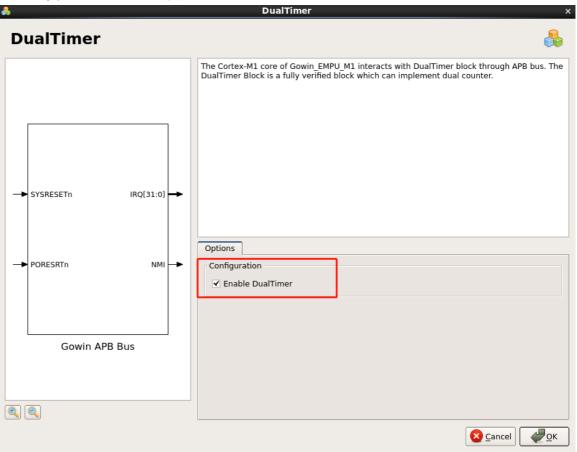

### DualTimer 配置

- 双击打开 DualTimer,可以选择配置 DualTimer,如图 3-21 所示;

- 默认关闭,如果选择 Enable DualTimer,则 Gowin\_EMPU\_M1 支持 DualTimer。

IPUG531-1.5 29(42)

图 3-21 DualTimer 配置

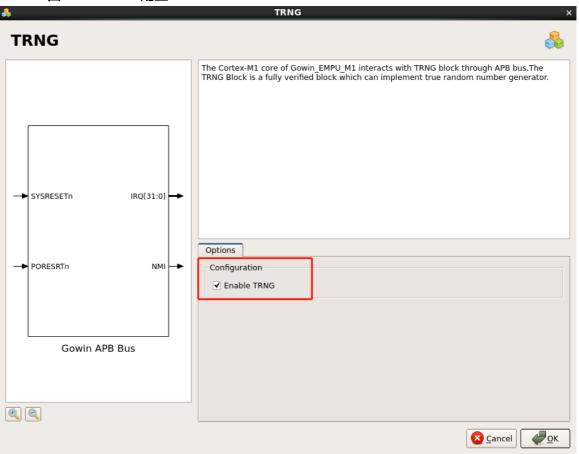

### TRNG 配置

- 双击打开 TRNG,可以选择配置 TRNG,如图 3-22 所示;

- 默认关闭,如果选择 Enable TRNG,则 Gowin\_EMPU\_M1 支持 TRNG。

IPUG531-1.5 30(42)

图 3-22 TRNG 配置

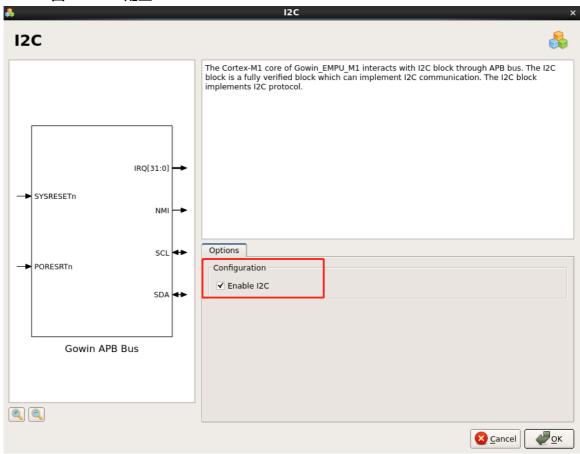

### I2C 配置

- 双击打开 I2C,可以选择配置 I2C,如图 3-23 所示;

- 默认关闭,如果选择 Enable I2C,则 Gowin\_EMPU\_M1 支持 I2C。

IPUG531-1.5 31(42)

图 3-23 I2C 配置

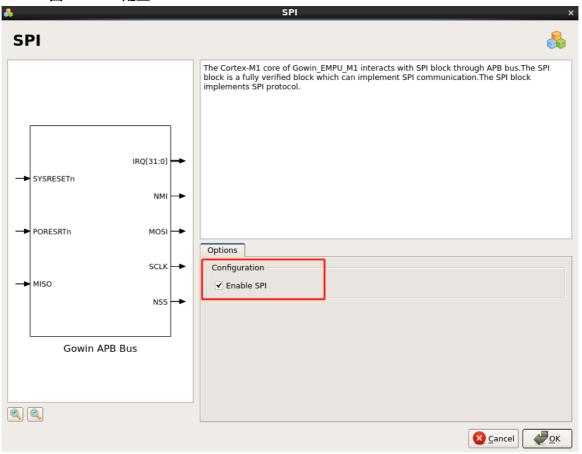

### SPI 配置

- 双击打开 SPI,可以选择配置 SPI,如图 3-24 所示;

- 默认关闭,如果选择 Enable SPI,则 Gowin\_EMPU\_M1 支持 SPI。

IPUG531-1.5 32(42)

图 3-24 SPI 配置

### SD-Card 配置

- 双击打开 SD-Card,可以选择配置 SD-Card,如图 3-25 所示;

- 默认关闭,如果选择 Enable SD-Card,则 Gowin\_EMPU\_M1 支持 SD-Card;

- SD-Card 端口 SD\_SPICLK 必须接入 30MHz 的时钟输入。

IPUG531-1.5 33(42)

图 3-25 SD-Card 配置

#### APB2 Extension 配置

- 双击打开 APB2 Extension,可以选择配置 APB2 Extension,如图 3-26 所示;

- 默认关闭,如果选择 Enable APB2 Extension,则 Gowin\_EMPU\_M1 支持 APB2 Extension,用户可以在此接口自行连接扩展的 APB 外部设备。

IPUG531-1.5 34(42)

图 3-26 APB2 Extension 配置

#### PSRAM 配置

- 双击打开 PSRAM,可以选择配置 PSRAM,如图 3-27 所示;

- 默认关闭,如果选择 Enable PSRAM,则 Gowin\_EMPU\_M1 支持 PSRAM;

- 如下器件(GW2AR-18/GW2AR-18C)支持 Gowin\_EMPU\_M1 PSRAM:

- GW2AR-LV18QN88PES

- GW2AR-LV18QN88PC8/I7

- GW2AR-LV18QN88PC7/I6

- GW2AR-LV18EQ144PES

- GW2AR-LV18EQ144PC8/I7

- GW2AR-LV18EQ144PC7/I6

- GW2AR-LV18EQ144PC9/I8

IPUG531-1.5 35(42)

图 3-27 PSRAM 配置

### 综合工具配置

完成 Gowin\_EMPU\_M1 功能配置后,选择产生 Gowin\_EMPU\_M1 的综合工具 Synplify Pro 或 GowinSynthesis,如图 3-30 所示。

IPUG531-1.5 36(42)

3.3 用户设计

RTC

#### 图 3-28 综合工具配置

# 3.3 用户设计

telp

● 完成 Gowin EMPU M1 配置后,产生 Gowin EMPU M1 硬件设计;

TRNG

I2C

**C**ancel

- 实例化 Gowin EMPU M1;

- 导入用户设计,连接 Gowin EMPU M1,形成完整的 RTL 设计。

# 3.4 约束

完成用户 RTL 设计后,根据使用的开发板和需要输出的 IO,产生物理约束文件。

根据时序要求,产生时序约束文件。

物理约束的产生方法请参考 SUG101, Gowin 设计约束指南。

# 3.5 配置

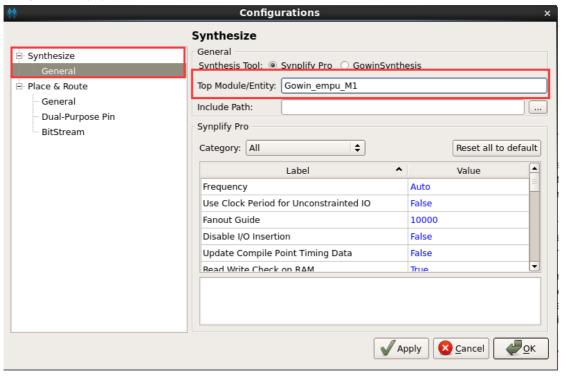

## 3.5.1 顶层模块配置

综合配置中,根据工程设计中的实际顶层模块名称配置此处顶层模块名

IPUG531-1.5 37(42)

3 工程模板 3.5 配置

称,如图 3-29 所示。

#### 图 3-29 顶层模块配置

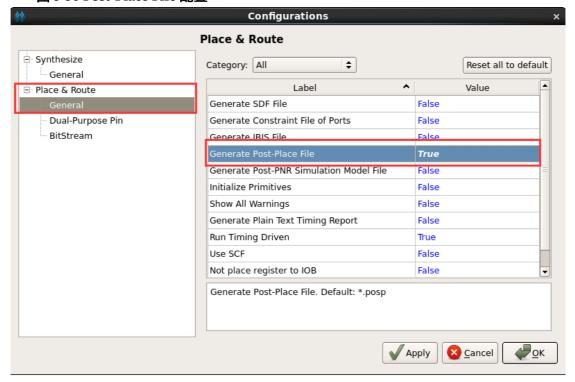

### 3.5.2 Post-Place File 配置

如果使用 Gowin\_EMPU\_M1 软件编程设计和硬件设计自动化合并的下载方法,则配置 Place & Route 产生 Post-Place File,如图 3-30 所示,否则不需要配置输出 Post-Place File。

图 3-30 Post-Place File 配置

IPUG531-1.5 38(42)

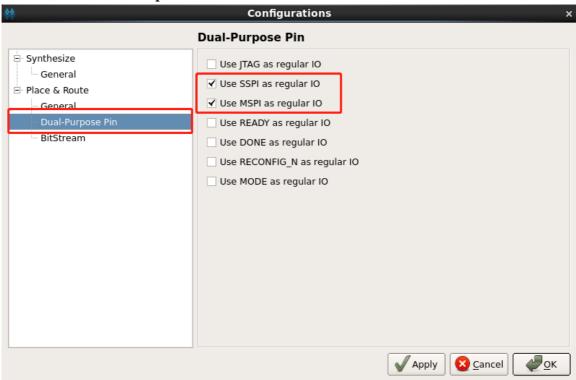

# 3.5.3 Dual-Purpose Pin 配置

如果 Gowin\_EMPU\_M1 使用片外 SPI-Flash 下载启动方式,复用 SSPI 和 MSPI 端口为通用端口,如图 3-31 所示,否则不需要配置端口复用。

图 3-31 Dual-Purpose Pin 配置

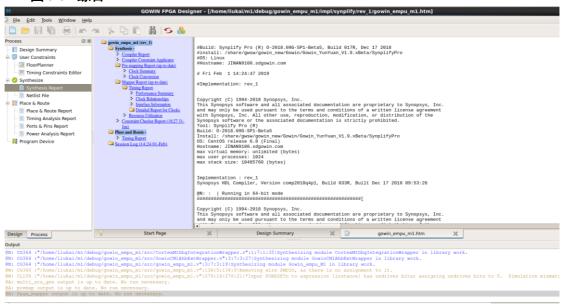

# 3.6 综合

运行 Gowin 云源软件的综合工具 Synplify\_Pro 或 GowinSynthesis, 完成 RTL 设计的综合,如图 3-32 图所示。

#### 图 3-32 综合

IPUG531-1.5 39(42)

3.7 布局布线

综合工具的使用方法请参考 SUG100, Gowin 云源软件用户指南。

# 3.7 布局布线

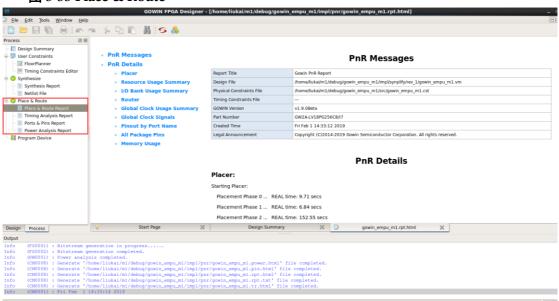

运行 Gowin 云源软件的布局布线工具 Place & Route,完成布局布线和 生成码流文件,如图 3-33 所示。

#### 图 3-33 Place & Route

布局布线工具使用方法请参考 SUG100, Gowin 云源软件用户指南。

# 3.8 下载

运行 Gowin 云源软件的下载工具 Programmer, 完成码流文件的下载。

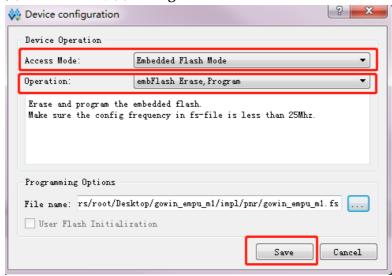

单击 "Programmer > Edit/Configure Device" 或工具栏 Configure Device "具",打开"Device configuration"对话框。

如果板载器件 GW1N-9/GW1NR-9 系列,"Access Mode"下拉列表中选择"Embedded Flash Mode","Operation"下拉列表中选择"embFlash Erase, Program","Programming Options"中导入需要下载的码流文件,单击"Save",如图 3-34 所示。

IPUG531-1.5 40(42)

3 工程模板 3.8 下载

### 图 3-34 GW1N 系列 Configure Device

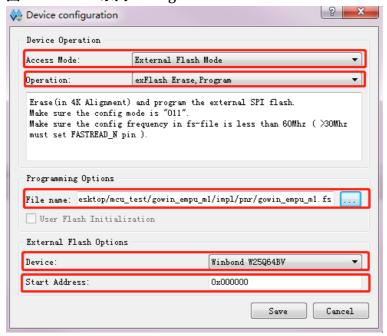

如果板载器件 GW2A-18/GW2A-18C/GW2AR-18/GW2AR-18C/GW2A-55/GW2A-55C, "Access Mode"下拉列表中选择"External Flash Mode"。"Operation"下拉列表中选择"exFlash Erase, Program"。"Programming Options"中导入需要下载的码流文件。"External Flash Options"中"Device"根据板载 Flash 芯片选择(如 Winbond W25Q64BV)。"Start Address"选择"0x000000",单击"Save",如图 3-35 所示。

#### 图 3-35 GW2A 系列 Configure Device

完成 Device configuration 后,单击"Programmer"工具链 Program/Configure "事",完成码流下载。

下载工具 Programmer 使用方法请参考 <u>SUG502</u>, Gowin Programmer 用户指南。

IPUG531-1.5 41(42)

# **4** 参考设计

Gowin\_EMPU\_M1 提供 Debug 和 No Debug 参考设计:

- Gowin\_EMPU\_M1\ref\_design\FPGA\_RefDesign\Debug\_RefDesign

- Gowin\_EMPU\_M1\ref\_design\FPGA\_RefDesign\NoDebug\_RefDesign

IPUG531-1.5 42(42)