# Gowin Triple Speed Ethernet MAC **User Guide**

IPUG538-1.0E, 2/20/2019

#### Copyright©2019 Guangdong Gowin Semiconductor Corporation. All Rights Reserved.

No part of this document may be reproduced or transmitted in any form or by any denotes, electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of GOWINSEMI.

#### Disclaimer

GOWINSEMI<sup>®</sup>, LittleBee<sup>®</sup>, Arora<sup>™</sup>, and the GOWINSEMI logos are trademarks of GOWINSEMI and are registered in China, the U.S. Patent and Trademark Office, and other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders, as described at www.gowinsemi.com. GOWINSEMI assumes no liability and provides no warranty (either expressed or implied) and is not responsible for any damage incurred to your hardware, software, data, or property resulting from usage of the materials or intellectual property except as outlined in the GOWINSEMI Terms and Conditions of Sale. All information in this document should be treated as preliminary. GOWINSEMI may make changes to this document at any time without prior notice. Anyone relying on this documentation should contact GOWINSEMI for the current documentation and errata.

#### **Revision History**

| Date      | Version | Description                |

|-----------|---------|----------------------------|

| 2/20/2019 | 1.0E    | Initial version published. |

## Content

| Content                                 | i  |

|-----------------------------------------|----|

| List of Figuresii                       | ii |

| List of Tables                          | V  |

| 1 About This Guide1                     | 1  |

| 1.1 Purpose                             | 1  |

| 1.2 Supported Products                  | 1  |

| 1.3 Related Documents                   | 1  |

| 1.4 Terminology and Abbreviations2      | 2  |

| 1.5 Support and Feedback                | 2  |

| 2 Overview                              | 3  |

| 3 Feature and Performance               | 4  |

| 3.1 Key Features                        | 4  |

| 3.2 Working Frequency                   | 4  |

| 3.3 Resource Utilization                | 4  |

| 4 Function and Structure Description6   | 6  |

| 4.1 Overall Structure6                  | 6  |

| 4.2 MAC Layer Interface                 | 7  |

| 4.2.1 RGMII Interface                   | 7  |

| 4.2.2 GMII Interface                    | 7  |

| 4.2.3 MII Interface                     | 8  |

| 4.2.4 RGMII/MII Interface               | 8  |

| 4.3 User Interface                      | 9  |

| 4.3.1 Ethernet Frame Reception          | 9  |

| 4.3.2 Ethernet Frame Transmission12     | 2  |

| 4.3.3 Flow Control Function             |    |

| 4.3.4 FCS Forward Function17            |    |

| 4.3.5 PAD Function                      |    |

| 4.3.6 Transmitting IFG Setting Function |    |

| 4.3.7 Jumbo Setting Function            |    |

| 4.3.8 Management Function               | 8  |

| 5 Port List                             | 0  |

| 6 Parameter Configuration | 24 |

|---------------------------|----|

| 7 Reference Design        | 25 |

| 8 Interface Configuration | 26 |

## **List of Figures**

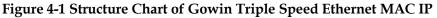

| Figure 4-1 The structure chart of Gowin Triple Speed Ethernet MAC IP                    | . 6  |

|-----------------------------------------------------------------------------------------|------|

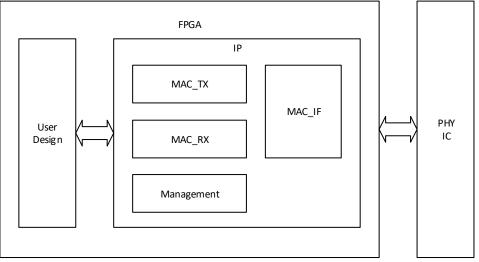

| Figure 4-2 Schematic diagram of RGMII pin connection                                    | . 7  |

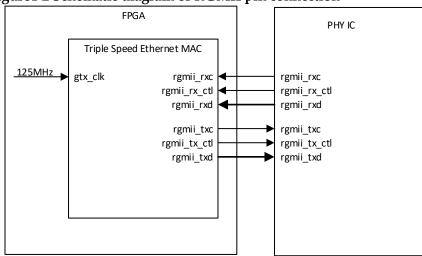

| Figure 4-3 Schematic diagram of GMII pin connection                                     | . 7  |

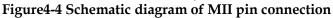

| Figure4-4 Schematic diagram of MII pin connection                                       | . 8  |

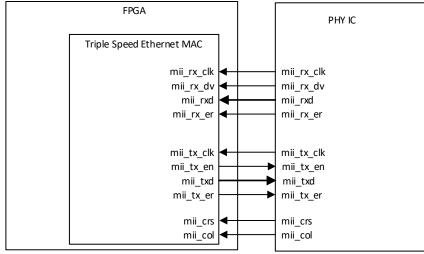

| Figure4-5 Schematic diagram of GMII/MII pin connection                                  | . 8  |

| Figure 4-6 Normal Ethernet Frame Reception at 1000M Rate                                | . 9  |

| Figure 4-7 Normal Ethernet Frame Reception at 10M/100M Rate                             | . 9  |

| Figure4-8 Error Ethernet Frame Reception at 1000M Rate                                  | . 9  |

| Figure4-9 Error Ethernet Frame Reception at 10M/1000M Rate                              | . 9  |

| Figure4-10 At 1000M Rate Enabling FCS Forward Correct Ethernet Frame Reception          | . 10 |

| Figure4-11 At 1000M Rate Enabling FCS Forward Error Ethernet Frame Reception            | . 10 |

| Figure4-12 At 100M Rate Enabling FCS Forward Correct Ethernet Frame Reception           | . 10 |

| Figure4-13 At 100M Rate Enabling FCS Forward Error Ethernet Frame Reception             | . 10 |

| Figure4-14 VLAN Tagged Frame Reception                                                  | . 10 |

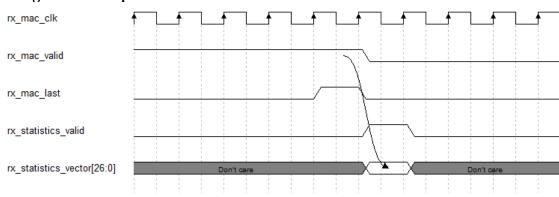

| Figure4-15 Reception Statistics                                                         | . 11 |

| Figure4-16 Normal Ethernet Frame Transmission at 1000M Rate                             | . 13 |

| Figure4-17 In RGMII Mode Normal Ethernet Frame Transmission at 10M/100M Rate            | . 13 |

| Figure4-18 In MII Mode Normal Ethernet Frame Transmission at 10M/100M Rate              | . 13 |

| Figure4-19 TX_ER for Ethernet Frame Transmission at 1000M rate                          | . 13 |

| Figure4-20 TX_ER Ethernet Frame Transmission at 10M/100M rate in RGMII Mode             | . 13 |

| Figure4-21 TX_ER Ethernet Frame Transmission at 10M/100M rate in MII Mode               | . 13 |

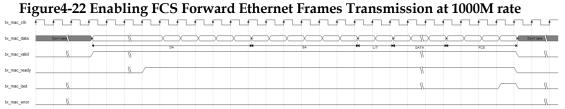

| Figure4-22 Enabling FCS Forward Ethernet Frames Transmission at 1000M rate              | . 14 |

| Figure 4-23 Enabling FCS Forward Ethernet Frames Transmission at 1000M rate in MII Mode | . 14 |

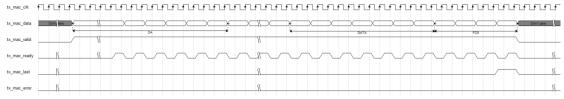

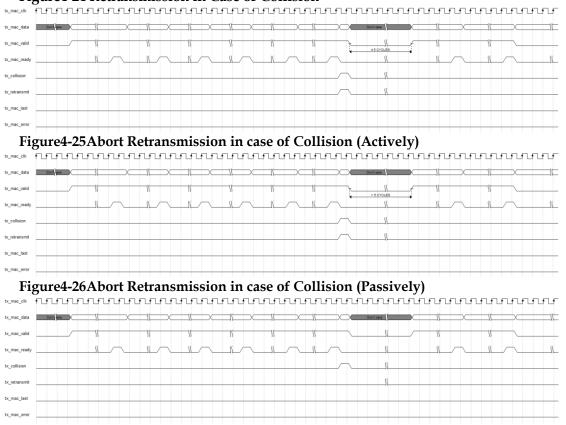

| Figure4-24 Retransmission in case of collision                                          | . 15 |

| Figure4-25Abort retransmission in case of collision (Actively)                          | . 15 |

| Figure4-26Abort retransmission in case of collision (Passively)                         | . 15 |

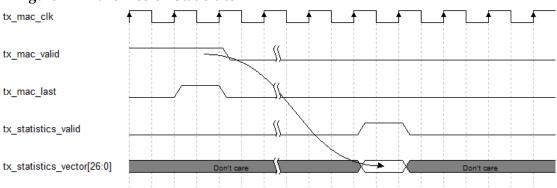

| Figure4-27Transmission Statisitics                                                      | . 15 |

| Figure4-28Transmitting Pause Frame                                                      | . 16 |

| Figure4-29Receiving Pause Frame                                                         | . 17 |

| Figure4-30 Schematic Diagram of Connection between mdc and mdio                         | . 18 |

| Figure4-31 The Write Timing of miim                                                     | . 19 |

| Figure4-32 The Read Timing of Miim                                                      | . 19 |

| Figure8-1 IP Core Generation Tool                              | 26 |

|----------------------------------------------------------------|----|

| Figure8-2 Triple Speed Ethernet MAC IP Configuration Interface | 27 |

| Figure8-3 Triple Speed Ethernet MAC IP Help                    | 27 |

## **List of Tables**

| Table1-1 Terminology and Abbreviation                                         | 2  |

|-------------------------------------------------------------------------------|----|

| Table2-1 Gowin Triple Speed Ethernet MAC IP                                   | 3  |

| Table3-1 Resource Utilization                                                 | 5  |

| Table 4-1 Rx_Statistics_Vector Bit Definition                                 | 12 |

| Table 4-2 Bit Definition of tx_statistics_vector                              | 16 |

| Table 5-1 The IO port for Gowin Triple Speed Ethernet MAC IP                  | 21 |

| Table 6-1 Static and Timing Parameters of the Gowin Triple Speed Ethernet MAC | 24 |

## **1** About This Guide

## 1.1 Purpose

This user guide is designed to help users quickly learn the function of Gowin Triple Speed Ethernet MAC IP. It mainly helps the user quickly understand the feature, characteristic and usage of Gowin Triple Speed Ethernet MAC IP.

## **1.2 Supported Products**

The information presented in this guide applies to the following products:

- 1. GW1N series (except GW1N-1)

- 2. GW1NR series

- 3. GW2A series

- 4. GW2AR series

### **1.3 Related Documents**

The user guides are available on the GOWINSEMI Website. You can find the related documents at www.gowinsemi.com:

- 1. GW1N series FPGA Products Data Sheet

- 2. GW1NR series FPGA Products Data Sheet

- 3. GW2A series FPGA Products Data Sheet

- 4. GW2AR series FPGA Products Data Sheet

- 5. Gowin YunYuan Software User Guide

## 1.4 Terminology and Abbreviation

The terminology and abbreviation used in this manual are as shown in Table1-1 below.

| Table1-1 | Termino | logy and | Abbreviation |

|----------|---------|----------|--------------|

|----------|---------|----------|--------------|

| Terminology and Abbreviations | Full Name             |

|-------------------------------|-----------------------|

| IP                            | Intellectual Property |

| LUT                           | Look-up Table         |

## **1.5 Support and Feedback**

Gowin Semiconductor provides customers with comprehensive technical support. If you have any questions, comments, or suggestions, please feel free to contact us directly by the following ways.

Website: www.gowinsemi.com.cn

E-mail: support@gowinsemi.com

+Tel: +86 755 8262 0391

## 2<sub>Overview</sub>

This document describes Triple Speed Ethernet MAC IP, which realizes the function description of MAC layer in the IEEE802.3 protocol. Triple Speed Ethernet MAC IP provides a universal access interface for users. It can be integrated into devices that require an Ethernet MAC, a connection typically used for communication applications.

| Gowin Triple Speed Ethernet MAC IP |                                                                   |  |  |  |  |  |  |  |  |

|------------------------------------|-------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Supporting devices                 | GW1N series (except GW1N) ,GW1NR series,GW2A series, GW2AR series |  |  |  |  |  |  |  |  |

| Logic Resource                     | See Table3-1。                                                     |  |  |  |  |  |  |  |  |

| Delivered Doc.                     |                                                                   |  |  |  |  |  |  |  |  |

| Design Files                       | Verilog (encryption)                                              |  |  |  |  |  |  |  |  |

| Reference Design                   | Verilog                                                           |  |  |  |  |  |  |  |  |

| Testing platform                   | Verilog                                                           |  |  |  |  |  |  |  |  |

| Test and Design Flow               |                                                                   |  |  |  |  |  |  |  |  |

| Synthesis Software                 | Synplify_Pro                                                      |  |  |  |  |  |  |  |  |

| Application Software               | GowinYunYuan                                                      |  |  |  |  |  |  |  |  |

#### Table2-1 Gowin Triple Speed Ethernet MAC IP

# **3**<sub>Feature and Performance</sub>

### **3.1 Key Features**

- Support MII/GMII/RGMII interface

- Conform to IEEE 802.3 protocol;

- Support 10/100/1000m rate

- Support full duplex and half duplex mode, conflict detection supported in half duplex mode

- Support users to choose whether to automatically add and verify CRC

- Support the function of adding pad automatically

- Support Ethernet frame classification statistics

- Support Ethernet frame error statistics

- Support IFG configurable functions

- Support Jumbo mode

- Support Flow Control in full duplex mode

- Support Management interface mdc, mdio.

## 3.2 Working Frequency

The Gowin Triple Speed Ethernet MAC IP working frequency depends on the current operation mode of IP. References are as follows:

- When IP is configured to RGMII mode, the working frequency supports 1000/100/10mhz

- When IP is configured to GMII mode, the working frequency supports 1000mhz

- When IP is configured to MII mode, the working frequency supports 100/10mhz

- When IP is configured to GMII/MII mode, the working frequency supports 1000/100/10mhz

## 3.3 Resource Utilization

Gowin Triple Speed Ethernet MAC IP adopts Verilog language, which applies in GW1N series (except GW1N-1), GW1NR series, GW2A series and GW2AR series FPGA devices. Different modes have different resource consumption. An overview of resource utilization is given in Table3-1. For the resource utilization of other devices, please refer to the post release information.

| Interface | LUTs | REGs | Device Series | Speed Level |

|-----------|------|------|---------------|-------------|

| RGMII     | 1298 | 1284 | GW2A18        | -8          |

| GMII      | 899  | 1041 | GW2A18        | -8          |

| MII       | 1142 | 1224 | GW2A18        | -8          |

| GMII/MII  | 1245 | 1261 | GW2A18        | -8          |

## **4** Function and Structure Description

## **4.1 Overall Structure**

The basic structure of Gowin Triple Speed Ethernet MAC IP is shown in figure 4-1, mainly including MAC\_IF, MAC\_RX, MAC\_TX, Management and other modules. The User Design in Figure 4-1 is the user design in FPGA, and the PHY IC is the chip of Ethernet PHY, which is externally connected.

- MAC\_TX module realizes the conversion from user data format to Ethernet data format, as well as CRC, PAD, Flow Control, frame statistics and other functions.

- MAC\_RX module realizes the conversion from Ethernet data format to user data format, as well as CRC, Flow Control, IFG configuration, frame statistics, error indication and other functions.

- AC\_IF module realizes the function of Ethernet data adaption to various MAC interface, such as RGMII, GMII, MII.

- Management realizes MDC and MDIO functions of Ethernet management interface and facilitates users to configure PHY IC.

## 4.2 MAC Layer Interface

IP supports 4 MAC layer interfaces, namely RGMII interface, GMII interface, MII interface and GMII/MII interface. The supporting mode of each interface is listed as follows:

- RGMII interface supports 1000/100/10m full-duplex and 100/10m half-duplex;

- GMII interface supports 1000M full-duplex;

- MII interface supports 100/10m full-duplex and 100/10m half-duplex;

- GMII/MII interface supports 1000/100/10m full-duplex and 100/10m half-duplex.

#### 4.2.1 RGMII Interface

The RGMII interface includes 12 lines, namely rgmii\_rxc, rgmii\_rx\_ctl, rgmii\_rxd[3:0], rgmii\_txc, rgmii\_tx\_ctl, rgmii\_txd[3:0]. The user needs to provide 125MHz clock for IP through gtx\_clk. Figure4-2 is the schematic diagram of connecting pin of RGMII interface and PHY chip. Figure4-2 Schematic diagram of RGMII pin connection

#### 4.2.2 GMII Interface

GMII interface includes 22 lines, namely gmii\_rx\_clk, gmii\_rx\_dv, gmii\_rxd[7:0], gmii\_rx\_er, gmii\_tx\_clk, gmii\_tx\_en, gmii\_txd[7:0], gmii\_tx\_er. The user needs to provide 125MHz clock for IP through gtx\_clk. Figure4-3 is the schematic diagram of connecting pin of GMII interface and PHY chip. Figure4-3 Schematic Diagram of GMII Pin Connection

#### 4.2.3 MII Interface

MII interface includes 16 lines, namely mii\_rx\_clk, mii\_rx\_dv, mii\_rx\_dv, mii\_rxd[3:0], mii\_rx\_er, mii\_tx\_clk, mii\_tx\_en, mii\_txd[3:0], mii\_tx\_er, mii\_crs, mii\_col. Figure4-4 is the schematic diagram of connecting pin of MII interface and PHY chip.

#### 4.2.4 RGMII/MII Interface

GMII/MII interface is the combination of GMII interface and MII interface. It is usually connected to PHY chips supporting both GMII and MII. The transmit direction requires the user to select TXD, tx\_en, and tx\_er signals based on the current Ethernet rate. Figure4-5 is the schematic diagram of connecting pin of GMII/MII interface and PHY chip. Figure4-5 Schematic diagram of GMII/MII pin connection

## 4.3 User Interface

### **4.3.1 Ethernet Frame Reception**

Receiving Ethernet frame is the process of converting MAC interface data into user interface data. All received signals are synchronized with rx mac clk.

#### Normal Frame Reception

Figure 4-6 shows the normal Ethernet frame receiving process at1000M rate.

Figure 4-7 shows the normal Ethernet frame receiving process at 10M/100M rate.

When rx mac valid is 1, it means that rx mac data for this period is valid: When rx mac valid and rx mac last are both 1, rx mac data for this period is valid and is the last byte of this Ethernet frame. It should be noted that there is no buffer in IP to cache the incoming Ethernet frames, so the user must always be ready to receive Ethernet frames. When the first byte of the frame begins to appear in the user interface, the data is received continuously until the entire frame is received.

#### Figure4-6 Normal Ethernet Frame Reception at 1000M Rate

| rx_mac_clk   |     | ~        |   |   |   |    |        |   | <u></u> |        |        |        |   |   |   |    |   |   |        |    |   | 1 |      |      |          | r_f        | _ |

|--------------|-----|----------|---|---|---|----|--------|---|---------|--------|--------|--------|---|---|---|----|---|---|--------|----|---|---|------|------|----------|------------|---|

| rx_mac_data  | Dor | 1 0848   | × | X | × | X  | $\sim$ | X | ×       | $\sim$ | $\sim$ | $\sim$ | x | × | X | X  | X | X | $\sim$ |    | Þ |   |      |      | Dor      | n'i cere 👔 |   |

| rx_mac_valid |     | <u> </u> |   |   |   | UA |        |   |         |        |        |        |   |   |   | 01 |   |   |        | 5  | 5 |   | <br> | <br> | <u> </u> |            | _ |

| rx_mac_last  |     |          |   |   |   |    |        |   |         |        |        |        |   |   |   |    |   |   |        | \$ | L | _ |      | <br> | $\sim$   |            | _ |

| rx_mac_error |     | \$       |   |   |   |    |        |   |         |        |        |        |   |   |   |    |   |   |        | S  | L |   | <br> | <br> |          |            | _ |

#### Figure 4-7 Normal Ethernet Frame Reception at 10M/100M Rate

| rx_mac_data  | Don't car | X |     | X | <br>$\times$ |   |    |   | X    |        | ж |    |   |      |  | Don't Gate |

|--------------|-----------|---|-----|---|--------------|---|----|---|------|--------|---|----|---|------|--|------------|

| rx_mac_valid |           |   | ~~~ |   |              | ~ | 54 | ~ | *    | ыт<br> | * | ~~ |   | DATA |  |            |

| rx_mac_last  |           |   |     |   |              |   |    |   | <br> |        |   |    | ( |      |  |            |

| rx_mac_error |           |   |     |   |              |   |    |   |      |        |   |    |   |      |  | 11         |

#### **Error Frame Reception**

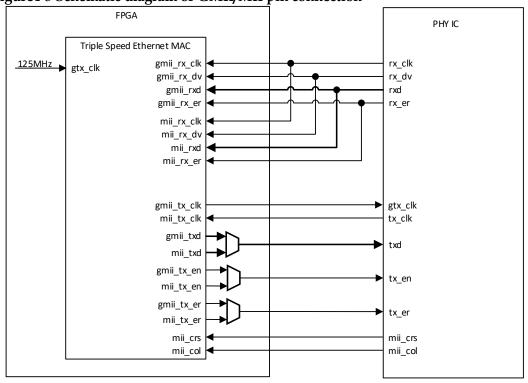

When rx mac error is 1, it indicates that there are certain errors in the current frame, and the specific error type can be checked by rx statistics valid and rx statistics vector signals. Rx mac error indicates the error state of the current frame only if rx mac last is 1. Figure 4-8 and Figure 4-9 show the receiving process of an error frame at 1000M and 10M/100M rate respectively.

Figure 4-8 Error Ethernet Frame Reception at 1000M Rate

| rx_mac_clk   |            |   | -4 | 4      |        |        |        |        |   | ſ      |   |    | 1 | 1      | 1 |        | <u></u> |        |        |       |      | <br>r_4 |          |          | - |

|--------------|------------|---|----|--------|--------|--------|--------|--------|---|--------|---|----|---|--------|---|--------|---------|--------|--------|-------|------|---------|----------|----------|---|

| rx_mac_data  | Don't care | \ |    | $\sim$ | $\sim$ | $\sim$ | $\sim$ | $\sim$ | × | $\sim$ | X | X  | X | $\sim$ | × | $\sim$ | )(      | $\sim$ | $\sim$ | x_1px |      |         |          | ant care |   |

| rx_mac_valid |            | 1 |    |        |        |        |        |        |   |        |   | 54 |   |        |   |        |         |        |        | 1     |      | <br>    |          |          | _ |

| rx_mac_last  | 1          | 1 |    |        |        |        |        |        |   |        |   |    |   |        |   |        |         |        |        |       | <br> | <br>    | <u> </u> |          | _ |

| rx_mac_error |            | 1 |    |        |        |        |        |        |   |        |   |    |   |        |   |        |         |        |        |       | <br> | <br>    |          |          | _ |

#### Figure4-9 Error Ethernet Frame Reception at 10M/1000M Rate

When the following errors occur, rx mac error will indicate:

- 1. Receiving FCS error frame ;

- 2. Receiving align frame;

- 3. In the receiving process, the MAC interface RX\_ER valid signal is received ;

- 4. Conflicts occur in half duplex;

- 5. Frame length error. When the Jumbo function is disabled, receive non-vlan frame of less than 64 bytes or more than 1518 bytes, and vlan frames of less than 64 bytes or more than 1522 bytes; When Jumbo function is disabled, receive frame of less than 64 bytes.

#### **Received Frame FCS Forward**

When the user sets IP to the mode of receiving FCS Forward, IP will send the received FCS field to the user side, as shown in Figure4-10, Figure4-11, Figure4-12 and Figure4-13. Now, IP still automatically verifies the FCS field and indicates by rx\_mac\_error and rx\_statistics\_vector. Figure4-10 1000M Rate Enabling FCS Forward Correct Ethernet Frame Reception

| rx_mac_data  | Don't care | ×  | X | X | X  | $\sim$ | X | ж | <u> </u> |    |      | ×  | $\sim$ | ×  | X | X |         | X | $\sim$ | X | $\sim$ | X   | X | × •      | ion'i care |   |

|--------------|------------|----|---|---|----|--------|---|---|----------|----|------|----|--------|----|---|---|---------|---|--------|---|--------|-----|---|----------|------------|---|

| rx_mac_valid | ((         | 1  |   |   | DA |        |   | × | <br>     | 54 | <br> | M. | UT     | M. |   |   | DATA (( |   |        | × |        | FCS |   | *        | "          |   |

| TA_INAC_VAIN |            | Ť. |   |   |    |        |   |   |          |    |      |    |        |    |   |   | Y       |   |        |   |        |     |   | _        |            |   |

| rx_mac_last  |            |    |   |   |    |        |   |   |          |    | <br> |    |        |    |   |   | 1       |   |        |   |        |     |   | <u> </u> |            | - |

| rx_mac_error | (          |    |   |   |    |        |   |   |          |    |      |    |        |    |   |   | 5       |   |        |   |        |     |   |          | ((         |   |

|              |            |    |   |   |    |        |   |   |          |    |      |    |        |    |   |   |         |   |        |   |        |     |   |          |            |   |

#### Figure4-11 1000M Rate Enabling FCS Forward Error Ethernet Frame Reception

| rx_mac_clk   |            | ЧЧ |    | - f |   |   |   |   |   |   | <u></u> |   | r |   | Ţ    | Ļ    | Lf L | <u>_</u> |   | <u> </u> |   | <u></u>  |           | 1        |

|--------------|------------|----|----|-----|---|---|---|---|---|---|---------|---|---|---|------|------|------|----------|---|----------|---|----------|-----------|----------|

| rx_mac_data  | Don't care |    |    | x   | × | X | X | X | X | X | ×       | X | ¥ | X |      | -IIX |      | X        | X | X        | X | ×        | on't care | -        |

| rx_mac_valid |            |    | DA |     |   |   |   | - |   |   |         |   |   |   | DATA |      |      |          |   |          |   | <u> </u> |           | <u> </u> |

| rx_mac_last  |            |    |    |     |   |   |   |   |   |   |         |   |   |   |      |      |      |          |   |          |   | ~        | (         | <u> </u> |

| rx_mac_error | 8          |    |    |     |   |   |   |   |   |   |         |   |   |   |      | 55   |      |          |   |          |   | <u> </u> | 5         |          |

#### Figure4-12 100M Rate Enabling FCS Forward Correct Ethernet Frame Reception

| rx_mac_clk   | flflf | - fl | flf           | Lf L | Гŀ | ЦП | L <del>.</del> L | flf | Ţ               | LΠ | £. | flf | Ŀf | ЦП | f Lf | Ŀ  | ЦП | ſĿ       | flf | цī | flf | - f | LΓ | £. | FLf | цП | £14      | Ŀ | Ŀf | ել | fц | Ŀ   | ĿГ | flf | Ŀ        | L-L       | ΓĿΓ |  |

|--------------|-------|------|---------------|------|----|----|------------------|-----|-----------------|----|----|-----|----|----|------|----|----|----------|-----|----|-----|-----|----|----|-----|----|----------|---|----|----|----|-----|----|-----|----------|-----------|-----|--|

| rx_mac_data  | Don't |      |               | _    |    | _  | _                |     | $ \rightarrow $ |    | ×  |     | ×  |    |      | ×  | _x | _        | ×   | ×  |     | ×   | ×  |    | x   |    | 1        | × | X  |    |    | X   |    |     | ×        | Don't cer |     |  |

| rx_mac_valid |       |      | $\overline{}$ | ~_   |    |    | ~                |     | Ý               |    | 7  |     |    | 7  |      | 5A | 4  | <u> </u> |     | Ţ  |     |     | Ť  |    |     |    | ir_      |   | Ý  | ~  |    | FCS |    |     | <u> </u> |           | 1   |  |

| rx_mac_last  |       |      |               |      |    |    |                  | -   |                 |    |    |     |    |    |      |    |    |          |     |    |     |     |    |    | _   |    | <u>%</u> |   | _  |    |    |     |    |     |          |           |     |  |

| rx_mac_error |       |      |               |      |    |    |                  | -   |                 |    | _  |     |    | _  |      |    |    |          |     | _  | -   |     |    |    | -   | _  | <u>n</u> |   | _  |    |    |     | _  | -   |          |           | 1   |  |

#### Figure4-13 100M Rate Enabling FCS Forward Error Ethernet Frame Reception

| ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | ษษษะ       |

|-----------------------------------------|------------|

|                                         | Don't care |

|                                         |            |

| n_mac_last                              |            |

#### **VLAN Tagged Frame Reception**

When IP receives a VLAN Tagged frame, it indicates that this frame is a VLAN Tagged frame in rx\_statistics\_vector. VLAN Tagged frame is the 0x8100 frame which is two bits after the source MAC address. The VLAN field is defined as 4 bytes in IEEE802.3. The first two bytes is 0x8100 and the last two bytes is VLAN label, as shown in Figure4-14. Figure4-14 VLAN Tagged Frame Reception

##

#### **Receiving MAC Control Frame**

When IP receives a MAC Control frame, it indicates that this frame is a MAC Control frame in rx\_statistics\_vector . MAC Control frame is a frame with L/T field of 0x8808 . When the L/T field is 0x8808, this frame is the MAC Control frame, which is defined in IEEE802.3.

#### **Reception when Ethernet line is abnormal**

Single-byte frame may occur on line in the event of an abnormal Ethernet line or a half-duplex collision. At this moment, the first rx\_mac\_valid and rx\_mac\_last of the user-side interface will be both 1, that is, after receiving a byte, the frame ends. The user application program needs to handle the occurrence of such an exception.

#### **Reception Statisitics**

Statistics of reception frames are output at rx\_statistics\_vector signal. When rx\_statistics\_valid is 1, it indicates that rx\_statistics\_vector is valid, and rx\_statistics\_vector indicates the statistical information of just received frames. The timing sequence is shown in Figure4-15. The bit definition of rx\_statistics\_vector is shown in Table 4-1

#### **Figure4-15 Reception Statistics**

| Location | Name                  | Description                                                                        |

|----------|-----------------------|------------------------------------------------------------------------------------|

| 26       | RX Alignment Error    | If the received frame is not an integer multiple of bytes, set 1.                  |

| 25       | RX Length Error       | If the received frame length does not meet the standard, set 1                     |

| 24       | RX FCS Error          | If the received frame has an FCS error, set 1                                      |

| 23       | RX_ER Error           | If the MAC interface RX_ER signal is valid in the process of reception, set 1      |

| 22       | RX Collision Error    | In half duplex mode, if a collision<br>occurs during the frame reception, set<br>1 |

| 21:6     | RX Frame Length       | The length of received frame, including FCS field                                  |

| 5        | RX Flow Control Frame | In full duplex mode, if the received frame is a flow control frame, set 1          |

| 4        | RX MAC Control Frame  | If the received frame is a MAC Control frame, set 1                                |

| 3        | RX VLAN Frame         | If the received frame is a VLAN frame, set 1                                       |

| 2        | RX Multicast Frame    | If the received frame is a multicast frame, set 1                                  |

| 1        | RX Broadcast Frame    | If the received frame is a broadcast frame, set 1                                  |

| 0        | RX Unicast Frame      | If the received frame is a unicast frame, set 1                                    |

Table 4-1 Rx\_Statistics\_Vector Bit Definition

#### **4.3.2 Ethernet Frame Transmission**

Sending Ethernet frames is the process of converting user interface data to MAC interface data. All received signals are synchronized with tx\_mac\_clk.

#### **Normal Frame Reception**

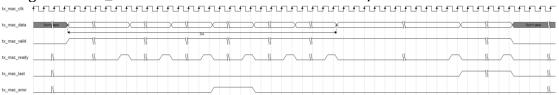

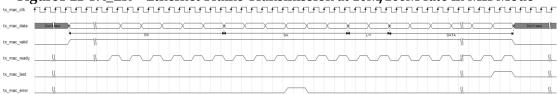

Figure 4-16 shows the normal Ethernet frame transmission process at 1000M rate.

Figure4-17 shows the normal Ethernet frame transmission process at a rate of 10M/100M in RGMII. mode. In RGMII mode, tx\_mac\_clk is 125MHz. At a rate of 10M, tx\_mac\_ready is valid for every 100 periods; At a rate of 100M, tx\_mac\_ready is valid for every 10 periods.

Figure 4-18 shows the normal Ethernet frame transmission process at a rate of 10M/100M in MII mode.

During the entire frame transmission process, tx\_mac\_valid must remain at 1 until the end of the frame. When tx\_mac\_ready and tx\_mac\_last are both 1, tx\_mac\_data is transmitted in this period and is the last byte of the Ethernet frame for that frame. It should be noted that there is no buffer in the IP to cache the transmitted Ethernet frames. Therefore, when the first byte starts to be transmitted, the user needs to prepare subsequent bytes and assign to tx\_mac\_data in time when tx\_mac\_ready is 1 until the entire frame is transmitted.

#### Figure4-16 Normal Ethernet Frame Transmission at 1000M Rate

| tx_mac_clk   |            |          |   | Ţ | ~ |       |   | ſ      | ſ      | 1 | ſ |   | <u>_</u> | ſ      | 1 | <u>_</u> | ſ | ţ.     | <u></u> | ff     | Ţ         | 1        | Ц | Ţ | Ъf          | 7     | Ţ      |   |

|--------------|------------|----------|---|---|---|-------|---|--------|--------|---|---|---|----------|--------|---|----------|---|--------|---------|--------|-----------|----------|---|---|-------------|-------|--------|---|

| tx_mac_data  | Don't care | s        |   |   | 1 | <br>× | × | $\sim$ | $\sim$ |   | × | × | $\sim$   | $\sim$ |   | $\sim$   | × | $\sim$ | ×       | $\sim$ | $\square$ |          | X |   | $ \supset $ | Don't | care ( | I |

| tx_mac_valid | (          | <u>%</u> | — |   | 5 | DA    |   |        |        |   | - |   |          | SA     |   |          | M | UT     | M       |        |           | DATA     |   |   | -           |       |        |   |

| tx_mac_ready |            |          |   |   | 1 | <br>  |   |        |        |   |   |   |          |        |   |          |   |        |         |        |           | <u> </u> |   |   | _           |       |        |   |

| tx_mac_last  |            | <u> </u> |   |   |   |       |   |        |        |   |   |   |          |        |   |          |   |        |         |        |           |          |   |   | _           |       |        |   |

| tx_mac_error | (          | <u> </u> |   |   |   |       |   |        |        |   |   |   |          |        |   |          |   |        |         |        |           |          |   |   |             |       |        |   |

#### Figure4-17 In RGMII Mode Normal Ethernet Frame Transmission at 10M/100M Rate

|              | 0          |         |             |      |      |             |      |        |          | ,      |            |

|--------------|------------|---------|-------------|------|------|-------------|------|--------|----------|--------|------------|

| tx_mac_clk   | fifter.    | กกกก    | <u>nnnn</u> | กกกก | กกกก | <u>fift</u> | եեեե | AAAAAA | ւրեւելել | กกกกกก | กกกกกก     |

| tx_mac_data  | Don'i sare | <u></u> |             |      |      | I_          |      | X      | <u> </u> | X1[    | Don't care |

| tx_mac_valid |            | 1       | 1           | 11   | 1    | 1           | 5    |        |          | 11     |            |

| tx_mac_ready |            | 55      |             |      | !L   |             |      |        |          |        | lL         |

| tx_mac_last  | <u>I</u> [ |         |             |      |      |             |      |        |          |        |            |

| tx_mac_error |            |         |             |      |      |             |      |        |          |        | <u>s</u>   |

#### Figure4-18 In MII Mode Normal Ethernet Frame Transmission at 10M/100M Rate

| _mac_clk | + | L† | L† | L† | Lt | Lt | Lt | Lt | 1 | 1 | 14 | t L | t L | t L | t L | tι | 1 L | _† | <u>+</u> | _† | <u>+</u> | Lt. | L† | Lt. | L† | L† | Lt. | L† | L† | Lt | L† | Lt | Lt | · Lt | Lt | Ŀt | 1 | Ŀt | Ŀt | Lt | Lt | Lt | Lt | Ŀt | Ŀt | Ŀt | Lt | Lt | Lt | Ŀŧ | Lt | Lt |  |

|----------|---|----|----|----|----|----|----|----|---|---|----|-----|-----|-----|-----|----|-----|----|----------|----|----------|-----|----|-----|----|----|-----|----|----|----|----|----|----|------|----|----|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--|

|          |   |    |    |    |    |    |    |    |   |   |    |     |     |     |     |    |     |    |          |    |          |     |    |     |    |    |     |    |    |    |    |    |    |      |    |    |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |  |

|          |   |    |    |    |    |    |    |    |   |   |    |     |     |     |     |    |     |    |          |    |          |     |    |     |    |    |     |    |    |    |    |    |    |      |    |    |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |  |

|          |   |    |    |    |    |    |    |    |   |   |    |     |     |     |     |    |     |    |          |    |          |     |    |     |    |    |     |    |    |    |    |    |    |      |    |    |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |  |

|          |   |    |    |    |    |    |    |    |   |   |    |     |     |     |     |    |     |    |          |    |          |     |    |     |    |    |     |    |    |    |    |    |    |      |    |    |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |  |

|          |   |    |    |    |    |    |    |    |   |   |    |     |     |     |     |    |     |    |          |    |          |     |    |     |    |    |     |    |    |    |    |    |    |      |    |    |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |  |

| tx_mac_data  | Don't care | () | X_ | X      |     | xx      |   | XX_ | X  | XX | ××  | X   |      | X Don't care |  |

|--------------|------------|----|----|--------|-----|---------|---|-----|----|----|-----|-----|------|--------------|--|

| tx_mac_valid |            | 1  |    | DA     |     |         | * |     | SA |    | L/T | *4  | DATA | *            |  |

| tx_mac_ready |            |    |    | $\sim$ | ~   |         | ~ |     |    |    |     | ~~~ |      |              |  |

| tx_mac_last  |            |    |    |        |     |         |   |     |    |    |     |     |      |              |  |

| tx_mac_error |            |    |    |        |     |         |   |     |    |    |     |     |      |              |  |

|              | ייע דיו    |    |    |        | . т | • • • • | • | •   |    |    |     |     |      |              |  |

#### TX\_ER Error Frame Transmission

During the transmission process, when tx\_mac\_error and tx\_mac\_ready are both 1, it indicates that there is an error in the current transmitted frame. IP will transmit TX\_ER transmitted data error indication on the MAC interface.

Figure4-19 shows the transmission process of TX\_ER Ethernet frame at a rate of 1000M.

Figure4-20 shows the transmission process of TX\_ER Ethernet frame at a rate of 10M/100M in RGMII mode.

Figure4-21 shows the transmission process of TX\_ER Ethernet frame at a rate of 10M/100M in MII mode.

#### Figure4-19 TX\_ER for Ethernet Frame Transmission at 1000M rate

| tx_mac_clk   |            | 1       |    |              |        |   | ſ |      |   |        |              |   | <u>_</u> |        |   | ſĿſ           |   |               |     |        |          | 1      |

|--------------|------------|---------|----|--------------|--------|---|---|------|---|--------|--------------|---|----------|--------|---|---------------|---|---------------|-----|--------|----------|--------|

| tx_mac_data  | Don't care | 1       | ×— | <br>35       | $\sim$ | × |   | ×    | × | $\sim$ | ×            | × | ×        | $\sim$ | × | )<br>()<br>() | × | $\rightarrow$ |     | $\sim$ | Dor      | t care |

| tx_mac_valid |            | //      | —  | \$\$         | DA     |   |   |      | - |        | SA           |   |          | UT     |   | DATA          |   |               | FCS |        | <u> </u> |        |

| tx_mac_ready |            |         |    | <br><u>%</u> | <br>   |   |   |      |   |        |              |   |          |        |   | 1             |   |               |     |        |          |        |

| tx_mac_last  |            | <u></u> |    |              |        |   |   | <br> |   |        | <br>         |   |          |        |   | <u> </u>      |   |               |     |        | <u> </u> |        |

| tx_mac_error |            | <u></u> |    |              | <br>   |   |   | <br> |   |        | <br><u> </u> |   |          |        |   |               |   |               |     |        |          |        |

Figure4-20 TX\_ER Ethernet Frame Transmission at 10M/100M rate in RGMII Mode

#### Figure4-21 TX\_EREthernet Frame Transmission at 10M/100M rate in MII Mode

#### **Transmission Frame FCS Forward**

When the user sets IP to be transmission FCS Forward mode, the IP will not automatically add FCS field. After the user transmits the DATA field, the FCS field needs to be calculated and added manually, as is shown in Figure4-22 and Figure4-23.

Figure4-23 Enabling FCS Forward Ethernet Frames Transmission at 1000M rate in MII Mode

#### Transmission in half duplex mode

In half duplex mode, IP indicates the transmission state through tx collision and tx retransmit signal if the user does not detect any collision during the transmission. The Ethernet frames can be transmitted according to the above full duplex transmission process. If the user detects a collision during the transmission, the following should be done to ensure the correct transmission of data. When the user detects the tx collision to be1, it means that there is a collision on the line. The user must immediately set tx\_mac\_valid to 0 when he detects the tx\_collision to be 1, so as to end the Ethernet frame transmission. With the detection of tx collision to be1, and if tx retransmit is 1, it indicates that the collision is within a reasonable range, and the user can decide whether to retransmit the frame. If the user is ready to retransmit the frame, please set tx\_mac\_valid to 1 within 5 periods to prepare for the retransmission of the frame. If the user prepares to abort to retransmit the frame, please set tx mac valid to 1 after 5 periods to prepare for the next frame transmission. With the detection of tx\_collision to be1, and if tx\_retransmit is 0, it indicates that the collision is not within a reasonable range (a frame with more than 16 collisions, or collisions occurring after 64 bytes having been sent), then the user needs to abort the transmission of this frame.

Figure 4-24 shows the retransmission process when a collision occurring.

Figure 4-25 and Figure 4-26 show respectively the non-retransmission process when a collision occurring.

#### Figure4-24 Retransmission in Case of Collision

#### **Transmission Statisitics**

Transmission frames statistics is output at tx\_statistics\_vector signal. When tx\_statistics\_valid is 1, it indicates that tx\_statistics\_vector is valid, and at this point tx\_statistics\_vector indicates the statistics information of just transmitted frames. The timing sequence is shown in Figure4-27. The bit definition of tx\_statistics\_vector is shown in Table 4-2..

| Location | Name                  | Description                                                                                                                                                                                                       |

|----------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28       | TX Collision          | In half duplex mode, if a collision occurs when this frame is transmitted, set1.                                                                                                                                  |

| 27:24    | TX Attempts           | In half duplex mode, the number of<br>times this frame was attempted to be<br>transmitted, 0 represents the first<br>transmission;1 represents the second<br>transmission;15 represents the 16th<br>transmission. |

| 23       | Excessive Collision   | In half duplex mode, if the frame is on<br>the 16th attempt to transmit, collision<br>occurring, set 1.                                                                                                           |

| 22       | Late Collision        | If the collision occurs after 64 bytes having been transmitted, set 1                                                                                                                                             |

| 21:6     | TX Frame Length       | Transmission frame length, including FCS field                                                                                                                                                                    |

| 5        | TX Flow Control Frame | In full duplex mode, if the IP is configured to transmit a flow control frame, set 1                                                                                                                              |

| 4        | TX MAC Control Frame  | If the transmission frame is MAC<br>Control frame, set 1                                                                                                                                                          |

| 3        | TX VLAN Frame         | If the transmission frame is VLAN frame, set 1                                                                                                                                                                    |

| 2        | TX Multicast Frame    | If the transmission frame is Multicast frame, set 1                                                                                                                                                               |

| 1        | TX Broadcast Frame    | If the transmission frame is Broadcast frame, set 1                                                                                                                                                               |

| 0        | TX Unicast Frame      | If the transmission frame is Unicastt frame, set 1                                                                                                                                                                |

Table 4-2 Bit Definition of tx\_statistics\_vector

#### **4.3.3 Flow Control Function**

IP supports the Flow Control function in full duplex mode. In full duplex mode, user can configure IP to transmit or receive Pause frame to achieve flow control.

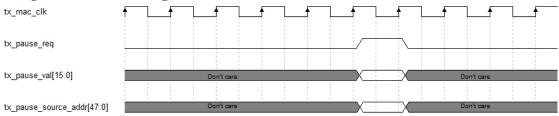

#### **Transmitting Pause Frame**

Users can set the tx\_pause\_req signal to 1 to transmit a pause frame. The value of tx\_pause\_val is inserted into the parameter field of the pause frame to calculate the pause time. Tx\_pause\_source\_addr is transmitted as the source MAC address for the pause frame, and the transmission order is from the low to high bytes.

#### Figure4-28Transmitting Pause Frame

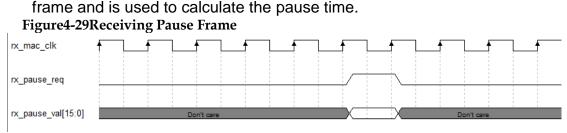

#### **Receiving Pause Frame**

When the IP receives a pause, it sets the rx\_pause\_req signal to 1. The value of rx\_pause\_val is the parameter field that receiving the pause

#### 4.3.4 FCS Forward Function

IP supports FCS Forward function that configures transmission and reception respectively.

#### **Receiving FCS Forward function**

When the user disables the FCS Forward function, the FCS field will not be output to the user side. IP automatically verifies the FCS field and its results will be output to rx\_statistics\_vector corresponding field. When the user enables the FCS Forward function, the FCS field will be output to the user side. IP still automatically verifies the FCS field and its results will be output to rx\_statistics\_vector corresponding field.

#### **Transmitting FCS Forward Function**

When the user disables the FCS Forward function, the user does not need to calculate and transmit the FCS field. The IP calculates the FCS field and adds it to the Ethernet frame automatically. When the user enables the FCS Forward function, the user calculates the FCS field and transmits it to the IP on the user side.

#### 4.3.5 PAD Function

When the user disables the FCS Forward function, if the frame transmitted by the user to IP is less than 60 bytes (excluding FCS), IP will automatically complement 0 to 60 bytes then add FCS field to ensure that the Ethernet frame transmitted meets the requirement of minimum 64 bytes. When the user enables the FCS Forward function, the IP will not automatically complement 64 bytes, and the actual transmitted data and length are completely determined by the user.

#### 4.3.6 Transmitting IFG Setting Function

When the IP is in full duplex mode, the user can set the minimum IFG for the Ethernet transmission. When the IP is in half duplex mode, the minimum IFG transmission set by user is ignored, and the minimum IFG is still 12 bytes.

When the user disables the IFG function, IP transmits a minimum IFG of 12 bytes, or 96 bit. When the user enables the IFG function, IP determines the minimum IFG based on the user settings. If the minimum IFG set by the user is less than 8 bytes, the actual minimum IFG of IP is 8 bytes; If the user sets the minimum IFG to be greater than or equal to 8 bytes, the IP's actual minimum IFG is the value set by the user. The minimum IFG can be set to a maximum of 255 bytes.

#### 4.3.7 Jumbo Setting Function

IP supports the Jumbo function. When the user disable the Jumbo function, IP judges that the correct Ethernet frame length was 64 bytes to 1518 bytes (non-vlan frames) or 64 bytes to 1522 bytes (VLAN frames). If the Ethernet frames received are not within the above range, rx\_mac\_error

will indicate that there is an Error on this frame and RX Length Error is 1 in rx\_statistics\_vector. When the user enables the Jumbo function, IP judges an error only if the Ethernet frames received are smaller than 64 bytes.

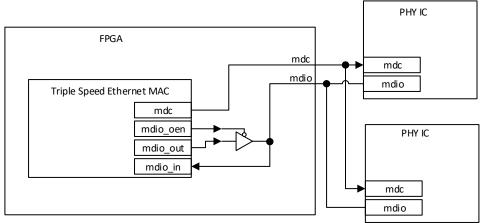

#### 4.3.8 Management Function

IP provides users with MIIM interface to facilitate them to configure PHY chip registers through MDC and MDIO.

MDC clock comes from CLK input clock frequency division. Users need to configure frequency divider according to CLK input clock to make MDC clock frequency meet the requirements of PHY chip. Please refer to table 6-1 for configuration method. Connection between MDC and MDIO is shown in Figure4-29.

Figure4-30 Schematic Diagram of Connection between mdc and mdio

Mdio connection refers to verilog as follows: assign mdio\_in = mdio; assign mdio = (!mdio oen) ? mdio out : 1'bz;

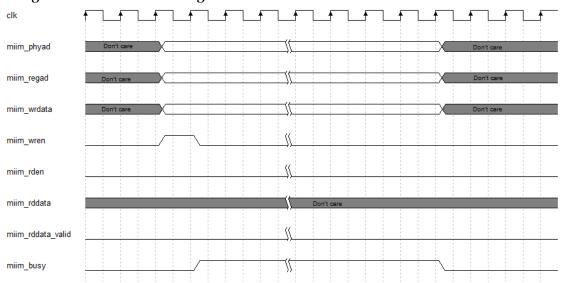

All miim interface signals are synchronized with the CLK clock.

To write, the user needs to set miim\_wren to 1 one period. IP will raise miim\_busy, indicating that the miim bus is doing the write. When miim\_busy is 0 again, it indicates this write has ended. And the user is ready for the next read or write. The miim\_phyad, miim\_regad, and miim\_wrdata signals are ready on the bus when miim\_wren is 1, and it remains unchanged when miim\_wren is 1. The write timing of miim is shown in Figure4-30.

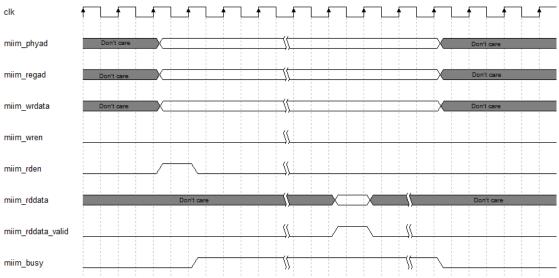

Figure4-31 The Write Timing of miim

To read, the user need to set miim\_rden to 1 one period. IP will raise miim\_busy, indicating that the miim bus is doing the read. When miim\_busy is 0 again, it indicates that this read has ended and the user can do the next read or write. The miim\_phyad and miim\_regad signals are ready on the bus when miim\_rden is 1, and it remains unchanged when miim\_busy is 1. During the read, the user monitors the miim\_rddata\_valid signal. When miim\_rddata\_valid is 1, the user can sample the value of this read in the miim\_rddata signal. The read timing of Miim is shown in Figure4-31. Figure4-32 Read Timing of Miim

## **5**<sub>Port List</sub>

The IO port for Gowin Triple Speed Ethernet MAC IP is shown in Table 5-1.

| Signal                 | <u>-1/0</u> | Data     | Gowin Triple Speed Ethernet MAC IP Description                                                                                                                                                                                                       |

|------------------------|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal                 | 1/0         | Width    | Description                                                                                                                                                                                                                                          |

| 125MHz clock input     |             | , that i |                                                                                                                                                                                                                                                      |

| gtx_clk                | input       | 1        | 125M clock input. When IP uses RGMII or GMII interface,                                                                                                                                                                                              |

| -                      |             |          | 125MHz clock should be input                                                                                                                                                                                                                         |

| <b>RGMII Interface</b> |             |          |                                                                                                                                                                                                                                                      |

| rgmii_rxc              | input       | 1        | RGMII receives clock                                                                                                                                                                                                                                 |

| rgmii_rx_ctl           | input       | 1        | RGMII receives control                                                                                                                                                                                                                               |

| rgmii_rxd              | input       | 4        | RGMII/MII receive data                                                                                                                                                                                                                               |

| rgmii_txc              | output      | 1        | RGMII receives data                                                                                                                                                                                                                                  |

| rgmii_tx_ctl           | output      | 1        | RGMII transmits control                                                                                                                                                                                                                              |

| rgmii_txd              | output      | 4        | RGMII transmits data                                                                                                                                                                                                                                 |

| GMII Interface         |             |          |                                                                                                                                                                                                                                                      |

| gmii_rx_clk            | input       | 1        | GMII receives clock                                                                                                                                                                                                                                  |

| gmii_rx_dv             | input       | 1        | GMII receives enable                                                                                                                                                                                                                                 |

| gmii_rxd               | input       | 8        | GMII receives data                                                                                                                                                                                                                                   |

| gmii_rx_er             | input       | 1        | GMII receives error                                                                                                                                                                                                                                  |

| gmii_gtx_clk           | output      | 1        | GMII receives clock                                                                                                                                                                                                                                  |

| gmii_tx_en             | output      | 1        | GMII transmits enable                                                                                                                                                                                                                                |

| gmii_txd               | output      | 8        | GMII transmits data                                                                                                                                                                                                                                  |

| gmii_tx_er             | output      | 1        | GMII transmits error                                                                                                                                                                                                                                 |

| MII Interface          |             |          |                                                                                                                                                                                                                                                      |

| mii_rx_clk             | input       | 1        | MII receives clock                                                                                                                                                                                                                                   |

| mii_rx_dv              | input       | 1        | MII receives enable                                                                                                                                                                                                                                  |

| mii_rxd                | input       | 4        | MII receives data                                                                                                                                                                                                                                    |

| mii_rx_er              | input       | 1        | MII receives error                                                                                                                                                                                                                                   |

| mii_tx_clk             | input       | 1        | MII transmits clock                                                                                                                                                                                                                                  |

| mii_tx_en              | output      | 1        | MII transmits enable                                                                                                                                                                                                                                 |

| mii_txd                | output      | 4        | MII transmits data                                                                                                                                                                                                                                   |

| mii_tx_er              | output      | 1        | MII transmits error                                                                                                                                                                                                                                  |

| mii_col                | input       | 1        | MII collision signal                                                                                                                                                                                                                                 |

| mii_crs                | input       | 1        | MII carrier signal                                                                                                                                                                                                                                   |

| Interface Status Conf  | igure       |          |                                                                                                                                                                                                                                                      |

| speedis1000            | input       | 1        | Selecting signal based on Ethernet rate. when IP works in<br>RGMII or GMII/MII mode, configure IP to work at 1000M<br>rate or 10M/100M rate:<br>1:1000M<br>0:10M/100M                                                                                |

| speedis10              | input       | 1        | Selecting signal based on Ethernet rate. When IP works in<br>RGMII mode and speedis1000 is 0, the configured IP<br>works at 10M or 100M rate:<br>1:10M<br>0:100M<br>It is should be noted when speedis1000 is1, this<br>configuration pin is ignored |

| duplex_status          | input       | 1        | Ethernet duplex mode configures signal. When IP works in<br>RGMII, MII or GMII/MII mode, configure IP working duplex<br>mode :<br>1:half duplex<br>0:full duplex                                                                                     |

| Reset                  |             | 1        |                                                                                                                                                                                                                                                      |

| rstn                   | input       | 1        | IP Reset signal, active low                                                                                                                                                                                                                          |

| User Interface         |             | T        |                                                                                                                                                                                                                                                      |

| rx_mac_clk             | output      | 1        | The user side receives clock                                                                                                                                                                                                                         |

| rx_mac_valid           | output      | 1        | The user side receives enable                                                                                                                                                                                                                        |

#### Table 5-1 The IO port for Gowin Triple Speed Ethernet MAC IP

| Signal                                                                                           | I/O    | Data<br>Width | Description                                                      |

|--------------------------------------------------------------------------------------------------|--------|---------------|------------------------------------------------------------------|

| rx_mac_data                                                                                      | output | 8             | The user side receives data                                      |

| rx_mac_last                                                                                      | output | 1             | The user side receives the indication of last byte               |

| rx_mac_error                                                                                     | output | 1             | The user side receives the indication of error frame             |

| rx_statistics_valid                                                                              | output | 1             | The user side receives the indication of valid statistics        |

| rx_statistics_vector                                                                             | output | 27            | The user side receives statistics                                |

| tx_mac_clk                                                                                       | output | 1             | The user side transmits clock                                    |

| tx mac valid                                                                                     | input  | 1             | The user side transmits enable                                   |

| tx_mac_data                                                                                      | input  | 8             | The user side transmits data                                     |

| tx_mac_last                                                                                      | input  | 1             | The user side transmits the indication of last byte              |

| tx_mac_error                                                                                     | input  | 1             | The user side transmits the indication of error frame            |

|                                                                                                  |        | 1             | The user side transmits a handshake signal. It indicates         |

| tx_mac_ready                                                                                     | output |               | that tx_mac_data is received with a value of 1.                  |

| tx_collision                                                                                     | output | 1             | The user side transmits the line collision indicator signal.     |

|                                                                                                  |        |               | When the value is 1, it indicates that there is a line collision |

|                                                                                                  |        |               | in this transmission and the user needs to end this              |

|                                                                                                  |        |               | transmission immediately. This signal is valid only in half      |

|                                                                                                  |        |               | duplex                                                           |

| tx_retransmit                                                                                    | output | 1             | The user side will transmit a retransmission indicator           |

|                                                                                                  |        |               | signal, which appears with tx_collision at the same time,        |

|                                                                                                  |        |               | and the value of 1 means that this frame needs to be             |

|                                                                                                  |        | -             | retransmitted. This signal is valid only in half duplex          |

| tx_statistics_valid                                                                              | output | 1             | The user side transmits the indication of valid statistics       |

| tx_statistics_vector                                                                             | output | 29            | The user side transmits statistics                               |

| IP Configure                                                                                     | 1      | I             |                                                                  |

| rx_fcs_fwd_ena                                                                                   | input  | 1             | Receiving FCS Forward function:                                  |

|                                                                                                  |        |               | 1:Enable receiving FCS Forward function                          |

|                                                                                                  |        |               | 0:Disable receiving FCS Forward function                         |

| rx_jumbo_ena                                                                                     | input  | 1             | Receiving Jumbo function:                                        |

|                                                                                                  |        |               | 1:Enable receiving Jumbo function                                |

|                                                                                                  |        |               | 0:Disable receiving Jumbo function                               |

| rx_pause_req                                                                                     | output | 1             | Receiving the signal of pause frame                              |

| rx_pause_val                                                                                     | output | 16            | C                                                                |

| tx_fcs_fwd_ena                                                                                   | input  | 1             | Transmitting FCS Forward Function                                |

|                                                                                                  |        |               | 1:Enable receiving FCS Forward function                          |

|                                                                                                  |        |               | 0:Disable receiving FCS Forward function                         |

| tx_ifg_delay_ena                                                                                 | input  | 1             | Transmitting the minimum IFG configuration enable:               |

|                                                                                                  |        |               | 1: Enable the minimum IFG configuration                          |

|                                                                                                  |        |               | 0: Disable minimum IFG configuration, and the default            |

|                                                                                                  |        |               | minimum IFG is 12 bytes                                          |

| tx_ifg_delay                                                                                     | input  | 8             | Transmitting minimum IFG:                                        |

|                                                                                                  |        |               | When tx_ifg_delay_ena is 1, the minimum IFG transmitted          |

|                                                                                                  |        |               | by IP is determined by tx_ifg_delay. When tx_ifg_delay is        |

|                                                                                                  |        |               | less than 8, the minimum IFG is 8; When tx_ifg_delay is          |

|                                                                                                  |        |               | greater than or equal to 8, the minimum IFG is set by the        |

|                                                                                                  |        |               | user.                                                            |

|                                                                                                  |        |               | When tx_ifg_delay_ena is 0, this setting is invalid              |

| tx_pause_req                                                                                     | input  | 1             | Transmitting enable signal of pause frame                        |

| tx_pause_val                                                                                     | input  | 16            | Transmitting the parameter field of pause frame, which           |

|                                                                                                  |        | 10            | means the counterpart needs to pause time.                       |

| tx_pause_source_add                                                                              | input  | 48            | Transmitting the source address of pause frame.                  |

| r<br>Managament Interface                                                                        |        |               |                                                                  |

| Management Interface           clk         input         1         Management module clock input |        |               |                                                                  |

|                                                                                                  | input  | 1             | Management module clock input                                    |

| miim_phyad                                                                                       | input  | 5             | PHY address                                                      |

| Signal            | I/O    | Data<br>Width | Description                                                       |

|-------------------|--------|---------------|-------------------------------------------------------------------|

| miim_regad        | input  | 5             | Address                                                           |

| miim_wrdata       | input  | 16            | Write data                                                        |

| miim_wren         | input  | 1             | Write enable                                                      |

| miim_rden         | input  | 1             | Read enable                                                       |

| miim_rddata       | output | 16            | Read data                                                         |

| miim_rddata_valid | output | 1             | Read data valid                                                   |

| miim_busy         | output | 1             | MIIM interface status indicator:<br>1: Reading/Writing<br>0: Idle |

| mdc               | output | 1             | MDC clock                                                         |

| mdio_in           | input  | 1             | MDIO input                                                        |

| mdio_out          | output | 1             | MDIO output                                                       |

| mdio_oen          | output | 1             | MDIO output enable                                                |

# **6**Parameter Configuration

Users are required to configure the various static and timing parameters of the Gowin Triple Speed Ethernet MAC according to the design requirements. Refer to Table 6-1.

| Name               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Options                          |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Interface          | Interface Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RGMII,GMII,MII,GMII/MII          |

| RGMII Input Delay  | When using the RGMII interface, this<br>option is used to adjust the Delay value<br>of the input data RXD IODELAY. If the<br>value adds 1 each time, it means the<br>RXD IODELAY in the FPGA increases<br>0.025ns delay; If the value reduces 1<br>each time, it means the RXD IODELAY in<br>the FPGA decreases 0.025ns delay.<br>When the input clock and data are<br>aligned along, this option is<br>recommended to be set to 100, that is,<br>RXD IODELAY in the FPGA is set to<br>2.5ns delay, at which time RXCLK<br>samples RXD correctly. | User input, range from 0 to 127. |