## Gowin SPDIF Receiver IP

# 用户指南

IPUG548-1.11,2021-04-22

#### 版权所有 © 2021 广东高云半导体科技股份有限公司

GO₩INā云, Gowin, 高云均为广东高云半导体科技股份有限公司注册商标, 本手册中提到的 其他任何商标, 其所有权利属其拥有者所有。未经本公司书面许可, 任何单位和个人都不得 擅自摘抄、复制、翻译本文档内容的部分或全部, 并不得以任何形式传播。

#### 免责声明

本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止发言或其它方式授予任何知识产权许可。除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。高云半导体不承诺对这些文档进行适时的更新。

## 版本信息

| 日期         | 版本   | 说明             |

|------------|------|----------------|

| 2019/05/10 | 1.0  | 初始版本。          |

| 2020/07/23 | 1.1  | 增加 SPDIF 恢复时钟。 |

| 2021/04/22 | 1.11 | 更新 2.4 节信号定义。  |

# 目录

| 月 | 录                                       | İ          |

|---|-----------------------------------------|------------|

| 图 | <br> 目录                                 | <b>i</b> i |

|   | 目录                                      |            |

| • | 关于本手册                                   |            |

| 1 | × · · · · · · · · · · · · · · · · · · · |            |

|   | 1.1 手册内容                                |            |

|   | 1.2 相关文档                                |            |

|   | 1.3 术语、缩略语                              |            |

|   | 1.4 技术支持与反馈                             |            |

| 2 | 功能描述                                    | 2          |

|   | 2.1 概述                                  | 2          |

|   | 2.1.1 特性                                | 2          |

|   | 2.1.2 性能参考                              | 2          |

|   | 2.2 系统框图                                | 3          |

|   | 2.3 工作原理                                | 3          |

|   | 2.3.1 实现框图                              |            |

|   | 2.3.2 SPDIF 帧结构                         |            |

|   | 2.3.3 BMC 编码                            |            |

|   | 2.3.4 控制器工作过程                           |            |

|   | 2.4 信号定义                                |            |

|   | 2.4.1 用户逻辑侧信号                           |            |

|   | 2.4.2 接收侧信号                             |            |

|   | 2.5 参数介绍                                |            |

|   | 2.6 接口时序                                |            |

| 2 | 应用举例                                    |            |

| ၁ |                                         |            |

|   | 3.1 概述                                  |            |

|   | 3.2 应用框图                                |            |

|   | 3.3 GUI 调用                              | 7          |

## 图目录

| 图 2-1 系统框图                    | 3 |

|-------------------------------|---|

| 图 2-2 实现框图                    |   |

| 图 2-3 帧格式                     |   |

| 图 2-4 子帧格式                    |   |

| 图 2-5 用户逻辑时序                  |   |

| 图 3-1 应用框图                    |   |

| 图 3-2 工程界面                    |   |

| 图 3-3 IP Core Generator 界面    |   |

| 图 3-4 例化 SPDIF_RX_Top         |   |

| El 0 1 1/1/10 01 211 -107-106 | 0 |

## 表目录

| 表 1-1 术语、缩略语  | 1 |

|---------------|---|

| 表 2-1 性能参考    |   |

| 表 2-2 用户逻辑侧信号 |   |

| 表 2-3 接收侧信号   | 6 |

| 表 2-4 GUI 参数  |   |

IPUG548-1.11 iii

1 关于本手册 1.1 手册内容

# 1 关于本手册

## 1.1 手册内容

Gowin SPDIF Receiver IP 用户手册主要包括功能特征、整体框图、工作原理、信号定义、参数介绍、接口时序、GUI 调用等,旨在帮助用户快速了解高云半导体 SPDIF Receiver IP 的产品特性和使用方法,加速用户产品开发。

## 1.2 相关文档

通过登录高云半导体网站 <u>www.gowinsemi.com.cn</u> 可以下载、查看以下相关文档:

- <u>DS100</u>, GW1N 系列 FPGA 产品数据手册

- DS226, GW2AR 系列 FPGA 产品数据手册

- DS102, GW2A 系列 FPGA 产品数据手册

## 1.3 术语、缩略语

表 1-1 中列出了本手册中出现的相关术语、缩略语及相关释义。

#### 表 1-1 术语、缩略语

| 术语、缩略语 | 全称                                    | 含义           |

|--------|---------------------------------------|--------------|

| FPGA   | Field Programmable Gate Array         | 现场可编程门阵列     |

| SPDIF  | Sony/Philips Digital Interface Format | 索尼/飞利浦数据接口格式 |

## 1.4 技术支持与反馈

高云半导体提供全方位技术支持,在使用过程中如有任何疑问或建议,可直接与公司联系:

网址: www.gowinsemi.com.cn

E-mail: support@gowinsemi.com

Tel: +86 755 8262 0391

IPUG548-1.11 1(9)

2 功能描述 2.1 概述

# 2 功能描述

## 2.1 概述

SPDIF(Sony/Philips Digital Interface Format)是一种数字音频传输接口,普遍使用光纤和同轴线输出,将音频信号输出到解码器上,能保持高保真度的输出结果,广泛应用在 DTS(Digital Theatre System,数字化影院系统)。

为了更好地服务 FPGA 用户,降低用户的系统开发难度,提高产品开发速度,设计一款低功耗通用 SPDIF Receiver 控制器,实现 SPDIF 接口协议及 BMC 编码等功能。

SPDIF Receiver 控制器通过软件界面调用后,可通过 Gowin 软件综合、布局布线适用到高云所有 FPGA 产品。

## 2.1.1 特性

- 控制器输入工作时钟速率不小于 512Fs (FS 即音频采样速率);

- 通过高速时钟异步采样全数据处理恢复语音数据和时钟;

- SPDIF 恢复时钟为控制器输入工作时钟的 1/8:

- 支持 8KHz~192KHz 采样速率;

- 支持 16bit~24bit 位宽范围取值;

- 支持 IEC60958 (SPDIF) 和 AES3 标准的 PCM 数据传输;

- 锁定时间不大于 1Fs;

- 低功耗:

- 完全可综合。

## 2.1.2 性能参考

Gowin SPDIF Receiver IP 的工作频率取决于 IP 在所选芯片中支持的最大工作频率,设计语言为 Verilog, 性能测试参考如下所示:

#### 表 2-1 性能参考

| 芯片型号                | 编程语言    | LUT4 资源 | 最大速度    |

|---------------------|---------|---------|---------|

| GW1N-LV4LQ144C6/I5  | Verilog | 330     | ≥90MHz  |

| GW2A-LV18LQ144C8/I7 | Verilog | 318     | ≥150MHz |

IPUG548-1.11 2(9)

2 功能描述 2.2 系统框图

## 2.2 系统框图

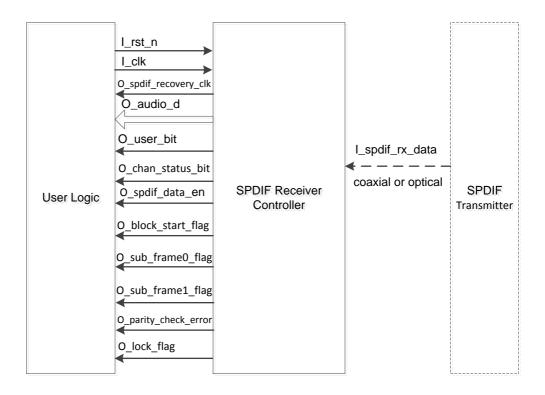

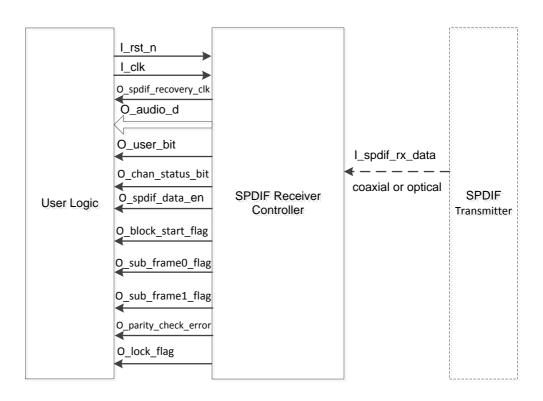

SPDIF Receiver 控制器用户逻辑侧主要包括数据、控制、时钟、复位等信号,发送端口侧仅有一路输入数据。

#### 图 2-1 系统框图

## 2.3 工作原理

## 2.3.1 实现框图

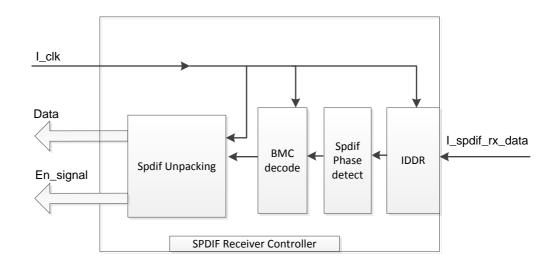

图 2-2 实现框图

IPUG548-1.11 3(9)

2 功能描述 2.3 工作原理

整个 SPDIF Receiver 控制器包括 Spdif Unpacking、BMC decode、Spdif Phase detect 、IDDR 等模块。

- Spdif Unpacking: 对接收的 spdif 数据进行拆包,并发送到用户端口;

- BMC decode:对 spdif 传输过来的数据进行解码;

- Spdif Phase detect:对 spdif 传输过来的数据进行相位检测;

- IDDR: 实现 1:2 串并转换。

#### 2.3.2 SPDIF 帧结构

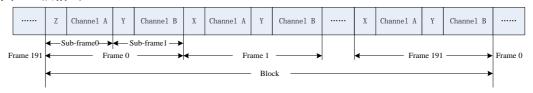

#### 图 2-3 帧格式

SPDIF 块由 192 个帧组成,每个帧由 2 个子帧组成,分为 Channel A 与 Channel B 两个声道,分别对应左右声道。子帧数据长度为 32 bit,包含帧头 (Preamble)、辅助数据(Aux. Data)、音频数据(Audio Data)以及四个位的信息与检查码。一个子帧为 4 Bytes,而一个 Frame 为 8 Bytes,而一个 Block 为 192 x 8 = 1536 Bytes。

#### 图 2-4 子帧格式

| 0 3           | 4 7       | 8   |                   | 27  | 28 | 29 | 30 | 31 |  |

|---------------|-----------|-----|-------------------|-----|----|----|----|----|--|

| Sync preamble | Auxiliary | LSB | Audio sample word | MSB | V  | U  | O  | Р  |  |

#### 1. 帧头(Sync Preamble)

主要有 X、Y、Z 三种组态,分别表示该子帧为 Channel 1、Channel 2、Block 起始。

#### 2. 辅助数据(Auxiliary)

目前比较常见的用途是当音频数据超过 20bit 取样时,这四个 bit 用来储存多出的取样 bit,比如说当要传送 24bit 取样的数据时,用来存放末四个 bit 的音频数据。

#### 3. 音频数据(Audio sample word)

存放实际的取样数据,长度为 20 bit,以 LSB 优先的方式传送,当取样低于 20 bit 时,没有用到的 LSB bits 要设定为零。

#### 4. 有效标识(Validity bit)

此位用来标识子帧内的数据是不是正确,如果设定为 0,代表此子帧内的数据是正确可被接收,反之如果此 bit 为 1,则代表接收端应该忽略此子帧。

#### 5. 用户位(User bit)

此位为用户自行定义位,每组 Sample 传送一位,直到 192 组 Sample 传完后组成 192 位的信息,两声道各自有一组 192 位的用户信息。

6. 信道状态位(Channel Status bit)

IPUG548-1.11 4(9)

2 功能描述 2.4 信号定义

此位与用户位一样,每组 Sample 传送一位,最后组成两声道各自一组 192 位的信道状态信息(Channel Status)。这个 192 位信道状态信息分为 专业(Professional)与一般家用(Consumer)两种不同的结构,以第一个位决定,设为 1 时为 Professional 模式,设为 0 时为 Consumer 模式。

#### 7. 同位检查位(Parity bit)

同位检查是用来判别是否有奇数个位发生错误,是一种简便错误检查方法,使用偶位同位检查(Even Parity Check)。

### 2.3.3 BMC 编码

双相符号编码(Biphase Mark Code),简称 BMC,属于一种相位调制 (phase modulation)的编码方法,是将时钟信号和数据信号混合在一起传输的编码方法。

其原理是使用一个两倍于传输位率(bit Rate)的时钟频率作为基准,把原本一位数据拆成两部分,当数据为 1 的时,在其时钟周期内转变一次电位 (0->1 或 1->0)让数据变成两个不同电位的数据,变成 10 或 01,而当数据为 0 时则不转变电位,变成 11 或 00。同时每一个位开头的电平与前一个位结尾电平要不同,以便接收端判别每一个位的边界。

## 2.3.4 控制器工作过程

SPDIF Receiver 控制器工作机制如下所述:

- 控制器进入工作状态前,用户逻辑通过发送复位信号来初始化内部寄存器及状态机等;

- 2. 控制器会在输入时钟下对从 IDDR 接收的数据通过检测 10 或 01 跳 边沿信息来进行定时恢复:

- 3. 对相位检测模块处理后的 spdif 数据做 BMC 解码;

- 4. 按照 SPDIF 协议进行协议解析,并对数据做校验处理:

- 5. 把音频数据、User bit、Validity bit、Channel status bit 等数据及指示信号发送到用户接口。

## 2.4 信号定义

## 2.4.1 用户逻辑侧信号

表 2-2 用户逻辑侧信号

| 序号 | 信号名称                 | 方向 | 描述                     | 备注             |

|----|----------------------|----|------------------------|----------------|

| 1  | I_rst_n              | I  | 复位                     | 所有信号输          |

| 2  | I_clk                | I  | 时钟                     | 入输出方向<br>均以控制器 |

| 3  | O_spdif_recovery_clk | 0  | SPDIF 恢复时钟             | 为参考            |

| 4  | O_audio_d            | 0  | 音频数据                   |                |

| 5  | O_user_bit           | 0  | User bit 位数据           |                |

| 6  | O_chan_status_bit    | 0  | Channel Status Bit 位数据 |                |

| 7  | O_spdif_data_en      | 0  | 数据有效信号                 |                |

| 8  | O_sub_frame0_flag    | 0  | Sub Frame0 起始标志        |                |

| 9  | O_sub_frame1_flag    | 0  | Sub Frame1 起始标志        |                |

IPUG548-1.11 5(9)

2 功能描述 2.5 参数介绍

| 序号 | 信号名称                 | 方向 | 描述                       | 备注 |

|----|----------------------|----|--------------------------|----|

| 10 | O_block_start_flag   | 0  | Block 起始标志               |    |

| 11 | O_parity_check_error | 0  | 校验错误标识(高电平指示当前子帧<br>有误码) |    |

| 12 | O_lock_flag          | 0  | 锁定标识                     |    |

## 2.4.2 接收侧信号

#### 表 2-3 接收侧信号

| 序号 | 信号名称            | 方向 | 描述           | 备注                     |

|----|-----------------|----|--------------|------------------------|

| 1  | I_spdif_rx_data | I  | Spdif 传输通道数据 | 所有信号输入输出方向均以控制<br>器为参考 |

## 2.5 参数介绍

Gowin SPDIF Receiver 控制器 GUI 参数如下所示。

#### 表 2-4 GUI 参数

| 序号 | 参数名称             | 允许范围  | 默认值 | 描述         |

|----|------------------|-------|-----|------------|

| 1  | SPDIF_DATA_WIDTH | 16~24 | 24  | 音频数据输入数据宽度 |

## 2.6 接口时序

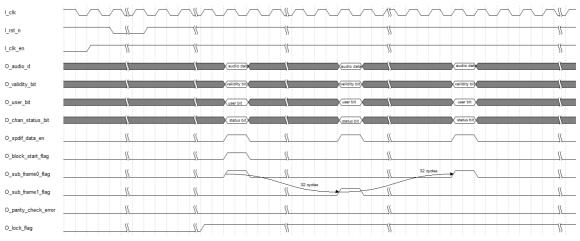

用户逻辑时序如下所示。

#### 图 2-5 用户逻辑时序

#### 注!

- 时钟使能信号使能后,需首先复位一次控制器;

- 所有输入和输出信息均与时钟上升沿对齐;

- 所有数据使能和标识信号都为一个时钟周期,且数据和数据使能对齐输出;

- O\_spdif\_recovery\_clk 时钟为输入工作时钟的 1/8。

IPUG548-1.11 6(9)

3 应用举例 3.1 概述

# **3** 应用举例

## 3.1 概述

本章主要介绍如何通过 GUI 界面设置参数、生成可用 SPDIF Receiver 控制器 Module。

## 3.2 应用框图

图 3-1 应用框图

## 3.3 GUI 调用

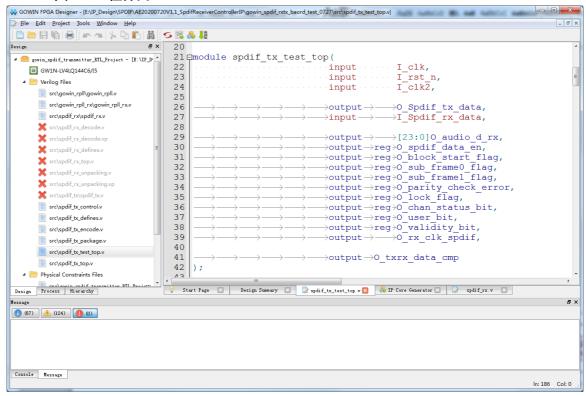

1. 启动 Gowin 云源软件后,打开工程,如图 3-2 所示:

IPUG548-1.11 7(9)

3 应用举例 3.3GUI 调用

#### 图 3-2 工程界面

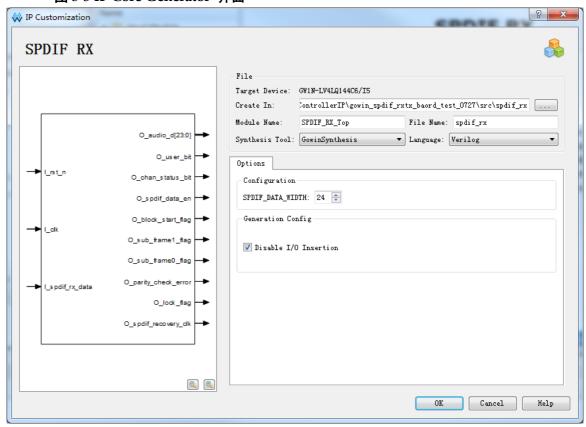

2. 在 Tools 菜单下点击"IP Core Generator",如图 3-3 所示。调用 SPDIF RX,参数默认即可,点击"OK"后生成"SPDIF RX Top Module"。

图 3-3 IP Core Generator 界面

IPUG548-1.11 8(9)

3 应用举例 3.3GUI 调用

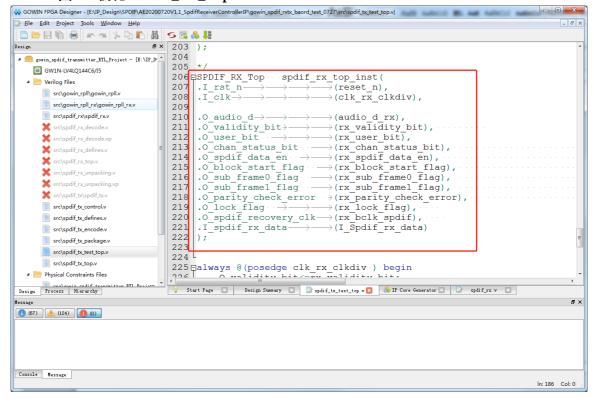

3. 在用户程序中例化 "SPDIF\_RX\_Top", 如图 3-4 所示。

#### 图 3-4 例化 SPDIF\_RX\_Top

IPUG548-1.11 9(9)