# Gowin\_EMPU(GW1NS-4C)硬件设计 参考手册

IPUG932-1.2,2021-06-21

#### 版权所有 © 2021 广东高云半导体科技股份有限公司

**GO**₩IN高云、₩、Gowin、GowinSynthesis以及高云均为广东高云半导体科技股份有限公司注册商标,本手册中提到的其他任何商标,其所有权利属其拥有者所有。未经本公司书面许可,任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部,并不得以任何形式传播。

#### 免责声明

本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止发言或其它方式授予任何知识产权许可。除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。高云半导体不承诺对这些文档进行适时的更新。

## 版本信息

| 日期         | 版本  | 说明                                      |

|------------|-----|-----------------------------------------|

| 2020/04/20 | 1.0 | 初始版本。                                   |

|            |     | ● 支持外部设备 AHB PSRAM Memory Interface;    |

|            |     | ● 支持外部设备 AHB HyperRAM Memory Interface; |

| 0004/00/00 |     | ● 支持外部设备 APB SPI_Nor_Flash;             |

| 2021/02/08 | 1.1 | ● GPIO 支持多种端口类型配置;                      |

|            |     | ● I <sup>2</sup> C 支持多种端口类型配置;          |

|            |     | <ul><li>● 升级软件版本以及软件开发工具包。</li></ul>    |

|            | 1.2 | ● 修复已知的 SPI 全双工读写问题;                    |

| 2021/06/21 |     | ● 删除综合工具 SynplifyPro;                   |

|            |     | ● 更新 FPGA 软件版本;                         |

|            |     | ● 更新参考设计。                               |

i

## 目录

| 目 | 录                     | i     |

|---|-----------------------|-------|

| 图 | 目录                    | . iii |

| 表 | 目录                    | . iv  |

| 1 | 硬件架构                  | 1     |

|   | 1.1 系统架构              | 1     |

|   | 1.2 系统特征              | 2     |

|   | 1.2.1 MCU 内核系统        | 2     |

|   | 1.2.2 FPGA 内核系统       | 3     |

|   | 1.3 系统端口              | 3     |

|   | 1.4 系统资源统计            | 8     |

| 2 | 硬件设计流程                | 9     |

|   | 2.1 硬件环境              | 9     |

|   | 2.2 软件环境              | 9     |

|   | 2.3 IP Core Generator | 9     |

|   | 2.4 Programmer        | 9     |

|   | 2.5 设计流程              | . 10  |

| 3 | 工程模板                  | . 11  |

|   | 3.1 工程创建              | . 11  |

|   | 3.1.1 创建工程            | . 11  |

|   | 3.1.2 设置工程名称和路径       | . 12  |

|   | 3.1.3 选择器件            | . 12  |

|   | 3.1.4 完成工程创建          | . 13  |

|   | 3.2 硬件设计              | . 14  |

|   | 3.2.1 TPIU 配置         | . 17  |

|   | 3.2.2 NVIC 配置         | . 17  |

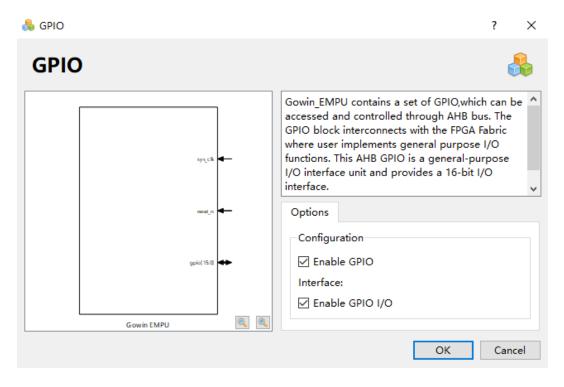

|   | 3.2.3 GPIO 配置                        | 18 |

|---|--------------------------------------|----|

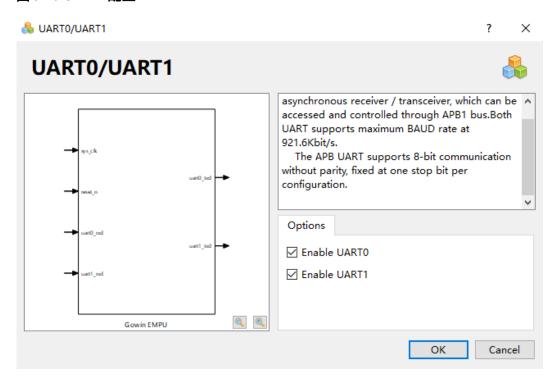

|   | 3.2.4 UART 配置                        | 19 |

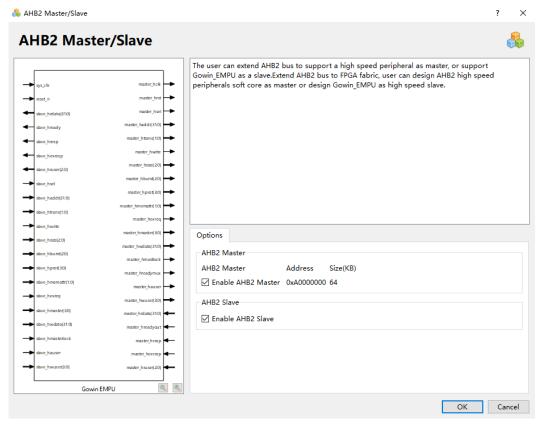

|   | 3.2.5 AHB2 Master/Slave 配置           | 20 |

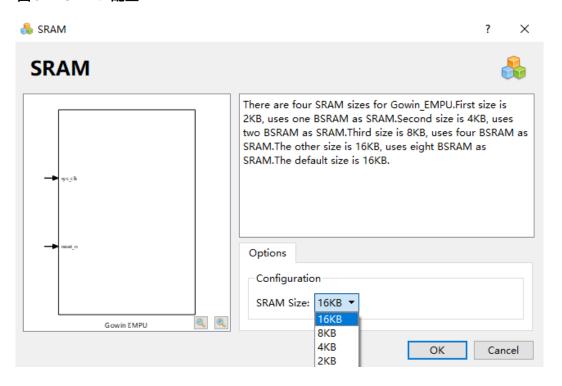

|   | 3.2.6 SRAM 配置                        | 21 |

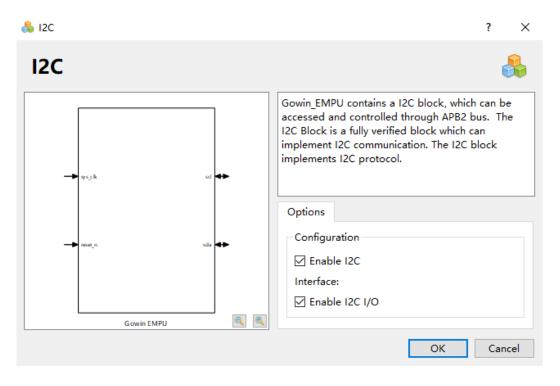

|   | 3.2.7 l <sup>2</sup> C 配置            | 22 |

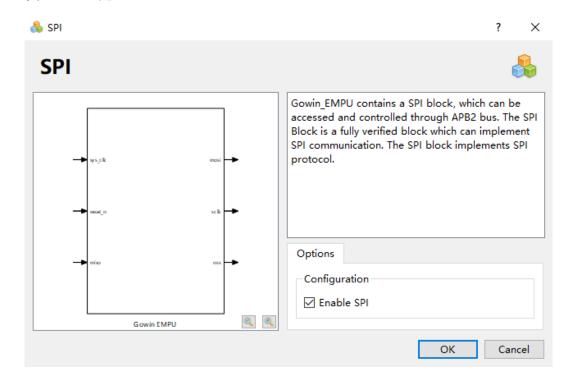

|   | 3.2.8 SPI 配置                         | 23 |

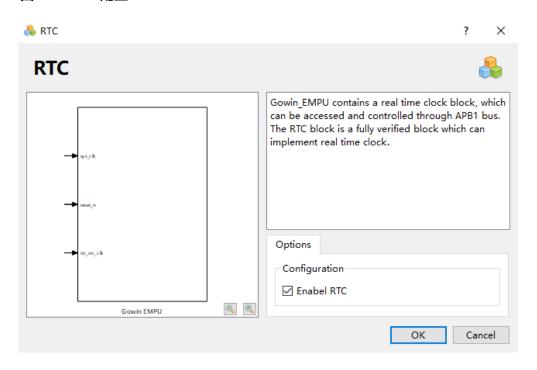

|   | 3.2.9 RTC 配置                         | 24 |

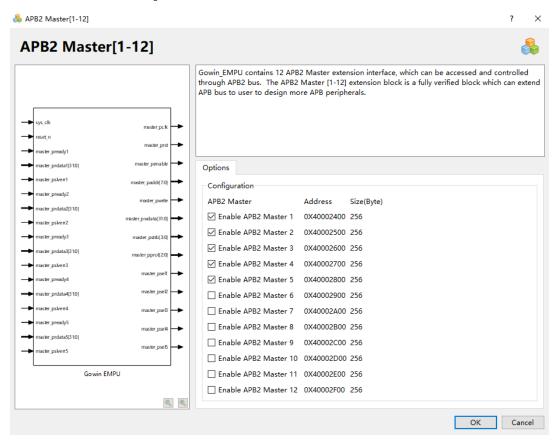

|   | 3.2.10 APB2 Master 配置                | 24 |

|   | 3.2.11 AHB PSRAM Memory Interface    | 26 |

|   | 3.2.12 AHB HyperRAM Memory Interface | 27 |

|   | 3.2.13 APB SPI_Nor_Flash             | 28 |

|   | 3.3 用户设计                             | 28 |

|   | 3.4 约束                               | 29 |

|   | 3.5 综合选项配置                           | 29 |

|   | 3.6 综合                               | 30 |

|   | 3.7 布局布线                             | 30 |

|   | 3.8 下载                               | 31 |

| 4 | 参考设计                                 | 33 |

# 图目录

| 图 | 1-1 系统架构                          | . 1  |

|---|-----------------------------------|------|

| 图 | 3-1 创建 FPGA Design 工程             | . 11 |

| 图 | 3-2 设置工程名称和路径                     | .12  |

| 图 | 3-3 选择器件                          | .13  |

| 图 | <b>3-4</b> 完成工程创建                 | .13  |

| 图 | 3-5 选择 Gowin_EMPU(GW1NS-4C)       | .14  |

| 图 | 3-6 系统结构图                         | . 15 |

| 图 | 3-7 TPIU 配置                       | . 17 |

| 图 | 3-8 NVIC 配置                       | .18  |

| 图 | 3-9 GPIO 配置                       | . 19 |

| 图 | 3-10 UART 配置                      | 20   |

| 图 | 3-11 AHB2 Master/Slave 配置         | 21   |

| 图 | 3-12 SRAM 配置                      | 22   |

| 图 | 3-13 I <sup>2</sup> C 配置          | 23   |

| 图 | 3-14 SPI 配置                       | 23   |

| 图 | 3-15 RTC 配置                       | 24   |

| 图 | 3-16 APB2 Master[1-12]配置          | 25   |

| 图 | 3-17 综合选项配置                       | 29   |

| 图 | 3-18 综合                           | 30   |

| 图 | 3-19 布局布线                         | 30   |

| 图 | 3-20 器件 GW1NS-4C/GW1NSR-4C 下载选项配置 | . 31 |

| 图 | 3-21 器件 GW1NSER-4C 下载选项配置         | . 32 |

## 表目录

| 表 1-1 系统端口定义                  | 3  |

|-------------------------------|----|

| 表 1-2 系统资源统计                  | 8  |

| 表 3-1 系统配置选项                  | 15 |

| 表 3-2 APB2 Master [1-12]基地址映射 | 26 |

IPUG932-1.2 iv

# 1 硬件架构

## 1.1 系统架构

Gowin\_EMPU(GW1NS-4C), 是由 MCU 内核系统和 FPGA 内核系统组成的片上系统,如图 1-1 所示。

#### MCU JTAG IF JTAG Config-Core DAP Cortex-M3 TPIU IF TPIU Bus Matrix FPGA Fabric USER\_INT[0-5] NVIC AHB2 Slave Extension SRAM FLASH AHB2 Slave AHB2 Master Extension AHB AHB2 Master LITE SRAM/FLASH IF GPIO IF BUS GPIO Clock/Reset AHB2APB Clock/Reset APB2 Extension IF APB2 Bridge UARTO IF UARTO Timer0 APB2 Master[1-12] UART1 IF UART1 Timer1 RTC IF Watch Dog

图 1-1 系统架构

MCU 内核系统,包括 MCU Core、AHB 总线及外部设备、AHB2APB Bridge、APB1 总线及外部设备等。

FPGA 内核系统,包括 MCU 内核系统的时钟和复位信号输入、MCU

IPUG932-1.2 1(33)

内核系统的数据存储器(SRAM)和指令存储器(FLASH)、APB2 Bridge、APB2 总线及外部设备等。

## 1.2 系统特征

Gowin\_EMPU(GW1NS-4C),包括两个子系统:

- MCU 内核系统

- FPGA 内核系统

## 1.2.1 MCU 内核系统

MCU 内核系统包括:

- MCU Core:

- ARM Cortex-M3 Core, ARM architecture v7-M Thumb2 指令集架构, 支持 16-bit 和 32-bit 指令集

- DAP (Debug Access Port)

- Bus Matrix

- NVIC (Nested Vector Interrupt Controller)

- TPIU (Trace Port Interface Unit)

- AHB 总线系统及外部设备

- GPIO

- AHB2 Master 用户扩展接口

- AHB2 Slave 用户扩展接口

- AHB2APB Bridge

- APB 总线系统及外部设备

- UARTO

- UART1

- Timer0

- Timer1

- Watch Dog

- RTC

- APB2 扩展接口

IPUG932-1.2 2(33)

## 1.2.2 FPGA 内核系统

FPGA 内核系统包括:

- 外部晶振时钟输入或内部晶振时钟,作为 MCU 内核系统的系统时钟源,系统时钟最高为 80MHz(以实际所用芯片及实际项目设计为准)

- 复位信号输入,作为 MCU 内核系统的系统复位信号

- 6个用户中断处理信号,用户扩展外部设备中断处理功能

- AHB 扩展接口

- SRAM 和 FLASH,作为 MCU 内核系统的数据存储器和指令存储器

- 1个 AHB2 Master 用户扩展接口

- 1 个 AHB2 Slave 用户扩展接口

- APB2 扩展接口

- SPI Master

- I2C Master

- 12 个 APB2 Master 用户扩展接口

- Memory

- MCU 内核系统数据存储器 SRAM Size,可以配置为 2KB、4KB、 8KB 或 16KB

- MCU 内核系统指令存储器 FLASH Size, 为 32KB

## 1.3 系统端口

Gowin\_EMPU(GW1NS-4C)系统端口定义,如表 1-1 所示。

表 1-1 系统端口定义

| 名称         | I/O | 位宽    | 描述         | 所属模块  |  |

|------------|-----|-------|------------|-------|--|

| sys_clk    | in  | 1     | 系统时钟信号     | -     |  |

| reset_n    | in  | 1     | 系统复位信号     | -     |  |

| trace_clk  | out | 1     | TPIU时钟信号   | TPIU  |  |

| trace_data | out | [3:0] | TPIU数据输出信号 | IFIO  |  |

| user_int_0 | in  | 1     | 用户中断处理信号 0 |       |  |

| user_int_1 | in  | 1     | 用户中断处理信号 1 | NVIC  |  |

| user_int_2 | in  | 1     | 用户中断处理信号 2 | INVIC |  |

| user_int_3 | in  | 1     | 用户中断处理信号 3 |       |  |

IPUG932-1.2 3(33)

1.3 系统端口

| 名称                  | I/O                    | 位宽     | 描述                         | 所属模块                            |  |

|---------------------|------------------------|--------|----------------------------|---------------------------------|--|

| user_int_4          | in                     | 1      | 用户中断处理信号 4                 |                                 |  |

| user_int_5          | in                     | 1      | 用户中断处理信号 5                 |                                 |  |

| gpio                | inout                  | [15:0] | 通用输入输出信号                   | GPIO I/O                        |  |

| gpioin              | in                     | [15:0] | 通用输入信号                     | GPIO non-I/O                    |  |

| gpioout             | out                    | [15:0] | 通用输出信号                     |                                 |  |

| gpioouten           | out                    | [15:0] | 通用输出使能信号                   |                                 |  |

| uart0_rxd           | in                     | 1      | UART0接收信号                  | LIADTO                          |  |

| uart0_txd           | out                    | 1      | UART0发送信号                  | - UARTO                         |  |

| uart1_rxd           | in                     | 1      | UART1接收信号                  | - UART1                         |  |

| uart1_txd           | out                    | 1      | UART1发送信号                  | UARTI                           |  |

| scl                 | inout                  | 1      | I <sup>2</sup> C串行时钟信号     | I <sup>2</sup> C Master I/O     |  |

| sda                 | inout                  | 1      | I <sup>2</sup> C串行数据信号     | - 1 C Master I/O                |  |

| sclin               | in                     | 1      | I <sup>2</sup> C串行时钟输入信号   |                                 |  |

| sclout              | out                    | 1      | I <sup>2</sup> C串行时钟输出信号   |                                 |  |

| sclouten out        |                        | 1      | I <sup>2</sup> C串行时钟输出使能信号 | I <sup>2</sup> C Master non-I/O |  |

| sdain               | in                     | 1      | I <sup>2</sup> C串行数据输入信号   | TC Master non-I/O               |  |

| sdaout              | out                    | 1      | I <sup>2</sup> C串行数据输出信号   |                                 |  |

| sdaouten            | out                    | 1      | I <sup>2</sup> C串行数据输出使能信号 |                                 |  |

| mosi                | out                    | 1      | SPI主设备输出/从设备输入信号           |                                 |  |

| miso                | in                     | 1      | SPI主设备输入/从设备输出信号           | 1                               |  |

| sclk out            |                        | 1      | SPI时钟信号                    | - SPI Master                    |  |

| nss                 | out                    | 1      | SPI从设备选择信号                 |                                 |  |

| rtc_src_clk         | in                     | 1      | RTC时钟信号                    | RTC                             |  |

| master_hclk         | out                    | 1      | Master时钟信号                 |                                 |  |

| master_hrst         | out                    | 1      | Master复位信号                 |                                 |  |

| master_hsel         | out                    | 1      | Master选择信号                 |                                 |  |

| master_haddr out    |                        | [31:0] | Master地址信号                 |                                 |  |

| master_htrans out   |                        | [1:0]  | Master传输类型信号               | AHB2 Master                     |  |

| master_hwrite out 1 |                        | 1      | Master读写方向信号               | 1                               |  |

| master_hsize        | naster_hsize out [2:0] |        | Master传输数据Size信号           |                                 |  |

| master_hburst       |                        |        | Master burst类型信号           |                                 |  |

| master_hprot        | out                    | [3:0]  | Master保护控制信号               | <u> </u>                        |  |

IPUG932-1.2 4(33)

| 名称               | I/O | 位宽     | 描述                 | 所属模块       |  |

|------------------|-----|--------|--------------------|------------|--|

| master_memattr   | out | [1:0]  | Master memattr信号   |            |  |

| master_exreq     | out | 1      | Matter exreq信号     |            |  |

| master_hmaster   | out | [3:0]  | Master主机标号信号       | 7          |  |

| master_hwdata    | out | [31:0] | Master写数据信号        | 7          |  |

| master_hmastlock | out | 1      | Master锁定标记信号       |            |  |

| master_hreadymux | out | 1      | Master hreadymux信号 |            |  |

| master_hauser    | out | 1      | Master hauser信号    |            |  |

| master_hwuser    | out | [3:0]  | Master hwuser信号    |            |  |

| master_hrdata    | in  | [31:0] | Master读数据信号        |            |  |

| master_hreadyout | in  | 1      | Master hreadyout信号 |            |  |

| master_hresp     | in  | 1      | Master传输状态信号       |            |  |

| master_exresp    | in  | 1      | Master exresp信号    |            |  |

| master_hruser    | in  | [2:0]  | Master hruser信号    |            |  |

| slave_hsel       | in  | 1      | Slave选择信号          |            |  |

| slave_haddr      | in  | [31:0] | Slave地址信号          |            |  |

| slave_htrans     | in  | [1:0]  | Slave传输类型信号        |            |  |

| slave_hwrite     | in  | 1      | Slave读写方向信号        |            |  |

| slave_hsize      | in  | [2:0]  | Slave传输数据Size信号    |            |  |

| slave_hburst     | in  | [2:0]  | Slave burst类型信号    |            |  |

| slave_hprot      | in  | [3:0]  | Slave保护控制信号        |            |  |

| slave_hmaster    | in  | [3:0]  | Slave主机标号信号        |            |  |

| slave_hwdata     | in  | [31:0] | Slave写数据信号         |            |  |

| slave_hmastlock  | in  | 1      | Slave锁定标记信号        | AHB2 Slave |  |

| slave_hrdata     | out | [31:0] | Slave读数据信号         |            |  |

| slave_hready     | out | 1      | Slave准备好信号         |            |  |

| slave_hresp      | out | 1      | Slave传输状态信号        |            |  |

| slave_hexresp    | out | 1      | Slave hexresp信号    |            |  |

| slave_hruser     | out | [2:0]  | Slave hruser信号     |            |  |

| slave_hmemattr   | in  | [1:0]  | Slave hmemattr信号   |            |  |

| slave_hexreq     | in  | 1      | Slave hexreq信号     |            |  |

| slave_hauser     | in  | 1      | Slave hauser信号     |            |  |

| slave_hwuser     | in  | [3:0]  | Slave hwuser信号     |            |  |

IPUG932-1.2 5(33)

1.3 系统端口

| 名称                | I/O        | 位宽                      | 描述                    | 所属模块            |  |

|-------------------|------------|-------------------------|-----------------------|-----------------|--|

| master_pclk       | out        | 1                       | APB2 Master时钟信号       |                 |  |

| master_prst       | out        | 1                       | APB2 Master复位信号       |                 |  |

| master_penable    | out        | 1                       | APB2 Master使能信号       |                 |  |

| master_paddr      | out        | [7:0]                   | APB2 Master地址信号       | APB2 Master     |  |

| master_pwrite     | out        | 1                       | APB2 Master读写方向信号     | [1-12]          |  |

| master_pwdata     | out        | [31:0] APB2 Master写数据信号 |                       |                 |  |

| master_pstrb      | out        | [3:0]                   | APB2 Master写选通信号      |                 |  |

| master_pprot      | out        | [2:0]                   | APB2 Master保护类型信号     |                 |  |

| master_psel1      | out        | 1                       | APB2 Master [1]选择信号   |                 |  |

| master_pready1    | in         | 1                       | APB2 Master [1]准备好信号  | ADDO Mostor [4] |  |

| master_prdata1    | in         | [31:0]                  | APB2 Master [1]读数据信号  | APB2 Master [1] |  |

| master_pslverr1   | in         | 1                       | APB2 Master [1]传输失败信号 |                 |  |

| master_psel2      | out        | 1                       | APB2 Master [2]选择信号   |                 |  |

| master_pready2    | in         | 1                       | APB2 Master [2]准备好信号  | ADDO Mostor [2] |  |

| master_prdata2    | in         | [31:0]                  | APB2 Master [2]读数据信号  | APB2 Master [2] |  |

| master_pslverr2   | in         | 1                       | APB2 Master [2]传输失败信号 |                 |  |

| master_psel3      | out        | 1                       | APB2 Master [3]选择信号   |                 |  |

| master_pready3    | in         | 1                       | APB2 Master [3]准备好信号  | ADD2 Moster [2] |  |

| master_prdata3    | in         | [31:0]                  | APB2 Master [3]读数据信号  | APB2 Master [3] |  |

| master_pslverr3   | in         | 1                       | APB2 Master[3]传输失败信号  |                 |  |

| master_psel4      | out        | 1                       | APB2 Master [4]选择信号   |                 |  |

| master_pready4 in |            | 1                       | APB2 Master [4]准备好信号  | ADDO Master [4] |  |

| master_prdata4    | in         | [31:0]                  | APB2 Master [4]读数据信号  | APB2 Master [4] |  |

| master_pslverr4   | in         | 1                       | APB2 Master[4]传输失败信号  |                 |  |

| master_psel5      | out        | 1                       | APB2 Master [5]选择信号   |                 |  |

| master_pready5    | pready5 in |                         | APB2 Master [5]准备好信号  | ADDO Master [5] |  |

| master_prdata5    | in         | [31:0]                  | APB2 Master [5]读数据信号  | APB2 Master [5] |  |

| master_pslverr5   | in         | 1                       | APB2 Master[5]传输失败信号  |                 |  |

| master_psel6      | out        | 1                       | APB2 Master [6]选择信号   |                 |  |

| master_pready6    | in         | 1                       | APB2 Master [6]准备好信号  | ADDO Master [C] |  |

| master_prdata6    | in         | [31:0]                  | APB2 Master [6]读数据信号  | APB2 Master [6] |  |

| master_pslverr6   | in         | 1                       | APB2 Master[6]传输失败信号  |                 |  |

IPUG932-1.2 6(33)

1.3 系统端口

| 名称                       | I/O    | 位宽     | 描述                    | 所属模块               |  |

|--------------------------|--------|--------|-----------------------|--------------------|--|

| master_psel7             | out    | 1      | APB2 Master [7]选择信号   |                    |  |

| master_pready7           | in     | 1      | APB2 Master [7]准备好信号  | - APB2 Master [7]  |  |

| master_prdata7 in        |        | [31:0] | APB2 Master [7]读数据信号  | APB2 Master [7]    |  |

| master_pslverr7          | in     | 1      | APB2 Master[7]传输失败信号  |                    |  |

| master_psel8             | out    | 1      | APB2 Master [8]选择信号   |                    |  |

| master_pready8           | in     | 1      | APB2 Master [8]准备好信号  | ADD2 Magter [9]    |  |

| master_prdata8           | in     | [31:0] | APB2 Master [8]读数据信号  | - APB2 Master [8]  |  |

| master_pslverr8          | in     | 1      | APB2 Master[8]传输失败信号  |                    |  |

| master_psel9             | out    | 1      | APB2 Master [9]选择信号   |                    |  |

| master_pready9           | in     | 1      | APB2 Master [9]准备好信号  | ADD2 Master [0]    |  |

| master_prdata9 in        |        | [31:0] | APB2 Master [9]读数据信号  | APB2 Master [9]    |  |

| master_pslverr9          | in     | 1      | APB2 Master[9]传输失败信号  |                    |  |

| master_psel10            | out    | 1      | APB2 Master [10]选择信号  |                    |  |

| master_pready10          | ) in 1 |        | APB2 Master [10]准备好信号 | APB2 Master [10]   |  |

| master_prdata10 in       |        | [31:0] | APB2 Master [10]读数据信号 |                    |  |

| master_pslverr10         | in     | 1      | APB2 Master[10]传输失败信号 | 1                  |  |

| master_psel11            | out    | 1      | APB2 Master [11]选择信号  |                    |  |

| master_pready11          | in     | 1      | APB2 Master [11]准备好信号 | ADD2 Master [44]   |  |

| master_prdata11          | in     | [31:0] | APB2 Master [11]读数据信号 | - APB2 Master [11] |  |

| master_pslverr11         | in     | 1      | APB2 Master[11]传输失败信号 |                    |  |

| master_psel12            | out    | 1      | APB2 Master [12]选择信号  |                    |  |

| master_pready12          | in     | 1      | APB2 Master [12]准备好信号 | ADD2 Moster [42]   |  |

| master_prdata12 in [31:0 |        | [31:0] | APB2 Master [12]读数据信号 | - APB2 Master [12] |  |

| master_pslverr12         | in     | 1      | APB2 Master[12]传输失败信号 |                    |  |

IPUG932-1.2 7(33)

1.4 系统资源统计

## 1.4 系统资源统计

Gowin\_EMPU(GW1NS-4C)系统资源统计,如表 1-2 所示。

表 1-2 系统资源统计

| Resources                      | LUTs | Registers | BSRAMs | DSP<br>Macros |

|--------------------------------|------|-----------|--------|---------------|

| MCU Core Minimum               | 145  | 116       | 1      | 0             |

| MCU Core Default + Peripherals | 468  | 285       | 8      | 0             |

| MCU Core + APB SPI_Nor_Flash   | 1151 | 715       | 8      | 0             |

| MCU Core + AHB PSRAM Memory    | 1804 | 1555      | 8      | 0             |

| MCU Core + AHB HyperRAM Memory | 1284 | 1103      | 8      | 0             |

IPUG932-1.2 8(33)

2.1 硬件环境

# **2** 硬件设计流程

## 2.1 硬件环境

- DK-START-GW1NSR4C-QN48G V1.1

GW1NSR-LV4CQN48GC7/I6

- DK-START-GW1NSR4C-QN48P V1.1

GW1NSR-LV4CQN48PC7/I6

- DK-START-GW1NSR4C-MG64P V1.1

GW1NSR-LV4CMG64PC7/I6

## 2.2 软件环境

Gowin V1.9.8Beta 及以上版本。

## 2.3 IP Core Generator

Gowin 云源软件的 IP Core Generator,用于配置和产生Gowin\_EMPU(GW1NS-4C)硬件设计。

## 2.4 Programmer

Gowin 下载软件 Programmer, 支持 Gowin\_EMPU(GW1NS-4C) 硬件设计码流下载。

Programmer 软件使用方法,请参考 <u>SUG502</u>,Gowin Programmer 用户指南。

IPUG932-1.2 9(33)

2.5 设计流程

## 2.5 设计流程

Gowin\_EMPU(GW1NS-4C)硬件设计流程:

● IP Core Generator 配置和产生 Gowin\_EMPU(GW1NS-4C)硬件设计, 导入当前工程;

- 实例化 Gowin\_EMPU(GW1NS-4C),导入用户应用设计,连接用户应用设计与 Gowin\_EMPU Top Module;

- 物理约束和时序约束;

- 使用综合工具 GowinSynthesis 综合,产生综合后网表文件;

- 使用布局布线工具 Place & Route 布局布线,产生码流文件;

- 使用下载工具 Programmer, 下载码流到 GW1NS-4C/GW1NSR-4C/GW1NSER-4C。

IPUG932-1.2 10(33)

3工程模板 3.1 工程创建

# **3** 工程模板

## 3.1 工程创建

## 3.1.1 创建工程

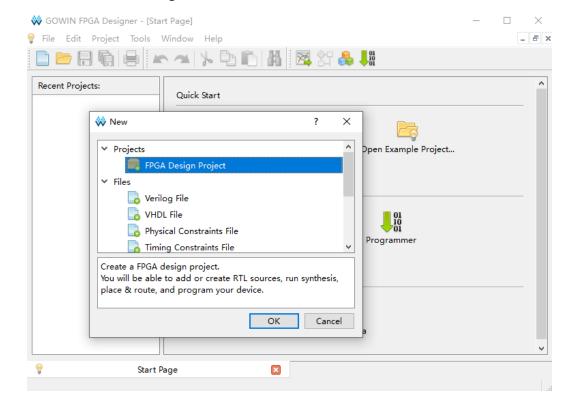

双击打开 Gowin 云源软件,选择菜单栏 "File > New... > FPGA Design Project",如图 3-1 所示。

#### 图 3-1 创建 FPGA Design 工程

IPUG932-1.2 11(33)

3工程模板 3.1 工程创建

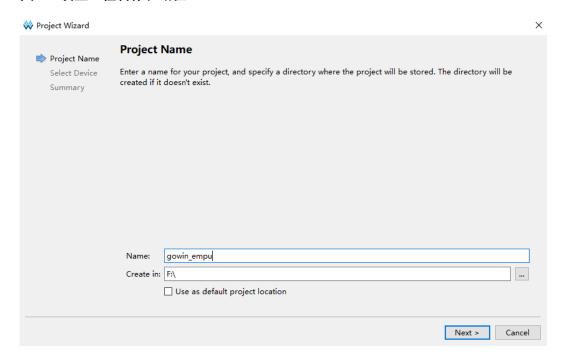

## 3.1.2 设置工程名称和路径

输入工程名称,选择工程路径,如图 3-2 所示。

#### 图 3-2 设置工程名称和路径

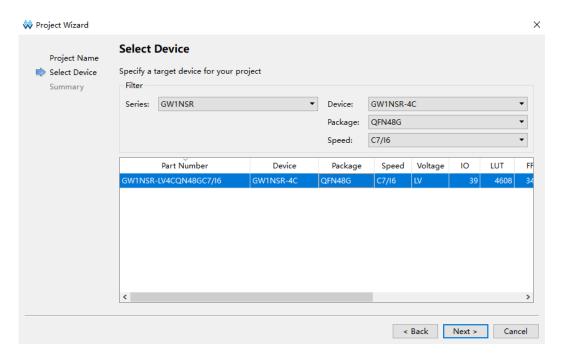

## 3.1.3 选择器件

选择 Series、Device、Package、Speed 和 Part Number,如图 3-3 所示。

以软件开发工具包 DK\_START\_GW1NSR4C\_QN48G\_V1.1 参考设计为例,如下所示。

Series: GW1NSR

Device: GW1NSR-4C

Package: QFN48G

Speed: C7/I6

Part Number: GW1NSR-LV4CQN48GC7/I6

IPUG932-1.2 12(33)

3工程模板 3.1 工程创建

#### 图 3-3 选择器件

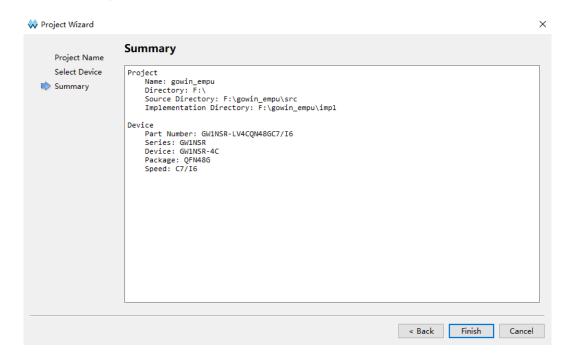

## 3.1.4 完成工程创建

完成工程创建,如图 3-4 所示。

#### 图 3-4 完成工程创建

IPUG932-1.2 13(33)

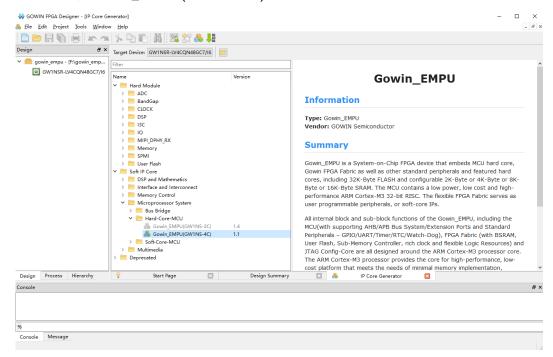

## 3.2 硬件设计

使用 IP Core Generator 产生 Gowin\_EMPU(GW1NS-4C)硬件设计。

选择 "Soft IP Core > Microprocessor System > Hard-Core-MCU > Gowin\_EMPU(GW1NS-4C) 1.1", 如图 3-5 所示。

#### 图 3-5 选择 Gowin\_EMPU(GW1NS-4C)

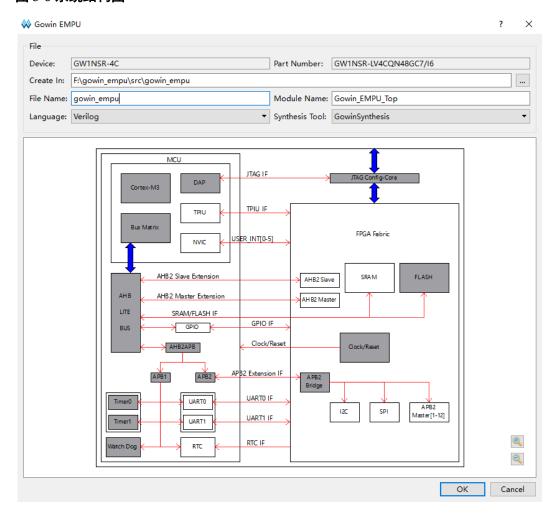

打开 Gowin\_EMPU(GW1NS-4C)配置选项,系统结构如图 3-6 所示。 其中置灰模块是系统默认,用户不可以配置;未置灰模块,请双击 打开该模块进行配置。

用户可以选择配置的模块,包括:

- TPIU

- NVIC: 6 个用户中断处理信号 USER INT0~5

- AHB2 Slave: FPGA 内核系统可以扩展 AHB2 Slave 用户设备

- AHB2 Master: FPGA 内核系统可以扩展 AHB2 Master 用户设备

- GPIO

- UART0 和 UART1

- RTC

IPUG932-1.2 14(33)

- SRAM:可以配置为 2KB、4KB、8KB 或 16KB,默认为 16KB

- I2C: FPGA 内核系统集成 I2C Master

- SPI: FPGA 内核系统集成 SPI Master

- APB2 Master[1-12]: FPGA 内核系统可以扩展 12 个 APB2 Master 用户设备

#### 图 3-6 系统结构图

Gowin\_EMPU(GW1NS-4C),系统配置选项,如表 3-1 所示。

表 3-1 系统配置选项

| 配置选项              | 描述                  |

|-------------------|---------------------|

| Enable TPIU       | 使能 TPIU,默认关闭。       |

| Enable USER_INT_0 | 使能用户中断处理信号[0],默认关闭。 |

| Enable USER_INT_1 | 使能用户中断处理信号[1],默认关闭。 |

| Enable USER_INT_2 | 使能用户中断处理信号[2],默认关闭。 |

| Enable USER_INT_3 | 使能用户中断处理信号[3],默认关闭。 |

IPUG932-1.2 15(33)

3工程模板 3.2 硬件设计

| 配置选项                        | 描述                                     |  |  |

|-----------------------------|----------------------------------------|--|--|

| Enable USER_INT_4           | 使能用户中断处理信号[4],默认关闭。                    |  |  |

| Enable USER_INT_5           | 使能用户中断处理信号[5],默认关闭。                    |  |  |

| Enable GPIO                 | 使能 GPIO,默认关闭。                          |  |  |

| Enable GPIO I/O             | 使能 GPIO inout 类型端口,默认打开。               |  |  |

| Enable UART0                | 使能 UARTO,默认关闭。                         |  |  |

| Enable UART1                | 使能 UART1,默认关闭。                         |  |  |

| Enable RTC                  | 使能 RTC,默认关闭。                           |  |  |

| Enable AHB2 Master          | 使能 AHB2 Master 用户扩展接口,默认关闭。            |  |  |

| Enable AHB2 Slave           | 使能 AHB2 Slave 用户扩展接口,默认关闭。             |  |  |

| Enable I <sup>2</sup> C     | 使能 I <sup>2</sup> C Master,默认关闭。       |  |  |

| Enable I <sup>2</sup> C I/O | 使能 I <sup>2</sup> C inout 类型端口,默认打开。   |  |  |

| Enable SPI                  | 使能 SPI Master,默认关闭。                    |  |  |

| Enable APB2 Master 1        | 使能 APB2 Master [1]用户扩展接口,默认关闭。         |  |  |

| Enable APB2 Master 2        | 使能 APB2 Master [2]用户扩展接口,默认关闭。         |  |  |

| Enable APB2 Master 3        | 使能 APB2 Master [3]用户扩展接口,默认关闭。         |  |  |

| Enable APB2 Master 4        | 使能 APB2 Master [4]用户扩展接口,默认关闭。         |  |  |

| Enable APB2 Master 5        | 使能 APB2 Master [5]用户扩展接口,默认关闭。         |  |  |

| Enable APB2 Master 6        | 使能 APB2 Master [6]用户扩展接口,默认关闭。         |  |  |

| Enable APB2 Master 7        | 使能 APB2 Master [7]用户扩展接口,默认关闭。         |  |  |

| Enable APB2 Master 8        | 使能 APB2 Master [8]用户扩展接口,默认关闭。         |  |  |

| Enable APB2 Master 9        | 使能 APB2 Master [9]用户扩展接口,默认关闭。         |  |  |

| Enable APB2 Master 10       | 使能 APB2 Master [10]用户扩展接口,默认关闭。        |  |  |

| Enable APB2 Master 11       | 使能 APB2 Master [11]用户扩展接口,默认关闭。        |  |  |

| Enable APB2 Master 12       | 使能 APB2 Master [12]用户扩展接口,默认关闭。        |  |  |

| SRAM Size                   | 配置数据存储器 Size,可以配置为 2/4/8/16KB,默认 16KB。 |  |  |

IPUG932-1.2 16(33)

3工程模板 3.2 硬件设计

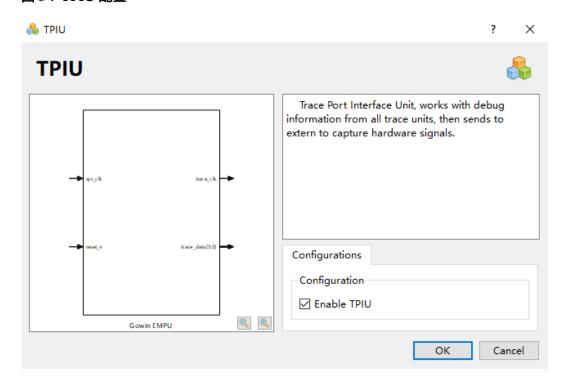

#### 3.2.1 TPIU 配置

双击打开 TPIU,可以选择配置 TPIU,如图 3-7 所示。

如果选择 Enable TPIU,则 Gowin\_EMPU(GW1NS-4C)支持 TPIU, 默认关闭。

#### 图 3-7 TPIU 配置

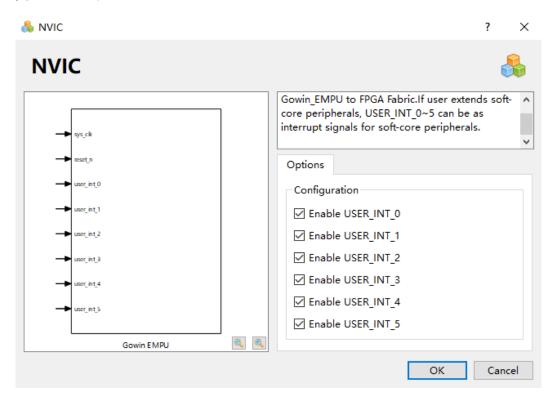

#### 3.2.2 NVIC 配置

双击打开 NVIC,可以选择配置用户中断处理信号 USER\_INT\_0~5,作为 FPGA 内核系统用户扩展外部设备中断处理功能的中断处理信号,如图 3-8 所示。

- 如果选择 Enable USER\_INT\_0,则 Gowin\_EMPU(GW1NS-4C)支持用户中断处理信号[0],默认关闭。

- 如果选择 Enable USER\_INT\_1,则 Gowin\_EMPU(GW1NS-4C)支持用户中断处理信号[1],默认关闭。

- 如果选择 Enable USER\_INT\_2,则 Gowin\_EMPU(GW1NS-4C)支持用户中断处理信号[2],默认关闭。

- 如果选择 Enable USER\_INT\_3,则 Gowin\_EMPU(GW1NS-4C)支持用户中断处理信号[3],默认关闭。

- 如果选择 Enable USER\_INT\_4,则 Gowin\_EMPU(GW1NS-4C)支持用户中断处理信号[4],默认关闭。

IPUG932-1.2 17(33)

● 如果选择 Enable USER\_INT\_5,则 Gowin\_EMPU(GW1NS-4C)支持用户中断处理信号[5],默认关闭。

#### 图 3-8 NVIC 配置

## 3.2.3 GPIO 配置

双击打开 GPIO,可以选择配置 GPIO,如图 3-9 所示。

- 如果选择 Enable GPIO,则 Gowin\_EMPU(GW1NS-4C)支持 GPIO,默 认关闭。

- 如果已经选择 Enable GPIO,则可以配置 GPIO 端口类型。

- 如果选择 Enable GPIO I/O,则 GPIO 支持 inout 类型端口,默认支持。

IPUG932-1.2 18(33)

#### 图 3-9 GPIO 配置

## 3.2.4 UART 配置

双击打开 UART0 或 UART1,可以选择配置 UART0 和 UART1,如 图 3-10 所示。

- 如果选择 Enable UART0,则 Gowin\_EMPU(GW1NS-4C)支持 UART0, 默认关闭。

- 如果选择 Enable UART1,则 Gowin\_EMPU(GW1NS-4C)支持 UART1, 默认关闭。

IPUG932-1.2 19(33)

#### 图 3-10 UART 配置

## 3.2.5 AHB2 Master/Slave 配置

双击打开 AHB2 Master 或 AHB2 Slave,可以选择配置 AHB2 Master 和 AHB2 Slave,如图 3-11 所示。

- 如果选择 Enable AHB2 Master,则 Gowin\_EMPU(GW1NS-4C)支持 AHB2 Master,默认关闭。

- 如果选择 Enable AHB2 Slave,则 Gowin\_EMPU(GW1NS-4C)支持 AHB2 Slave,默认关闭。

- AHB2 Master 用户扩展外部设备的基地址映射: 0xA0000000。

IPUG932-1.2 20(33)

#### 图 3-11 AHB2 Master/Slave 配置

## 3.2.6 SRAM 配置

双击打开 SRAM,可以选择配置 SRAM Size,如图 3-12 所示。 默认 SRAM Size 为 16KB,可以选择配置 SRAM Size 为 2KB、4KB、 8KB 或 16KB。

IPUG932-1.2 21(33)

#### 图 3-12 SRAM 配置

## 3.2.7 I<sup>2</sup>C 配置

双击打开 "I2C", 可以选择配置 I<sup>2</sup>C Master, 如图 3-13 所示。

- 如果选择"Enable I2C",则 Gowin\_EMPU(GW1NS-4C)支持 I<sup>2</sup>C Master, 默认关闭。

- 如果已经选择 "Enable I2C",则可以配置 I<sup>2</sup>C Master 端口类型。

- 如果选择 "Enable I2C I/O",则 I<sup>2</sup>C Master 支持 inout 类型端口,默认支持。

IPUG932-1.2 22(33)

#### 图 3-13 I2C 配置

## 3.2.8 SPI 配置

双击打开 SPI,可以选择配置 SPI Master,如图 3-14 所示。

如果选择 Enable SPI,则 Gowin\_EMPU(GW1NS-4C)支持 SPI Master,默认关闭。

#### 图 3-14 SPI 配置

IPUG932-1.2 23(33)

3 工程模板 3.2 硬件设计

#### 3.2.9 RTC 配置

双击打开 RTC,可以选择配置 RTC,如图 3-15 所示。

如果选择 Enable RTC,则 Gowin\_EMPU(GW1NS-4C)支持 RTC,默认关闭。

端口 rtc\_src\_clk 接入 3.072MHz 时钟输入,RTC 内部分频为 1Hz。

#### 图 3-15 RTC 配置

## 3.2.10 APB2 Master 配置

双击打开 APB2 Master[1-12],可以选择配置 APB2 Master [1-12], 如图 3-16 所示。

- 如果选择 Enable APB2 Master 1,则 Gowin\_EMPU(GW1NS-4C)支持 APB2 Master [1],默认关闭。

- 如果选择 Enable APB2 Master 2,则 Gowin\_EMPU(GW1NS-4C)支持 APB2 Master [2],默认关闭。

- 如果选择 Enable APB2 Master 3,则 Gowin\_EMPU(GW1NS-4C)支持 APB2 Master [3],默认关闭。

- 如果选择 Enable APB2 Master 4,则 Gowin\_EMPU(GW1NS-4C)支持 APB2 Master [4],默认关闭。

- 如果选择 Enable APB2 Master 5,则 Gowin\_EMPU(GW1NS-4C)支持 APB2 Master [5],默认关闭。

IPUG932-1.2 24(33)

● 如果选择 Enable APB2 Master 6,则 Gowin\_EMPU(GW1NS-4C)支持 APB2 Master [6],默认关闭。

- 如果选择 Enable APB2 Master 7,则 Gowin\_EMPU(GW1NS-4C)支持 APB2 Master [7],默认关闭。

- 如果选择 Enable APB2 Master 8,则 Gowin\_EMPU(GW1NS-4C)支持 APB2 Master [8],默认关闭。

- 如果选择 Enable APB2 Master 9,则 Gowin\_EMPU(GW1NS-4C)支持 APB2 Master [9],默认关闭。

- 如果选择 Enable APB2 Master 10,则 Gowin\_EMPU(GW1NS-4C)支持 APB2 Master [10],默认关闭。

- 如果选择 Enable APB2 Master 11,则 Gowin\_EMPU(GW1NS-4C)支持 APB2 Master [11],默认关闭。

- 如果选择 Enable APB2 Master 12,则 Gowin\_EMPU(GW1NS-4C)支持 APB2 Master [12],默认关闭。

#### 图 3-16 APB2 Master[1-12]配置

APB2 Master [1-12]用户扩展外部设备的基地址映射,如表 3-2 所示。

IPUG932-1.2 25(33)

表 3-2 APB2 Master [1-12]基地址映射

| APB2 Master | Address    | Size(Byte) |

|-------------|------------|------------|

| 1           | 0x40002400 | 256        |

| 2           | 0x40002500 | 256        |

| 3           | 0x40002600 | 256        |

| 4           | 0x40002700 | 256        |

| 5           | 0x40002800 | 256        |

| 6           | 0x40002900 | 256        |

| 7           | 0x40002A00 | 256        |

| 8           | 0x40002B00 | 256        |

| 9           | 0x40002C00 | 256        |

| 10          | 0x40002E00 | 256        |

| 11          | 0x40002E00 | 256        |

| 12          | 0x40002F00 | 256        |

## 3.2.11 AHB PSRAM Memory Interface

如果选用器件 GW1NSR-4C MG64P,则 Gowin\_EMPU(GW1NS-4C)支持外部设备 AHB PSRAM Memory Interface。

软件开发工具包以参考设计方式,提供外部设备 AHB PSRAM Memory Interface。

#### 硬件设计流程

- IPCore Generator 配置与产生 Gowin\_EMPU(GW1NS-4C), 使能 AHB2 Master 用户扩展接口

- IPCore Generator 配置与产生 PSRAM Memory Interface

- Memory Clock 100MHz

- 其它选项默认配置

- 设计实现 AHB 总线接口的 AHB PSRAM Memory Interface

- 实例化 Gowin\_EMPU(GW1NS-4C) Top Module 和 AHB PSRAM Memory Interface Top Module

- 连接 Gowin\_EMPU(GW1NS-4C)与 AHB PSRAM Memory Interface 的 AHB 总线接口

#### 参考设计

● 硬件参考设计

IPUG932-1.2 26(33)

3工程模板 3.2 硬件设计

Gowin\_EMPU\ref\_design\FPGA\_RefDesign\DK\_START\_GW1NS R4C\_MG64P\_V1.1\gowin\_empu\_psram

- 软件参考设计

- Gowin\_EMPU\ref\_design\MCU\_RefDesign\Keil\_RefDesign\psram

- Gowin\_EMPU\ref\_design\MCU\_RefDesign\GMD\_RefDesign\cm3 \_psram

## 3.2.12 AHB HyperRAM Memory Interface

如果选用器件 GW1NSR-4C/GW1NSER-4C QN48P,则 Gowin\_EMPU(GW1NS-4C)支持外部设备 AHB HyperRAM Memory Interface。

软件开发工具包以参考设计方式,提供外部设备 AHB HyperRAM Memory Interface。

#### 硬件设计流程

- IPCore Generator 配置与产生 Gowin\_EMPU(GW1NS-4C), 使能 AHB2 Master 用户扩展接口

- IPCore Generator 配置与产生 HyperRAM Memory Interface Embedded

- Memory Clock 100MHz

- 其它选项默认配置

- 设计实现 AHB 总线接口的 AHB HyperRAM Memory Interface

- 实例化 Gowin\_EMPU(GW1NS-4C) Top Module 和 AHB HyperRAM Memory Interface Top Module

- 连接 Gowin\_EMPU(GW1NS-4C)与 AHB HyperRAM Memory Interface 的 AHB 总线接口

#### 参考设计

- 硬件参考设计

- Gowin\_EMPU\ref\_design\FPGA\_RefDesign\DK\_START\_GW1NSR4C \_QN48P\_V1.1\gowin\_empu\_hyperram

- 软件参考设计

- Gowin\_EMPU\ref\_design\MCU\_RefDesign\Keil\_RefDesign\hyper \_ram

- Gowin\_EMPU\ref\_design\MCU\_RefDesign\GMD\_RefDesign\cm3 \_hyper\_ram

IPUG932-1.2 27(33)

3.3 用户设计

#### 3.2.13 APB SPI Nor Flash

如果选用器件 GW1NSR-4C/GW1NSER-4C QN48G,则 Gowin\_EMPU(GW1NS-4C)支持外部设备 APB SPI\_Nor\_Flash。

软件开发工具包以参考设计方式,提供外部设备 APB SPI\_Nor\_Flash。

#### 硬件设计流程

- IPCore Generator 配置与产生 Gowin\_EMPU(GW1NS-4C), 使能 APB2 Master [1]用户扩展接口

- 设计实现 SPI\_Nor\_Flash 控制器

- 设计实现 APB 总线接口的 APB SPI\_Nor\_Flash

- 实例化 Gowin\_EMPU(GW1NS-4C) Top Module 和 APB SPI\_Nor\_Flash Top Module

- 连接 Gowin\_EMPU(GW1NS-4C)与 APB SPI\_Nor\_Flash 的 APB 总线接口

#### 参考设计

- 硬件参考设计

Gowin\_EMPU\ref\_design\FPGA\_RefDesign\DK\_START\_GW1NSR4C

\_QN48G\_V1.1\gowin\_empu\_spinorflash

- 软件参考设计

- Gowin\_EMPU\ref\_design\MCU\_RefDesign\Keil\_RefDesign\spi\_no

r flash

- Gowin\_EMPU\ref\_design\MCU\_RefDesign\GMD\_RefDesign\cm3\_spi\_nor\_flash

## 3.3 用户设计

- 完成 Gowin\_EMPU(GW1NS-4C)配置后,产生 Gowin\_EMPU(GW1NS-4C)硬件设计

- 实例化 Gowin\_EMPU(GW1NS-4C) Top Module

- 导入用户应用设计,连接 Gowin\_EMPU(GW1NS-4C) Top Module 与用户应用设计,形成完整的 RTL 设计

IPUG932-1.2 28(33)

3 工程模板 3.4 约束

## 3.4 约束

完成用户 RTL 设计后,根据使用的开发板和需要输入输出的 IO,产生物理约束文件。

根据时序要求,产生时序约束文件。

物理约束和时序约束的产生方法,请参考 <u>SUG101</u>,Gowin 设计约束指南。

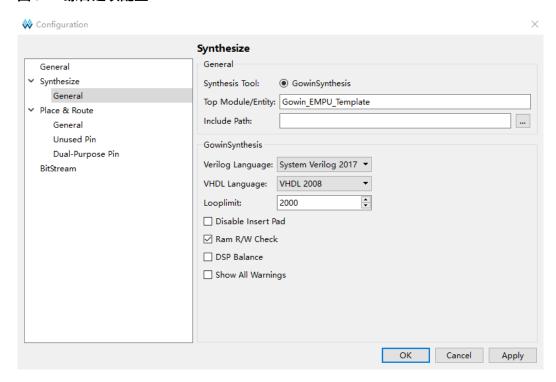

## 3.5 综合选项配置

综合选项配置,如图 3-17 所示。

- 根据设计中的实际顶层模块名称,配置 Top Module/Entity;

- 根据设计中的实际文件引用路径,配置 Include Path;

- 配置 Verilog Language,如 System Verilog 2017。

#### 图 3-17 综合选项配置

IPUG932-1.2 29(33)

3.6 综合

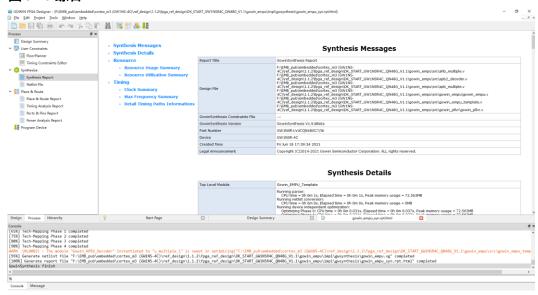

## 3.6 综合

运行 Gowin 云源软件的综合工具 GowinSynthesis, 完成 RTL 设计的综合,产生综合后的网表文件,如图 3-18 所示。

#### 图 3-18 综合

综合工具的使用方法,请参考 SUG100, Gowin 云源软件用户指南。

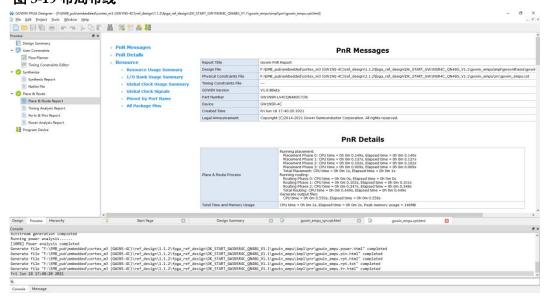

## 3.7 布局布线

运行 Gowin 云源软件的布局布线工具 Place & Route, 完成布局布线, 产生码流文件, 如图 3-19 所示。

#### 图 3-19 布局布线

布局布线工具使用方法,请参考 SUG100, Gowin 云源软件用户指

IPUG932-1.2 30(33)

3.8 下载

南。

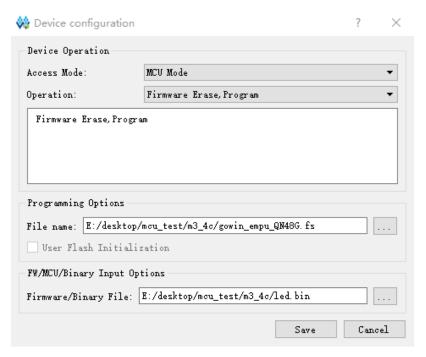

## 3.8 下载

使用 Gowin 云源软件的 Programmer 下载软件,下载硬件设计码流文件。

在 Gowin 云源软件中或安装路径下,打开下载软件 Programmer。

单击 Programmer 菜单栏 "Edit > Configure Device"或工具栏 "Configure Device"(圖), 打开 Device configuration。

如果是器件 GW1NS-4C/GW1NSR-4C,下载选项配置,如图 3-20 所示。

- Access Mode 下拉列表,选择"MCU Mode"选项。

- Operation 下拉列表,选择"Firmware Erase, Program"选项或"Firmware Erase, Program, Verify"选项。

#### 图 3-20 器件 GW1NS-4C/GW1NSR-4C 下载选项配置

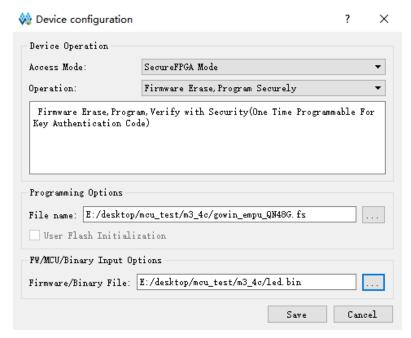

如果是器件 GW1NSER-4C, 下载选项配置, 如图 3-21 所示。

- Access Mode 下拉列表,选择 "SecureFPGA Mode"选项。

- Operation 下拉列表,选择"Firmware Erase, Program Securely"选项。

IPUG932-1.2 31(33)

3 工程模板 3.8 下载

#### 图 3-21 器件 GW1NSER-4C 下载选项配置

- "Programming Options > File name"选项,导入 Gowin\_EMPU(GW1NS-4C)硬件设计码流文件。

- 单击 "Save", 完成下载选项配置。

#### 注!

"FW/MCU/Binary Input Options > Firmware/Binary File"选项,导入Gowin\_EMPU(GW1NS-4C)软件编程设计二进制 BIN 文件,请参考 <u>IPUG928</u>,Gowin\_EMPU(GW1NS-4C) IDE 软件参考手册。

完成 Device configuration 后,单击 Programmer 工具栏 "Program/Configure"(事),完成 Gowin\_EMPU(GW1NS-4C)的下载。

下载软件 Programmer 使用方法,请参考 <u>SUG502</u>, Gowin Programmer 用户指南。

IPUG932-1.2 32(33)

## **4** 参考设计

Gowin\_EMPU(GW1NS-4C)提供硬件参考设计,通过链接获取如下参考设计: <u>cdn.gowinsemi.com.cn/Gowin\_EMPU\_V1.1.zip</u>:

Gowin\_EMPU\ref\_design\FPGA\_RefDesign

IPUG932-1.2 33(33)