# Gowin Design Constraints **User Guide**

SUG101-1.9E,03/09/2020

#### Copyright© 2020 Guangdong Gowin Semiconductor Corporation. All Rights Reserved.

No part of this document may be reproduced or transmitted in any form or by any denotes, electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of GOWINSEMI.

#### Disclaimer

GOWINSEMI®, LittleBee®, Arora, and the GOWINSEMI logos are trademarks of GOWINSEMI and are registered in China, the U.S. Patent and Trademark Office, and other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders, as described at www.gowinsemi.com. GOWINSEMI assumes no liability and provides no warranty (either expressed or implied) and is not responsible for any damage incurred to your hardware, software, data, or property resulting from usage of the materials or intellectual property except as outlined in the GOWINSEMI Terms and Conditions of Sale. All information in this document should be treated as preliminary. GOWINSEMI may make changes to this document at any time without prior notice. Anyone relying on this documentation should contact GOWINSEMI for the current documentation and errata.

## **Revision History**

| Date            | Version | Description                                                                  |  |

|-----------------|---------|------------------------------------------------------------------------------|--|

| 03/03/2016      | 1.09E   | Initial version published.                                                   |  |

|                 |         | Reload function added in FloorPlanner;                                       |  |

|                 |         | I3C mode added attribute in IO Constraint;                                   |  |

| 01/30/2018 1.1E |         | Multiple VCCs added and merged into one VCC in package view                  |  |

|                 |         | of FloorPlanner;                                                             |  |

|                 |         | Position constraint removed from clock constraint.                           |  |

|                 |         | Supports GW1N-2B, GW1N-4B, GW1N-6ES, GW1N-9ES,                               |  |

|                 |         | GW1NR-9ES, GW1NS-2, GW1NS-2C;                                                |  |

|                 |         | Removes the differential IO positive and negative poles in the               |  |

|                 |         | Package View of FloorPlanner and IO Color;                                   |  |

|                 |         | Changes the constraint color in the Chip ArrayFloor of Planner;              |  |

|                 |         | Changes the Arribute into ALL/LUT/REG in the Reserve constraint              |  |

| 07/05/2018      | 1.2E    | of FloorPlanner;                                                             |  |

|                 |         | The TCL Console is removed in the FloorPlanner and changed it                |  |

|                 |         | into the Message;                                                            |  |

|                 |         | <ul> <li>Removes the check in the FloorPlanner;</li> </ul>                   |  |

|                 |         | <ul><li>In the set_false_path, set_min_delay, set_max_delay and</li></ul>    |  |

|                 |         | set_multicycle_path, keep one "from" and remove the "rise_from"              |  |

|                 |         | and "fall_from"; keep one "to" and remove the "rise_to" fall_to".            |  |

| 09/21/2018      | 1.3E    | The description in appendix A updated.                                       |  |

| 10/26/2018      | 1.4E    | <ul> <li>GW1NZ-1/GW1NSR-2C supported;</li> </ul>                             |  |

| 10/20/2010      | 1.45    | The description in appendix A updated.                                       |  |

| 11/23/2018      | 1.5E    | GW1NSR-2 supported;                                                          |  |

| 11/20/2010      | 1.0L    | GW1N-6ES, GW1N-9ES, and GW1NR-9ES deleted.                                   |  |

|                 |         | The description of devices in List window updated, the description           |  |

|                 | 1.6E    | of devices and package, etc. removed, and describe them in the               |  |

| 03/06/2019      |         | form of Part Number;                                                         |  |

|                 |         | Select Part window updated;                                                  |  |

|                 |         | The description of appendix A updated.                                       |  |

| 05/17/2019      | 1.7E    | GW1N-1S supported.                                                           |  |

|                 | 1.8E    | <ul> <li>NET_LOC is updated to CLOCK_LOC and supports constraints</li> </ul> |  |

| 10/29/2019      |         | on non clock wire;                                                           |  |

| . 3, 23, 2010   |         | GW1NSE-2C, GW1NSER-4C, GW1NS-4, GW1NSR-4 and                                 |  |

|                 |         | GW1NRF-4B supported.                                                         |  |

| 03/09/2020      | 1.9E    | GW2A-18C, GW2AR-18C, GW2A-55C, GW1NS-4C, GW1NSR-4C                           |  |

| 00/03/2020 1.3L |         | supported.                                                                   |  |

## **Contents**

| Cor  | ntents                                     | . i |

|------|--------------------------------------------|-----|

| List | of Figures                                 | V   |

| List | of Tables                                  | X   |

| 1 Al | bout This Guide                            | 1   |

|      | 1.1 Purpose                                | 1   |

|      | 1.2 Supported Products                     | 1   |

|      | 1.3 Related Documents                      | 1   |

|      | 1.4 Abbreviations and Terminology          | 2   |

|      | 1.5 Support and Feedback                   | 2   |

| 2 In | troduction                                 | 3   |

| 3 Pł | nysical Constraints                        | 4   |

|      | 3.1 Function                               | 4   |

|      | 3.2 Start FloorPlanner                     | 4   |

|      | 3.3 Create and Open the Constraint File    | 6   |

|      | 3.3.1 Create Constraints File              | 6   |

|      | 3.3.2 FloorPlanner Output Constraint Files | 7   |

|      | 3.3.3 Open the Constraints File            | 9   |

|      | 3.4 FloorPlanner View                      | 9   |

|      | 3.4.1 Menu1                                | 0   |

|      | 3.4.2 Netlist and Project View2            | 4   |

|      | 3.4.3 Package View                         | 0   |

|      | 3.4.4 Chip Array View3                     | 3   |

|      | 3.4.5 Constraint View3                     | 8   |

|      | 3.5 Tcl Console View4                      | .2  |

|     | 3.6 Create Constraints - Drag Mode          | . 43 |

|-----|---------------------------------------------|------|

|     | 3.6.1 Set I/O Constraints Position          | . 43 |

|     | 3.6.2 Create Primitive Constraints          | . 45 |

|     | 3.6.3 Create Group Constraints              | . 47 |

|     | 3.6.4 Resource Reservation Creation         | . 49 |

|     | 3.6.5 Create Clock Assignment               | . 50 |

|     | 3.6.6 Quadrant Constraints Creation         | . 52 |

|     | 3.6.7 Create Hclk Constraints               | . 53 |

|     | 3.6.8 Vref Constraints Creation             | . 55 |

| 4 T | iming Constraint                            | 58   |

|     | 4.1 Static Timing Analysis (STA) Overview   | . 58 |

|     | 4.1.1 Basic Model of Static Timing Analysis | . 58 |

|     | 4.1.2 Timing Analysis Terminology           | . 59 |

|     | 4.1.3 Timing Analysis Path                  | . 59 |

|     | 4.1.4 Common Timing Checks                  | . 60 |

|     | 4.2 Timing Constraints Editor               | . 61 |

|     | 4.2.1 Overview                              | . 61 |

|     | 4.2.2 Open Editor                           | . 61 |

|     | 4.2.3 Create and Open the Constraints File  | . 62 |

|     | 4.2.4 Editor                                | . 64 |

|     | 4.2.5 Timing Constraints                    | . 66 |

|     | 4.3 Edit the SDC File                       | . 67 |

|     | 4.4 Edit Timing Constraints                 | . 68 |

|     | 4.4.1 Clock Constraints                     | . 68 |

|     | 4.4.2 I/O Delay                             | . 75 |

|     | 4.4.3 Path Constraints                      | . 77 |

|     | 4.4.4 Operation Conditions Constraints      | . 80 |

|     | 4.4.5 Timing Report                         | . 80 |

|     | 4.4.6 Save and Export                       | . 87 |

|     | 4.5 Priority of Timing Constraints          | . 87 |

| 5 T | iming Analysis View                         | 88   |

| Appendix A Physical Constraints Syntax Definition | 94  |

|---------------------------------------------------|-----|

| A.1 I/O Constraints                               | 94  |

| A.2 PORT Attributes Constraints                   | 95  |

| A.3 Primitive Constraints                         | 96  |

| A.4 Primitive Group Constraints                   | 99  |

| A.5 Resource Reservation                          | 101 |

| A.6 Relative Group Constraints                    | 102 |

| A.7 Vref Constraints                              | 102 |

| A.8 Quadrant Constraints                          | 103 |

| A.9 Clock Assignment                              | 104 |

| A.10 Hclk Constraints                             | 106 |

| Appendix B Timing Constraints Syntax Definition   | 108 |

| B.1 Clock Constraints                             | 108 |

| B.1.1 create_clock                                | 108 |

| B.1.2 create_generated_clock                      | 110 |

| B.1.4 set_clock_uncertainty                       | 113 |

| B.1.5 set_clock_groups                            | 114 |

| B.2 I/O Constraints                               | 115 |

| B.2.1 set_input_delay                             | 115 |

| B.2.2 set_output_delay                            | 117 |

| B.3 Path Constraints                              | 118 |

| B.3.1 set_max_delay   set_min_delay               | 118 |

| B.3.2 set_false_path                              | 120 |

| B.3.3 set_multicycle_path                         | 121 |

| B.4 Operation Conditions Constraints              | 123 |

| B.5 Timing Report                                 | 124 |

| B.5.1 report_timing                               | 124 |

| B.5.2 report_high_fanout_nets                     | 125 |

| B.5.3 report_route_congestion                     | 126 |

| B.5.4 report_min_pulse_width                      | 127 |

| B.5.5 report_max_frequency                        | 128 |

| B.5.6 report_exceptions128              |

|-----------------------------------------|

| B.1.2 create_generated_clock131         |

| B.1.4 set_clock_uncertainty135          |

| B.1.5 set_clock_groups136               |

| B.2 I/O Constraints136                  |

| B.2.1 set_input_delay136                |

| B.2.2 set_output_delay138               |

| B.3 Path Constraints140                 |

| B.3.1 set_max_delay   set_min_delay140  |

| B.3.2 set_false_path142                 |

| B.3.3 set_multicycle_path143            |

| B.4 Operation Conditions Constraints144 |

| B.5 Timing Report145                    |

| B.5.1 report_timing145                  |

| B.5.2 report_high_fanout_nets147        |

| B.5.3 report_route_congestion147        |

| B.5.4 report_min_pulse_width148         |

| B.5.5 report_max_frequency149           |

| B.5.6 report exceptions                 |

## **List of Figures**

| Figure 3-1 Start FloorPlanner From Tools Menu            | 5    |

|----------------------------------------------------------|------|

| Figure 3-2 Process View                                  | 5    |

| Figure 3-3 Open New Physical Constraints File            | . 6  |

| Figure 3-4 Create Physical Constraints File              | 7    |

| Figure 3-5 Manually Writing Physical Constraints File    | 7    |

| Figure 3-6 New FloorPlanner                              | 8    |

| Figure 3-7 Save Output File                              | 8    |

| Figure 3-8 Open the Physical Constraint File             | 9    |

| Figure 3-9 FloorPlanner View                             | 10   |

| Figure 3-10 File                                         | 10   |

| Figure 3-11 Select Device                                | 11   |

| Figure 3-12 Tools                                        | 12   |

| Figure 3-13 Primitive Finder View                        | 13   |

| Figure 3-14 New Primitive Group                          | 14   |

| Figure 3-15 Correct Primitive Group Interface            | 15   |

| Figure 3-16 Invalid Position                             | 16   |

| Figure 3-17 Invalid Position                             | 16   |

| Figure 3-18 New Relative Group                           | 17   |

| Figure 3-19 Group Interface in Correct Relative Position | 17   |

| Figure 3-20 Reserved Constraint                          | 18   |

| Figure 3-21 Timing Constraint                            | 19   |

| Figure 3-22 Quadrant Constraints (GW1N)                  | 19   |

| Figure 3-23 Quadrant Constraints (GW2A)                  | 20   |

| Figure 3-24 Hclk Constraints                             | 20   |

| Figure 3-25 Vref Constraints                             | . 21 |

| Figure 3-26 Select One Hit Drag Primitive        | 21 |

|--------------------------------------------------|----|

| Figure 3-27 Select One Hit Drag Location         | 22 |

| Figure 3-28 One Hit Drag Constraints             | 22 |

| Figure 3-29 Find View                            | 23 |

| Figure 3-30 View                                 | 24 |

| Figure 3-31 Windows                              | 24 |

| Figure 3-32 Help                                 | 24 |

| Figure 3-33 Project View                         | 25 |

| Figure 3-34 Netlist View                         | 26 |

| Figure 3-35 Show Bus and Non-Bus Conjunctively   | 27 |

| Figure 3-36 Hierarchical View                    | 28 |

| Figure 3-37 Timing Path                          | 29 |

| Figure 3-38 Netlist Right-Click Functions        | 30 |

| Figure 3-39 Package View                         | 31 |

| Figure 3-40 Right-Click Function of Package View | 32 |

| Figure 3-41 Differential Pair Display            | 32 |

| Figure 3-42 Chip Array View                      | 33 |

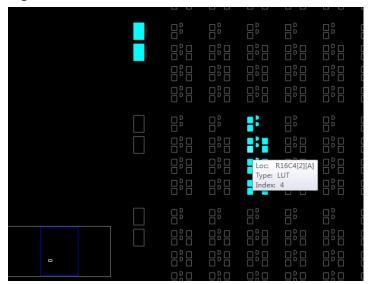

| Figure 3-43 Grid Constraint                      | 34 |

| Figure 3-44 Macro Element Constraint             | 34 |

| Figure 3-45 Primitive Constraint                 | 35 |

| Figure 3-46 Right-Clicking on the Chip Array     | 36 |

| Figure 3-47 Show Place View                      | 37 |

| Figure 3-48 Highlighted Timing Path              | 37 |

| Figure 3-49 I/O Constraint View                  | 38 |

| Figure 3-50 Primitive Constraints View           | 39 |

| Figure 3-51 Group Constraints View               | 40 |

| Figure 3-52 Resource Reservation View            | 40 |

| Figure 3-53 Clock Constraint View                | 41 |

| Figure 3-54 Quadrant Constraints View            | 41 |

| Figure 3-55 Hclk Constraints View                | 42 |

| Figure 3-56 Vref Constraints View                | 42 |

| Figure 3-57 Message View                                                       | 42 |

|--------------------------------------------------------------------------------|----|

| Figure 3-58 Drag to Chip Array to set I/O Constraints                          | 43 |

| Figure 3-59 Drag to Package View and Set I/O Constraints                       | 44 |

| Figure 3-60 Set I/O Constraints Location Constraint by F3                      | 45 |

| Figure 3-61 Drag to Chip Array and Set Primitive Constraints                   | 46 |

| Figure 3-62 Set Location of Primitive Constraints by Pressing F3               | 47 |

| Figure 3-63 Right-Click Menu of Group Constraints Editor                       | 47 |

| Figure 3-64 Create Primitive Group Constraints                                 | 48 |

| Figure 3-65 Create Relative Group Constraints                                  | 48 |

| Figure 3-66 Create Resource Reservation                                        | 49 |

| Figure 3-67 Copy Location in Chip Array to Set Resource Reservation Constraint | 50 |

| Figure 3-68 Create Clock Assignment Constraints                                | 51 |

| Figure 3-69 Modify Clock Assignment Constraints                                | 51 |

| Figure 3-70 Create Quadrant Constraints                                        | 52 |

| Figure 3-71 Modify Quadrant Constraints                                        | 53 |

| Figure 3-72 Create Hclk Constraints                                            | 54 |

| Figure 3-73 Modify Hclk Constraints                                            | 55 |

| Figure 3-74 Create Vref Constraints                                            | 55 |

| Figure 3-75 Vref Rename Check                                                  | 56 |

| Figure 3-76 Drag to Chip Array to Modify Location                              | 56 |

| Figure 3-77 Drag to Package View to set Vref Constraint Location               | 57 |

| Figure 4-1 Basic Model of Timing Analysis                                      | 59 |

| Figure 4-2 STA Four Timing Paths                                               | 60 |

| Figure 4-3 Process View                                                        | 62 |

| Figure 4-4 Open New Timing Constraints File                                    | 63 |

| Figure 4-5 Create Timing Constraint File                                       | 63 |

| Figure 4-6 Open Timing Constraint File                                         | 64 |

| Figure 4-7 Timing Constraint Editor                                            | 65 |

| Figure 4-8 Netlist Tree View                                                   | 65 |

| Figure 4-9 Constraint Edit View                                                | 66 |

| Figure 4-10 Open Timing Constraint View in Menu                                | 66 |

| Figure 4-11 Right Click to Open the Timing Constraint View | 67 |

|------------------------------------------------------------|----|

| Figure 4-12 Edit SDC File                                  | 67 |

| Figure 4-13 Create Clock Constraint                        | 68 |

| Figure 4-14 Objects                                        | 69 |

| Figure 4-15 Create Clock Constraint                        | 70 |

| Figure 4-16 Clock Constraint List                          | 70 |

| Figure 4-17 Right-click Contents of Clock List             | 70 |

| Figure 4-18 Create Generated Clock Constraints             | 72 |

| Figure 4-19 Right-click Contents of Clock List             | 72 |

| Figure 4-20 Create Clock Latency                           | 73 |

| Figure 4-21 Create Clock Uncertainty                       | 74 |

| Figure 4-22 Create Clock Group Constraints                 | 75 |

| Figure 4-23 Clock Group Member List                        | 75 |

| Figure 4-24 Create I/O Delay Constraints                   | 77 |

| Figure 4-25 Create False Path Constraints                  | 78 |

| Figure 4-26 Create Max/Min Delay Constraint                | 78 |

| Figure 4-27 Create Multicycle Path Constraint              | 79 |

| Figure 4-28 Create Operating Conditions Constraints        | 80 |

| Figure 4-29 Report Timing Creation Interface               | 81 |

| Figure 4-30 Report Timing Interface                        | 81 |

| Figure 4-31 Report High Fanout Nets Create Interface       | 82 |

| Figure 4-32 Report High Fanout Nets Interface              | 82 |

| Figure 4-33 Report Route Congestion Create                 | 83 |

| Figure 4-34 Report Route Congestion Interface              | 83 |

| Figure 4-35 Report Min Pulse Width Interface               | 84 |

| Figure 4-36 Report Min Pulse Width Interface               | 84 |

| Figure 4-37 Report Exception Interface                     | 85 |

| Figure 4-38 Report Max Frequency Interface                 | 85 |

| Figure 4-39 Report Exception Interface                     | 86 |

| Figure 4-40 Report Exception Interface                     | 86 |

| Figure 4-41 View Timing Reporting Interface                | 87 |

| Figure 5-1 Posp File Settings                        | . 89 |

|------------------------------------------------------|------|

| Figure 5-2 Read .posp File                           | . 89 |

| Figure 5-3 Read Timing Constraint File               | . 90 |

| Figure 5-4 Module Operation of Highlighting Key Path | . 91 |

| Figure 5-5 Highlight Module of Key Path in Red       | . 91 |

| Figure 5-6 Key Path Signal Flow                      | . 92 |

| Figure 5-7 Location After Adjustment                 | . 93 |

SUG101-1.9E ix

## **List of Tables**

| Table 1-1 Abbreviations and Terminology |  | 2 |

|-----------------------------------------|--|---|

|-----------------------------------------|--|---|

SUG101-1.9E x

1 About This Guide 1.1 Purpose

## 1 About This Guide

### 1.1 Purpose

This guide describes the physical constraints and timing constraints of Gowin Semiconductor. It also introduces the interface usage and syntax rules of Gowin physical constraints and timing constraints tools. It is designed to help users implement physical constraints and timing constraints. The software screenshots and the supported products listed in this guide are based on Windows 1.9.5 Beta. As the software is subject to change without notice, some information may not remain relevant and may need to be adjusted according to the software that is in use.

## **1.2 Supported Products**

The information in this guide applies to the following products:

- GW2A series of FPGA products: GW2A-18, GW2A-55, GW2A-18C and GW2A-55C.

- GW2AR series of FPGA products: GW2AR-18 and GW2AR-18C

- GW1N series of FPGA products: GW1N-1, GW1N-2, GW1N-2B, GW1N-4, GW1N-4B, GW1N-6, GW1N-9 and GW1N-1S

- GW1NR series of FPGA products: GW1NR-4, GW1NR-4B, and GW1NR-9

- GW1NS series of FPGA products: GW1NS-2, GW1NS-2C and GW1NS-4 and GW1NS-4C

- GW1NZ series of FPGA products: GW1NZ-1

- GW1NSR series of FPGA products: GW1NSR-2C, GW1NSR-2 and GW1NSR-4 and GW1NSR-4C

- GW1NSE series of SecureFPGA products: GW1NSE-2C

- GW1NSER series of SecureFPGA products: GW1NSER-4C

- GW1NRF series of FPGA products: GW1NRF-4B

#### 1.3 Related Documents

The latest user guides are available on the Gowin website. Please see

SUG101-1.9E 1(150)

the related documents at www.gowinsemi.com

- DS102, GW2A series of FPGA Products Data Sheet

- DS226, GW2AR series of FPGA Products Data Sheet

- DS100, GW1N series of FPGA Products Data Sheet

- DS117, GW1NR series of FPGA Products Data Sheet

- DS821, GW1NS series of FPGA Products Package and Pinout

- DS841, GW1NZ series of FPGA Products Data Sheet

- DS861, GW1NSR series of FPGA Products Data Sheet

- DS871, GW1NSE series of FPGA Products Data Sheet

- <u>SUG100</u>, Gowin Yun Yuan Software User Guide

## 1.4 Abbreviations and Terminology

Table 1-1 shows the abbreviations and terminology used in this guide.

Table 1-1 Abbreviations and Terminology

| Abbreviations and Terminology | Meaning                       |

|-------------------------------|-------------------------------|

| FPGA                          | Field Programmable Gate Array |

| I/O                           | Input/Output                  |

## 1.5 Support and Feedback

Gowin Semiconductor provides customers with comprehensive technical support. If you have any questions, comments, or suggestions, please feel free to contact us directly using the information provided below.

Website: www.gowinsemi.com

E-mail: support@gowinsemi.com

SUG101-1.9E 2(150)

# 2 Introduction

Gowin Constraint Editor includes the Physical Constraints Editor (FloorPlanner) and the Timing Constraints Editor. Users can employ these editors to implement physical constraints and timing constraints.

Gowin FloorPlanner tool is developed by Gowin for place & route and physical constraints editing. It can read and modify the attributes and location of I/O, Primitive, block (B-SRAM, DSP) and Group, etc. It also supports the generation of new layout and constraints files based on the associated configuration. The I/O attribute and location information on primitives and modules are specified in the provided files. Gowin FloorPlanner provides a simple layout and constraint editing function that is designed to improve the efficiency with which users write physical constraint files.

The timing constraint editor can be used to create and modify timing constraint files, which can provide efficient network list lookup and improve the efficiency with which users write timing constraint files.

The timing constraint editor has the following features:

- Calculates delay value according to a specific timing model through the signal transmission path and then compare this value with the expected value to determine whether the user design meets the timing requirements with the purpose to improve work efficiency;

- Provides the default basic clock and timing analysis for the cross-clock domain, including two timing reports formats: HTML and text (HTML by default);

- Supports the common timing constraints (including clock constraint, I/O port constraint, and timing path constraint), and the common timing report directives;

- Supports the priority commonly used;

- Inspects setup time, hold time, recovery time, removal time, and MPW by default, and customizes the timing report content according to the timing report instructions.

SUG101-1.9E 3(150)

3 Physical Constraints 3.1 Function

# 3 Physical Constraints

Users can employ the Gowin FloorPlanner tool to create and modify physical constraint files. These files provide tabulated constraint editing and efficient netlist lookup that can improve the efficiency of physical constraint files written.

#### 3.1 Function

Gowin FloorPlanner has the following features:

- Reads user design file and constraint file and outputs constraint file;

- Displays I/O port, primitive, and group constraints in user design files;

- Creates, edits, and modifies constraints information:

- Supports Chip array grid mode, macrocell mode, and primitive mode;

- Supports Package View based on package;

- Displays chip array and package view synchronously;

- Supports real-time display and differential display of a constrained position;

- Supports setting position information by dragging;

- Supports One Hit Drag generating constraints;

- Supports I/O port attributes configuration and batch configuration;

- Supports Clock Assignment display and editing;

- Supports legality check of constraints information.

#### 3.2 Start FloorPlanner

Two methods can be employed to open FloorPlanner:

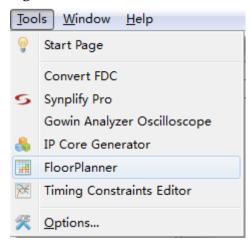

1. Click "IDE > Tools" and open "FloorPlanner", as shown in Figure 3-1.

SUG101-1.9E 4(150)

3 Physical Constraints 3.2 Start FloorPlanner

Figure 3-1 Start FloorPlanner From Tools Menu

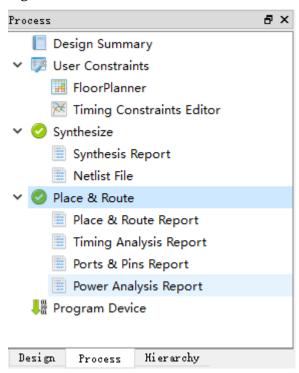

2. After creating a project in Process window and running Synthesize, double-click "FloorPlanner", as shown in Figure 3-2.

Figure 3-2 Process View

#### Note!

- If the Gowin FloorPlanner is required for constraints, the netlist file should be added first.

- When opening Gowin FloorPlanner from the tools menu, the user needs to load the netlist file through the "File > new".

- When opening Gowin FloorPlanner using the second approach, the netlist file will be automatically loaded.

SUG101-1.9E 5(150)

## 3.3 Create and Open the Constraint File

Physical constraint files are required for the constraint on position and attribute of I/O and Primitive in the project. Two ways are available here:

- 1. Manual writing;

- 2. Outputs the constraints file using Gowin FloorPlanner.

#### 3.3.1 Create Constraints File

The constraints file can be created by the following steps:

- Click "File > New" to open the "New" dialog box.

- 2. Select "Physical Constraints File", as shown in Figure 3-3.

Figure 3-3 Open New Physical Constraints File

#### Note!

- You can also open a "New" file in the following two ways:

- Using short cut "Ctrl+N";

- Clicking on the "New" icon on the toolbar.

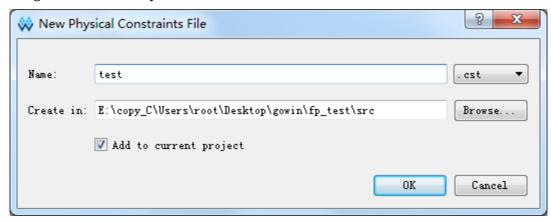

- Click on the "OK" button, and the dialog box shown in Figure 3-4 will appear.

SUG101-1.9E 6(150)

Figure 3-4 Create Physical Constraints File

- Name: Input the name of the physical constraint file. The suffix of CST or .ucf are supported.

- Create in: Click "Browse..." button and select the path in which the constraint file will be saved. The default path in which files are saved is the src folder.

- Add to current project: If this option is checked, the constraints file will be automatically added to the project.

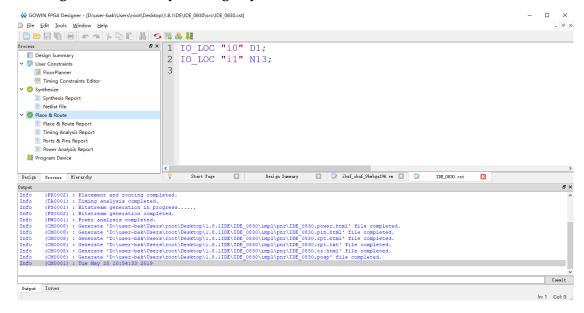

Once the new physical constraints file has been added, it will open, and the user can edit it according to the Gowin physical constraint syntax. The constraints file can be manually written, as shown in Figure 3-5.

Figure 3-5 Manually Writing Physical Constraints File

### 3.3.2 FloorPlanner Output Constraint Files

The Gowin FloorPlanner can output the new physical constraints file or modified physical constraint files. The steps are as following:

1. Start the FloorPlanner as described in 3.2 Start FloorPlanner;

SUG101-1.9E 7(150)

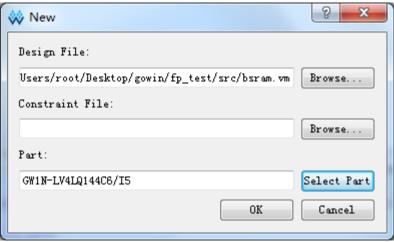

- 2. From the File menu, choose "File > New..." to open the "New" dialog, as shown in Figure 3-6;

- Enter the netlist files, select the device type, and click "OK".

Figure 3-6 New FloorPlanner

#### Note!

- Start the FloorPlanner using the first method described in 3.2.

- You can also open a "New" project by using one of the followings:

- Use the shortcut: "Ctrl+N".

- Click on the "New" icon in the toolbar.

The following operations can be performed in the interface of

#### FloorPlanner:

- 1. Distribute the pin location by dragging.

- 2. Click "Save" to output the constraints files.

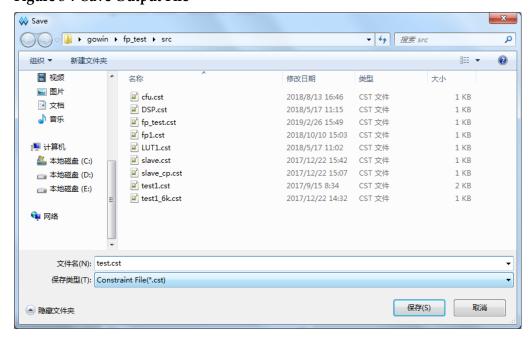

- 3. If required, modify the file name in the "Save" dialog box, as shown in Figure 3-7.

Figure 3-7 Save Output File

SUG101-1.9E 8(150)

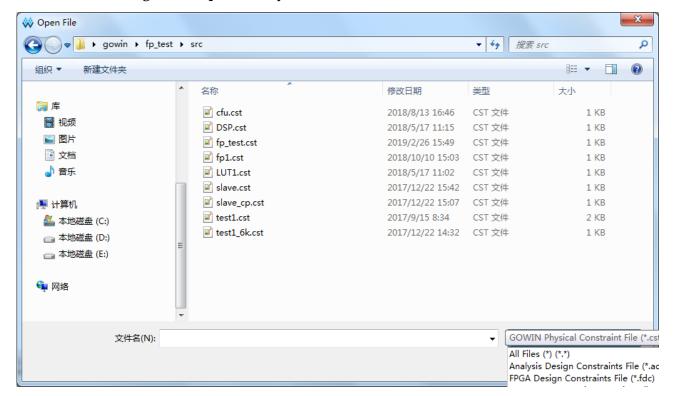

### 3.3.3 Open the Constraints File

The steps to open the constraints file are as follows:

- 1. In the IDE view, click "File > Open".

- Open the "Open File" dialog box, as shown in Figure 3-8.

Figure 3-8 Open the Physical Constraint File

#### Note!

- Alternatively, you can also open the "Open File" dialog box by the following two ways:

- Using the shortcut: Ctrl + O.

- By clicking "Open" icon on the toolbar.

- Select the directory in which the physical constraints file is saved and open the selected file.

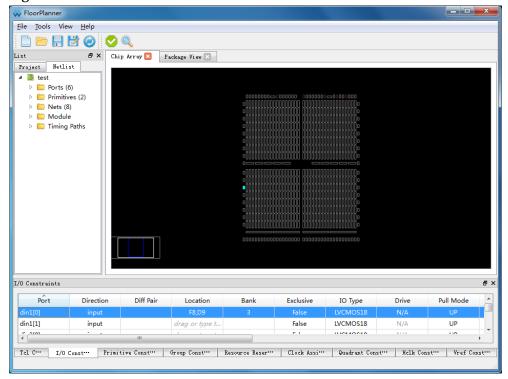

### 3.4 FloorPlanner View

Create or open the FloorPlanner (including the netlist file), as shown in Figure 3-9.

The interface includes the menu, List, Chip Array, Package View, Message, and various constraints editing views, etc.

SUG101-1.9E 9(150)

Figure 3-9 FloorPlanner View

#### 3.4.1 Menu

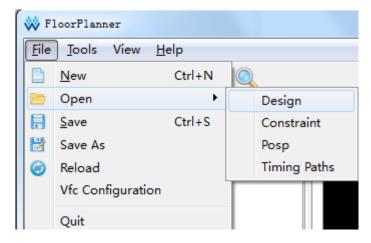

The FloorPlanner includes the "File", "Tools", "View", and "Help" options.

#### File

The file view is shown in Figure 3-10.

Figure 3-10 File

- New: Create new project, add user design, constraint and set chip information, etc., as shown in Figure 3-6;

- Open: Open the user netlist file, constraints file, device layout information file, or timing path file;

SUG101-1.9E 10(150)

Reload: Reload the cst file after modifying and saving it to a disk or project;

- Save: Save the modified information of the current constraints and override the original constraints file information;

- Save As: Output the modified information of the current constraints information to the file specified by the user. The file name of the network list is used as the constraints file name by default; however, this can be modified by the user;

- Quit: Close Gowin FloorPlanner.

#### Note!

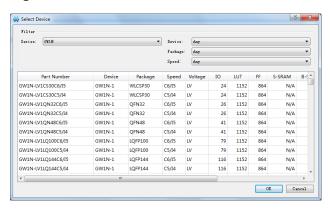

The Select Part option is used to select the chip, package information to support all Gowin FPGA devices, as shown in Figure 3-11.

Figure 3-11 Select Device

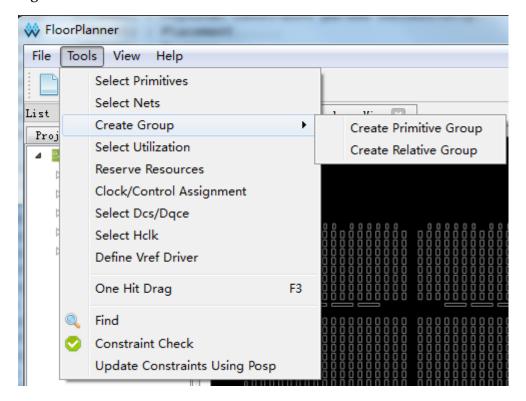

#### **Tools**

The tools view is shown in Figure 3-12. The tools functions are as follows:

- Input constraints information.

- Support One Hit Drag, Find, and Constraint Legality Check functions.

Display various constraints information in real time in the constraint editor, and the corresponding location information will be displayed in the Chip Array and Package View. The menu functions are as follows:

SUG101-1.9E 11(150)

Figure 3-12 Tools

#### Select Primitives.

- a) Select Primitive to create the corresponding constraints, click menu, and the dialog box will open, as shown in Figure 3-13.

- b) Find primitives by "Name" or "Type", and select the corresponding primitive.

- c) Click "OK" to generate the constraints information.

#### Note!

- The constraint information is displayed in the "Primitive Constraints" area at the bottom of the main interface.

- The user can set the location information by entering or dragging in the editing view.

- The location is highlighted in light blue in the Chip Array.

SUG101-1.9E 12(150)

8 Primitive Finder All Primitives Filter Name: \* \* Type: • Name Type 1 alu\_inst INS\_ALU 2 dffe\_inst\_Z INS\_DFFE Ξ 3 dle\_inst\_Z INS\_DLE 4 lut3\_inst0 INS\_LUT3 5 lut4\_inst0 INS\_LUT4 6 lut4\_inst1 INS\_LUT4 7 lut5\_inst INS\_LUT5 8 lut6\_inst INS\_LUT6 9 lut7\_inst INS\_LUT7 0K Cancel

Figure 3-13 Primitive Finder View

The Create Group menu includes the Create Primitive Group and Create Relative Group options. The functions are as follows:

#### **Create Primitive Group**

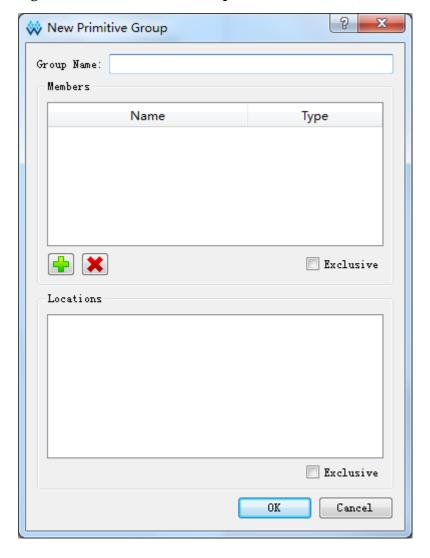

1. Click "Create Primitive Group", and the dialog box will open, as shown in Figure 3-14.

SUG101-1.9E 13(150)

**Figure 3-14 New Primitive Group**

- 2. Set the group name, primitive, location, and group exclusive information according to your needs.

- 3. Add and remove the primitives by clicking on the "\* and "\* icons respectively. The primitive group information is shown in Figure 3-15.

SUG101-1.9E 14(150)

Figure 3-15 Correct Primitive Group Interface

#### Note!

- Group name, primitive, and group location are required.

- The location information for the group can be input in the following ways:

- Input manually.

- Before creating the group constraints, copy the location and paste it into "New Primitive Group > Location" in the "Chip Array".

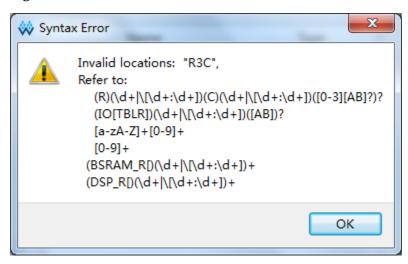

- 4. After creating the primitive group, click "OK", and the tool will check the syntax of the group location information.

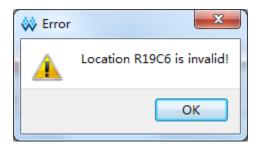

- a) If the location information is not acceptable, a prompt will appear, as shown in Figure 3-16 and Figure 3-17. Modify the location information accordingly.

SUG101-1.9E 15(150)

Figure 3-16 Invalid Position

Figure 3-17 Invalid Position

b) If no error exists, click "OK", and the available location will be displayed in the chip array.

See the newly generated group constraints in the Group Constraints area that is located at the bottom of the main view.

Double click on the group constraints and the dialog box will open for further editing, as shown in Figure 3-14.

#### Create the relative group

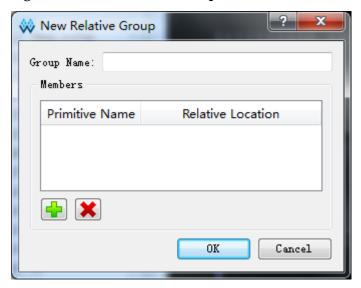

- 1. Create a constraints group with a relative position. Click on the menu and the dialog box will open, as shown in Figure 3-18.

- 2. Set the group name, primitive, and the relative position information that corresponds to each primitive.

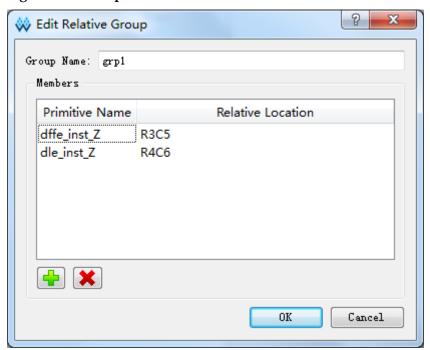

- 3. Add and remove the primitive by clicking on the "and" and icons respectively. The Relative Group Constraints that are created successfully will be displayed, as shown in Figure 3-19.

SUG101-1.9E 16(150)

Figure 3-18 New Relative Group

Figure 3-19 Group Interface in Correct Relative Position

#### Note!

- Group name, primitive, and relative location is required.

- The location information for the group can be inputted in the following ways:

- Input manually.

- Before creating the group constraint, copy the location and paste it into "New Relative Group > Relative Location" in the "Chip Array".

- Click the "OK" button after configuring the group. The constraints information will appear in the "Group Constraints" area at the bottom of the main interface.

Double click the group constraints, and the dialog box will appear for

SUG101-1.9E 17(150)

further editing, as shown in Figure 3-19.

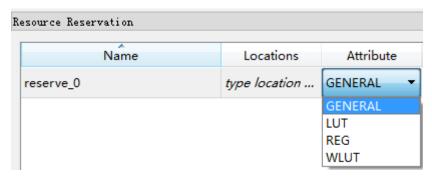

#### **Reserve Resources**

- 1. Click to create a new constraint in the "Resource Reservation" at the bottom of the main interface.

- 2. Double-click "Location" to input the constraint position.

- 3. Double-click "Attribute" to set the attributes for the reserved location, as shown in Figure 3-20.

#### Note!

The "Name" attribute is used to distinguish between different constraints. The name cannot be modified.

Figure 3-20 Reserved Constraint

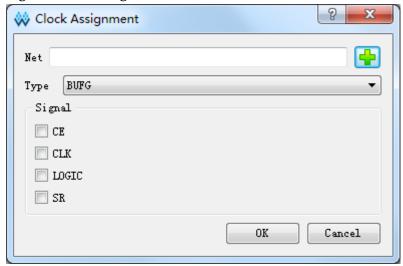

#### **Clock/Control Assignment**

Create a Clock constraint, and the number of constraints are limited, and check it via a constraint validity. Click the menu, and the dialog box will open, as shown in Figure 3-21. The operations are as follows:

- 1. Click " to select the corresponding net.

- 2. Select "BUFG", "BUFG [0]~[7]", "BUFS" and "LOCAL\_CLOCK" via the "Type" drop-down list.

- 3. Configure the signal via the "CE", "CLK". After configuring, click "OK" to generate the constraint information in the "Clock Assignment". Double click in the edit view. The dialog box for editing will open, as shown in Figure 3-21.

#### Note!

When selecting LOCAL\_CLOCK in Type, the Signal check will be in grey and can not be configured.

SUG101-1.9E 18(150)

**Figure 3-21 Timing Constraint**

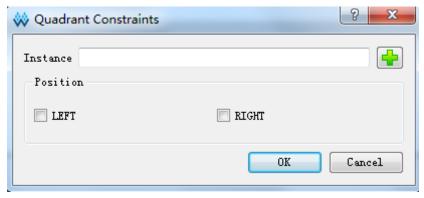

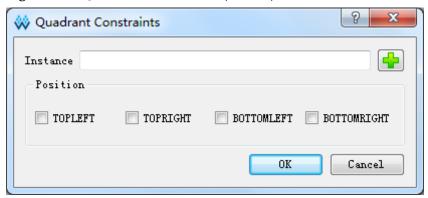

#### Select Dcs/Dqce

Create quadrant constraints for DCS and DQCE. Specify the instance to the specific quadrant according to the chip quadrant distribution, as shown in Figure 3-22 and Figure 3-23.

The related operations are as follows:

- 1. Select the corresponding DCS/DQCE devices by clicking on the " icon:

- 2. Configure the quadrant positions via the checkboxes under "Position";

- 3. Click "OK", the constraints information is generated in the "Quadrant Constraints" window at the bottom of the main interface. In the editing window, double-click to open the constraint dialog box again for editing.

#### Note!

Quadrant constraints cannot be added if there is no existing DCS/DQCE device.

The constraints editing window of "Quadrant Constraints" of GW2A-18, GW2AR-18, GW2A-55, GW2A-18C, GW2AR-18C and GW2A-55C series is shown in Figure 3-23.

Figure 3-22 Quadrant Constraints (GW1N)

SUG101-1.9E 19(150)

Figure 3-23 Quadrant Constraints (GW2A)

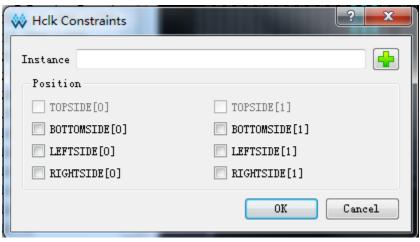

#### Select Hclk

Create HCLK constraints on primitives and specify the constraint locations of the chip, as shown in Figure 3-24.

The related operations are as follows:

- 1. You can select the device by clicking on the " icon.

- 2. Configure the quadrant positions using the checkboxes that appear under the "Position".

- 3. Click "OK", the constraints information is generated in the "Quadrant Constraints" window at the bottom of the main interface. In the editing window, double-click to open the constraint dialog box again for editing.

#### Note!

- HCLK constraints cannot be added if there is no existing compatible device.

- The positions that are available vary according to the different devices in the project.

Figure 3-24 Hclk Constraints

#### Define the Vref Driver

Create a new Vref Driver for configuring the Vref of the I/O port, and

SUG101-1.9E 20(150)

click the menu to create a new constraint in "Vref Constraints" at the bottom of the main interface, as shown in Figure 3-25.

**Figure 3-25 Vref Constraints**

#### Note!

- Specify the Vref constraint position by dragging.

- Modify the Vref name by double-clicking.

#### One Hit Drag

Quickly create primitive and I/O constraints information by following steps:

1. In Netlist window, select primitive or port, as shown in Figure 3-26. Figure 3-26 Select One Hit Drag Primitive

2. In Chip Array, select one or more location information, as shown in Figure 3-27.

SUG101-1.9E 21(150)

Figure 3-27 Select One Hit Drag Location

3. Click "Tools > One Hit Drag" or press "F3" to generate the constraint information directly, as shown in Figure 3-28.

Figure 3-28 One Hit Drag Constraints

#### Note!

Select the rectangle location by pressing "Ctrl" and clicking the left mouse button.

#### **Find**

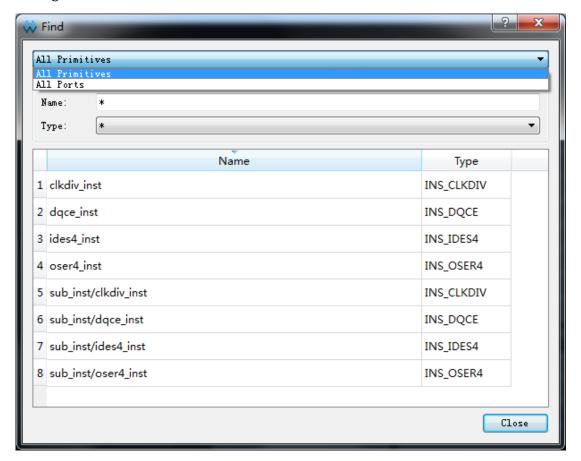

Quickly find primitives, the I/O port, and edit the corresponding constraints information on the primitive or port by right-clicking menu, and the dialog box will appear, as shown in Figure 3-29.

The related operations are as follows:

- 1. Find by selecting "All Primitive" or "All Port".

- 2. Select the corresponding item, right-click "Edit \* \* \* Constraint" to edit the constraints information at the bottom of the main interface.

SUG101-1.9E 22(150)

Figure 3-29 Find View

#### **Update the Constraints Using Posp**

Update the constraints information to the location information in the device layout information file.

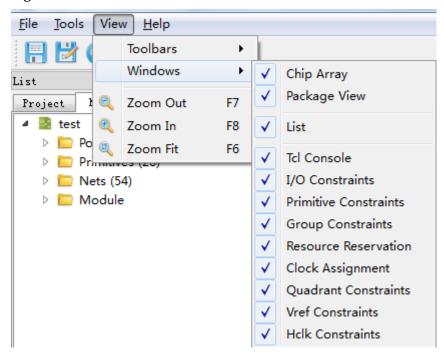

#### View

As shown in Figure 3-30, the view contains commands that can be used to control the toolbars, display windows, zoom in and out/fit chip array, and package view. A brief introduction to the sub-menus is presented below:

- Toolbars: Display shortcut buttons in toolbars.

- Windows: Display different windows, as shown in Figure 3-31.

- Zoom Out: Zoom out on the chip array or package view.

- Zoom In: Zoom in on the chip array or package view.

- Zoom Fit: Zoom in on the chip array or package view according to the view size.

SUG101-1.9E 23(150)

Figure 3-30 View

Figure 3-31 Windows

#### Help

The help contains information about the software version and associated copyright information. Click on the "About" option and the prompt box will appear, as shown in Figure 3-32.

Figure 3-32 Help

# 3.4.2 Netlist and Project View

The netlist and Project views can display device information, user

SUG101-1.9E 24(150)

design, and path information for the constraints file, netlist information, etc.

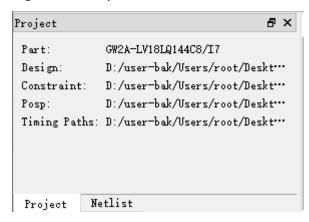

#### **Project**

The project interface is shown in Figure 3-33. This displays the chip information related to the project, such as Part Number, the design files constraint files, device layout information file, and timing path file entered by the user.

Figure 3-33 Project View

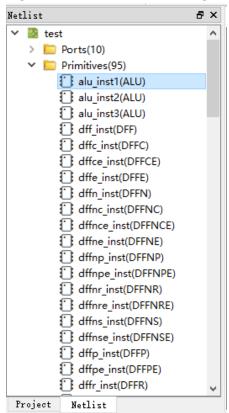

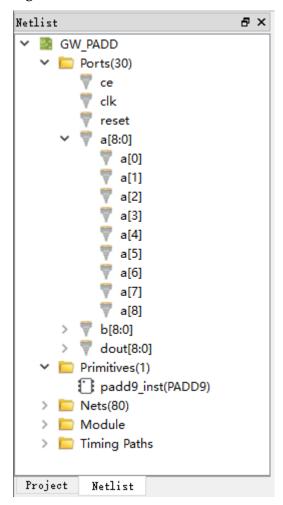

#### **Netlist View**

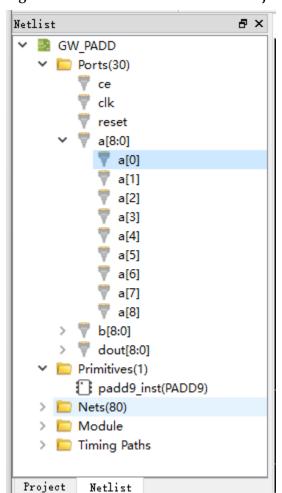

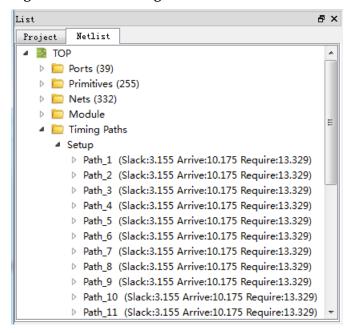

As shown in Figure 3-34, the netlist displays the Ports, Primitives, Nets, Module, Timing paths, and corresponding quantity in the tree structure.

SUG101-1.9E 25(150)

Figure 3-34 Netlist View

#### Note!

The name of the port, primitives, etc. in the full path and order is displayed alphabetically by default.

• Display port and net via combining bus and non-bus, as shown in Figure 3-35.

SUG101-1.9E 26(150)

Figure 3-35 Show Bus and Non-Bus Conjunctively

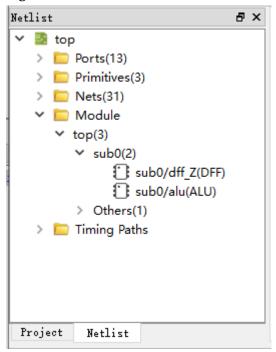

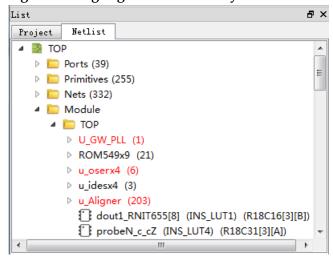

Display the module in the hierarchy and show the number of instances in each module when placing the mouse on a module in the module list, as shown in Figure 3-36.

SUG101-1.9E 27(150)

Figure 3-36 Hierarchical View

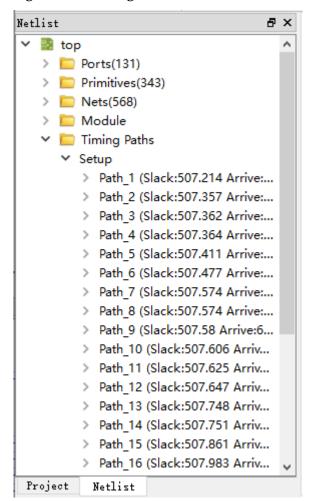

The sequential path is listed in the slack time from small to large, as shown in Figure 3-37.

SUG101-1.9E 28(150)

Figure 3-37 Timing Path

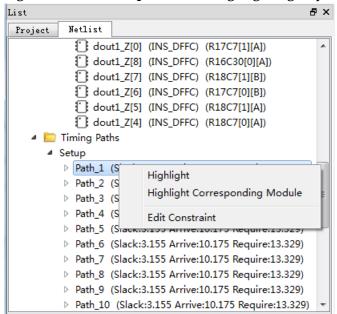

#### **Netlist View**

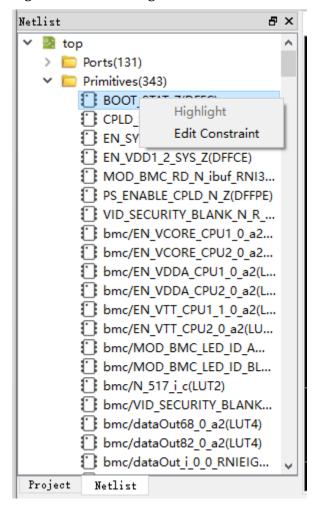

Netlist includes a right-click menu with the following functions:

- 1. Highlight the corresponding constraints location in the chip array.

- 2. Edit the corresponding constraints information.

#### Note!

If the current primitive, net or port has no position constraints, the highlighted function is not available, as shown in Figure 3-38.

SUG101-1.9E 29(150)

Figure 3-38 Netlist Right-Click Functions

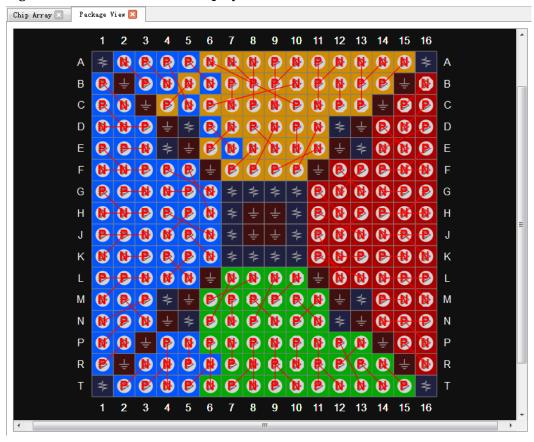

# 3.4.3 Package View

As shown in Figure 3-39, the package view displays the package information for each chip based on the chip package information, displaying pins for I/O, power supply, ground, etc. When placing the mouse in a position, the I/O information of the location will be shown, including I/O type, bank, and LVDS.

SUG101-1.9E 30(150)

Package View 🗵 Chip Array 🔣 9 10 11 12 13 14 15 16 В В C С D ≉ Ε 4 Ε ÷ ♦ ♦ **(4)** F **(** G G Н ≉ ≉ **(4) (4) (4)** ♦ ♦ ♦ ♦ ≉ ≱ ≉ K K <u></u> † ₽ L ≉ Ν Ν Р R R 5 9 11 12 15 6 8 10 13 16

Figure 3-39 Package View

User I/O and multiplexing I/O, power, ground, and dedicated pins are also marked with different symbols and colors. The different symbols and colors used for the various pins are defined below:

- Red means BANK0 pins; Green means BANK1 pins.

- Blue means BANK2 pins; Yellow means BANK3 pins.

- "D" means single-ended and differential I/O in BANK0; The filling color changes according to the BANK.

- "D" means multiplexing I/O in BANK3; The filling color changes according to the BANK.

- "\$\frac{1}{2}" means VCC. The filling color does not change.

- "= " means VSS. The filling color does not change.

- "E" means bluetooth interface. The filling color does not change.

- "b" means NC.

As shown in Figure 3-40, the package view includes a right-click menu. The relevant functions are as follows:

SUG101-1.9E 31(150)

- Support zoom in/out view, and show differential IO pairs.

- Switch to display between the Top and Bottom View. The Top View is the default view.

Figure 3-40 Right-Click Function of Package View

In the package view, select "Show Differential IO Pairs" by right-clicking and selecting "Display difference pair" from the menu. As shown in Figure 3-41, the items in a differential pair are connected by a red line.

Figure 3-41 Differential Pair Display

The package view displays the I/O port constraints position, which can be set in the following two ways:

SUG101-1.9E 32(150)

- Drag the constraints location of the I/O port in the package view.

- Drag the I/O Port to the package view from the "Netlist" or "I/O Constraints" at the bottom.

#### Note!

- When dragging, the mouse will display the name of the port that is being dragged.

- "S" indicates that the dragged port cannot be placed at the desired location.

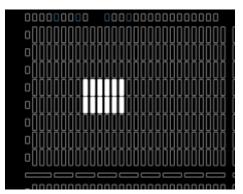

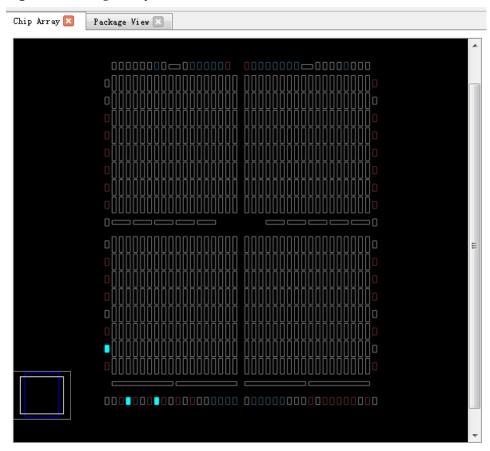

## 3.4.4 Chip Array View

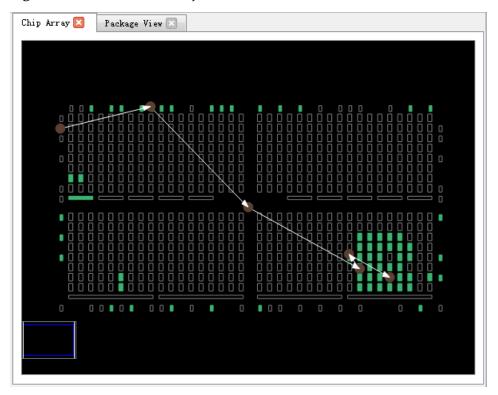

The chip array view of the FloorPlanner is shown in Figure 3-42. The chip array shows the distribution of IOB, CFU, and DSP according to the chip ranks and displays all constraint locations in real-time and support functions of enlarging, reducing, repeating location, suspending, dragging and dropping, etc.

The IOB is all IOB locations of the die, and is distinguished by different colors:

- White corresponds to the I/O location.

- Red is the location of an unpackaged I/O.

- The blue IOB in the GW2AR-18, GW1NR-4, GW1NR-4B, GW1NR-9, and GW1NSR-2C series indicates the I/O of embedded SDRAM.

Figure 3-42 Chip Array View

SUG101-1.9E 33(150)

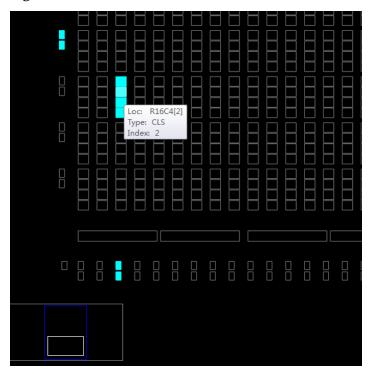

Chip array includes grid mode, macro element mode, and primitive mode.

Grid mode: Macroscopically display constraint position in grid scale, as shown in Figure 3-43.

Figure 3-43 Grid Constraint

Macro element mode: Display constraint position in CLS, block, etc., as shown in Figure 3-44.

**Figure 3-44 Macro Element Constraint**

Primitive mode: Display constraint position in reg, lut, etc., as shown in

SUG101-1.9E 34(150)

Figure 3-45. Figure 3-45 Primitive Constraint

The chip array supports the following dragging functions:

- Drag from array: Applies to the constraint position occupied by the particular primitive. Can be dragged optionally in Array.

- Drag from Netlist to Array to generate and specify constraints.

- Drag from Edit to Array to specify constraints.

The built-in Chip View is used to display the current view position relative to the entire chip in real time. The Chip Array view follows when dragging the white box in the chip. The Chip Array distinguishes between constraint type and displays the constraint position in different colors. The meaning of each color is as follows:

- White: Display the constraint position in the selection state or highlighted state.

- Dark blue: Display the position information for the reserved constraints, indicating that the position cannot be occupied again.

- Light blue: Display the I/O and Primitive locations constrained in one grid or within a range.

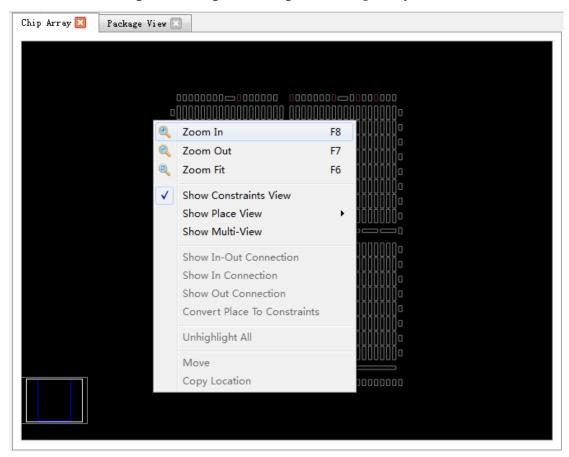

The chip array incorporates a right-click menu. The functions are as follows:

- Zoom in/out view.

- Show constraints in view, place view, and multi-view.

- Show I/O connection.

- Convert place to constraints.

- Eliminate highlighting.

- Remove and copy location information.

#### Note!

• If grid, block, reg, or lut, etc. are selected in the view, the "Copy Location" is

SUG101-1.9E 35(150)

- available on the right-click menu.

- If no grid is selected, the function is not available, as shown in Figure 3-46.

- Select an area by holding "Ctrl" and clicking on the left mouse button. Copy the location of the selected area by right-clicking and selecting the "Copy the Location" option. The replicated location can be pasted directly into any constraints in the editor.

Figure 3-46 Right-Clicking on the Chip Array

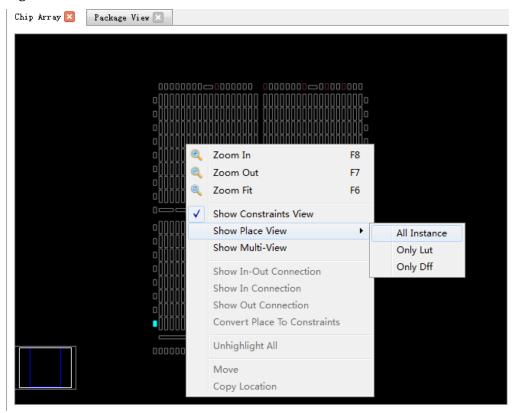

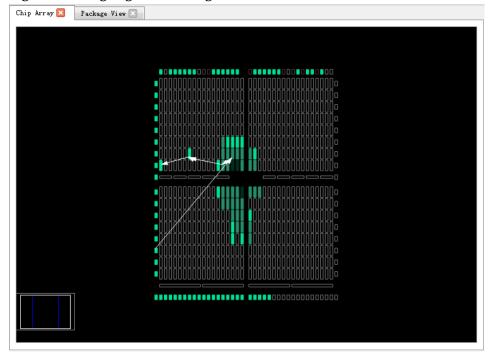

The Show Place View also shows the Lut and Reg density, as shown in Figure 3-47.

- ALL Instance: Shows all Instance places. Light green indicates less than five, green indicates six to ten, and dark green indicates more than ten.

- Only Lut: Shows all lut places. Light green indicates less than two, green indicates three to four, and dark green indicates more than four.

- Only Dff: Shows all reg places. Light green indicates less than two, green indicates three to four, and dark green indicates more than four.

SUG101-1.9E 36(150)

Figure 3-47 Show Place View

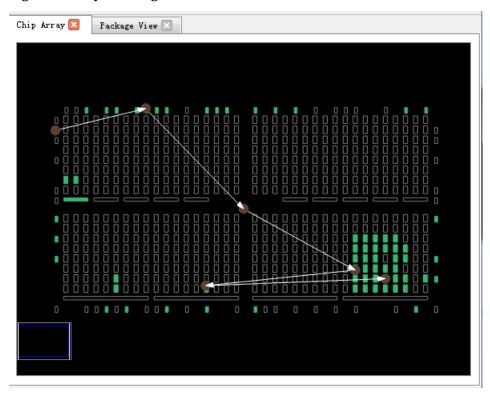

The chip array view also highlights the timing paths, as shown in Figure 3-48.

Figure 3-48 Highlighted Timing Path

SUG101-1.9E 37(150)

#### 3.4.5 Constraint View

The constraint view includes I/O constraints, primitive constraints, group constraints, etc., which are used to display the detailed information of each constraint and provide the constraints editor function and the drag position function. A brief introduction to each view is provided below.

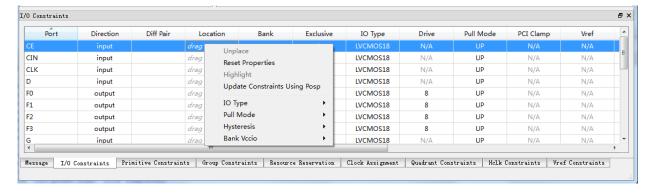

#### I/O Constraints

The I/O constraints view is as shown in Figure 3-49. The available functions are as follows:

- Display all attributes and constraints information of the I/O port in the user design, such as direction, bank, I/O type, pullMode of port, etc.

- Provide the functions for editing constraints location, attributes, etc.

- Change the constraints information by dragging, double-clicking, etc.

#### Note!

- Set the I/O location information by dragging or double-clicking.

- Display the I/O name when dragging/dropping the I/O.

- When dragging the I/O into the chip array, the placed position lightens, and the color of the implacable position brightens.

- After setting, the constraint position in the chip array is highlighted in light blue, and the constraint position in the package view is highlighted in orange.

The functions available on the right-click menu are as follows:

- Cancel placement;

- Reset port attributes;

- Highlight the constraint position;

- Update the constraints according to the device layout file;

- Set the I/O type, turnover rate, pull mode, drive mode, BANK voltage, etc;

- The right-click menu supports bulk modification of the port attributes.

#### Note!

Users can select multiple ports. If multiple ports have the same property values, they can be configured uniformly via the right-click menu.

Figure 3-49 I/O Constraint View

SUG101-1.9E 38(150)

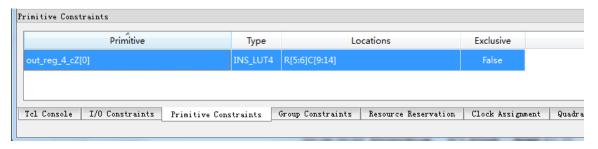

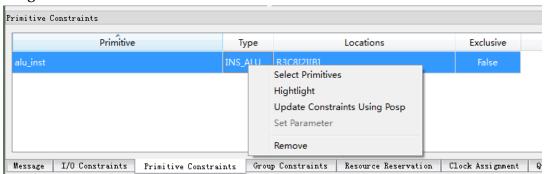

#### **Primitive Constraints**

The primitive constraints view is shown in Figure 3-50. The functions as follows:

- Display the name, type, location, and exclusive information for all primitive constraints.

- Editing.

#### Note!

- Modify the location information by dragging or double-clicking the input.

- Select exclusive information by double-clicking.

- Right-clicking on the menu allows the user to highlight constrained positions;

remove, add, and update constraints; and set the parameter value.

- The syntax and acceptability of the location will be checked when the primitive constraints are manually inputted. The error message dialog box will be as shown in Figure 3-16 and Figure 3-17.

Figure 3-50 Primitive Constraints View

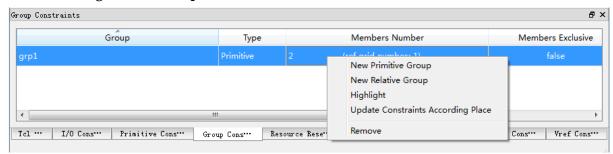

#### **Group Constraints**

The group constraints view is shown in Figure 3-51. The functions are as follows:

- Display the name, type, number of primitive, location, and exclusive information, including primitive and relative.

- As shown in Figure 3-15 and Figure 3-19, double-click on the corresponding group, open the dialog box and edit the constraint information.

- The right-clicking menu allows the user to highlight constraints positions; remove, add, and update constraints; and set the parameter value.

SUG101-1.9E 39(150)

Figure 3-51 Group Constraints View

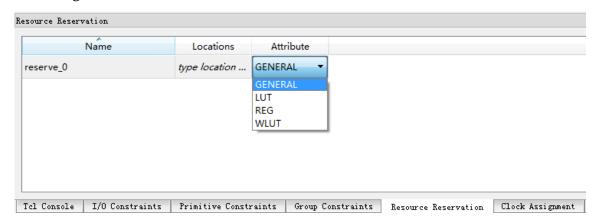

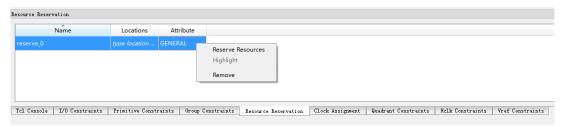

#### **Resource Reservation**

The resource reservation view is shown in Figure 3-52. The functions are as follows:

- Display location information for all the currently reserved constraints.

- The right-clicking menu allows the user to highlight constrained positions, and remove, add, and update constraints.

- The name is used to distinguish between the usage constraints. It cannot be modified.

#### Note!

Users can modify the location information by dragging or double-clicking on the input.

Figure 3-52 Resource Reservation View

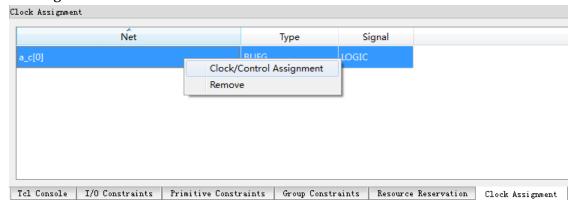

#### **Clock Assignment**

The clock assignment view is shown in Figure 3-53. The functions are as follows:

- Display information on current clock constraints.

- The right-clicking menu allows users to add and remove clock constraints.

#### Note!

- Double-click to edit.

- If no location information is available, the clock constraint does not support the drag/drop function.

SUG101-1.9E 40(150)

The clock constraint view is shown in Figure 3-21.

Figure 3-53 Clock Constraint View

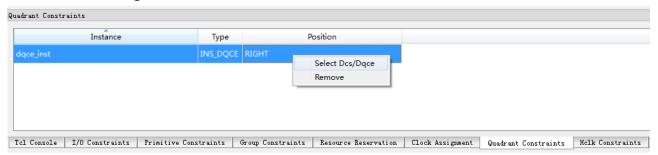

#### **Quadrant Constraints**

The quadrant constraints view is shown in Figure 3-54. The functions are as follows:

- Display all quadrant constraints, including instance name, type, and quadrant location.

- The right-click menu allows the user to add new quadrant constraints and remove the existing constraints.

#### Note!

- The quadrant constraints are valid only for DCS and DQCE devices.

- The quadrant constraint is shown in Figure 3-22 and Figure 3-23.

Figure 3-54 Quadrant Constraints View

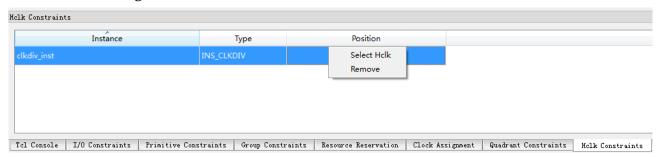

#### **Hclk Constraints**

The Hlk constraints view is as shown in Figure 3-55. The functions are as follows:

- Display the location constraints for each instance for hclk, including instance name, type, and quadrant location.

- The right-click menu allows the user to add new constraints and remove the existing constraints.

The create clock constraint is shown in Figure 3-24.

SUG101-1.9E 41(150)

Figure 3-55 Hclk Constraints View

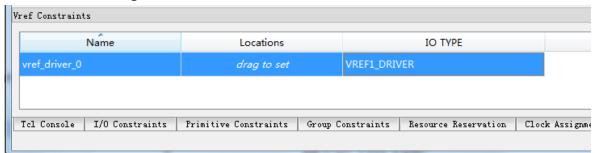

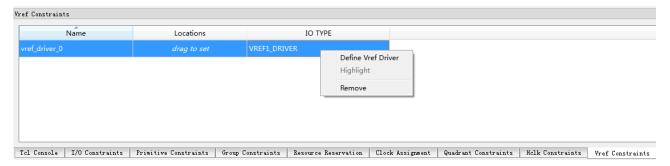

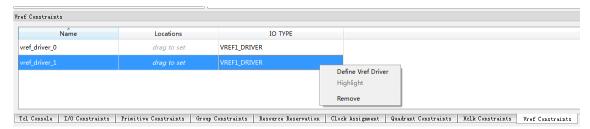

#### **Vref Constraints**

The Vref constraints view is shown in Figure 3-56. The functions are as follows:

- Display Vref driver information defined by the user. The user can customize the Vref name and location.

- The right-click menu allows the user to add and remove constraint information.

#### Note!

Set location information by dragging.

Figure 3-56 Vref Constraints View

# 3.5 Tcl Console View

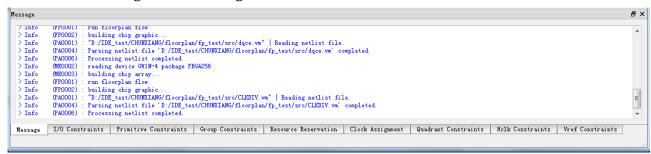

The Message View is shown in Figure 3-57. The output result is displayed.

Figure 3-57 Message View

SUG101-1.9E 42(150)

# 3.6 Create Constraints - Drag Mode

The constraints editor supports the creation of I/O constraints, primitive, group, esource, ock, quadrant, Hclk and Vref. Users can create constraints on the tools. See <u>3.4.1 Menu for details</u>.

#### Note!

You can also create constraints in other ways. Take "drag/drop", for instance. This section describes how to generate a onstraint by dragging and dropping.

## 3.6.1 Set I/O Constraints Position

Users can set the I/O constraints position via the following process:

After initiating the FloorPlanner and reading the design file, the constraints for all ports in the netlist are automatically loaded into the I/O constraints editor.

You can drag in the following two ways:

- 1. In Netlist (on the left), select port and drag it to the chip array.

- In I/O constraints editor (located below), select constraints and drag it to the chip array. Place it if permitted. The constraints location will then be changed to the IOB Location, as shown in Figure 3-58.

Floor Flanner

Fle Sook View Help

List

Project

Authority Set

Chip Array

Fackage View

Project

Form (S)

Chip Array

Fackage View

Figure 3-58 Drag to Chip Array to set I/O Constraints

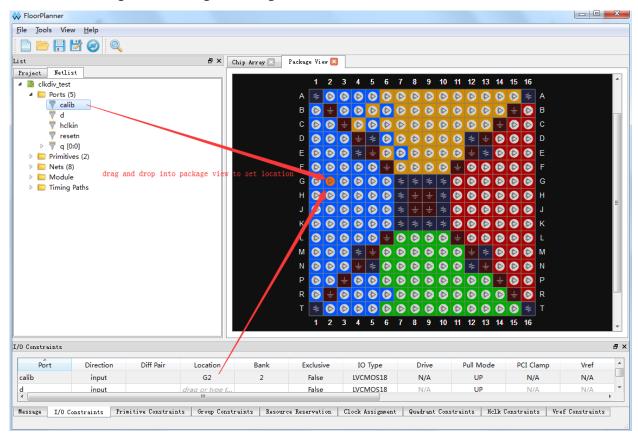

Drag to package view to set the I/O constraints. The steps are as follows:

SUG101-1.9E 43(150)

In Netlist, drag port to package view and place it in a permissible location.

2. Change the location of the constraints to the pin in the package view, as shown in Figure 3-59.

#### Note!

You can also set I/O constraints by dragging the constraints in the I/O constraints editor to the package view.

Figure 3-59 Drag to Package View and Set I/O Constraints

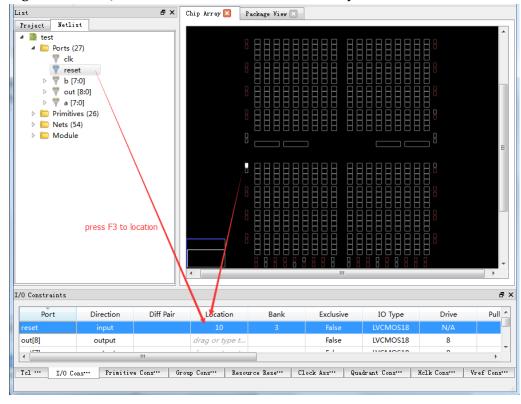

As shown in Figure 3-60, users can set the constraint location for the port in the constraints editor. The steps for doing this are as follows:

- Select port in Netlist.

- Select IOB in chip array.

- 3. Press "F3".

#### Note!

You can also select IOBLOCK by zooming out on the chip array.

SUG101-1.9E 44(150)

Figure 3-60 Set I/O Constraints Location Constraint by F3

In addition to the three methods described above, users can also enter the required constraint location by directly double-clicking on the I/O constraints location.

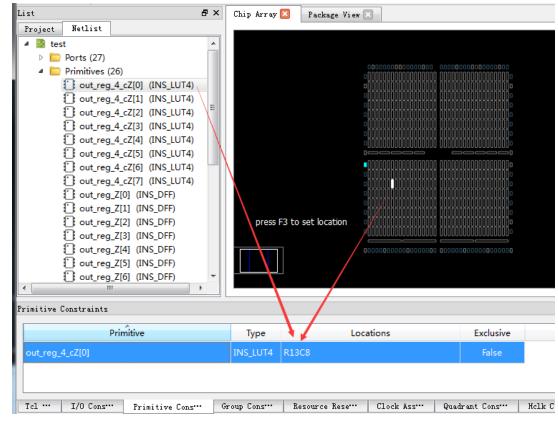

## 3.6.2 Create Primitive Constraints

Primitive constraints can be created in two ways. The steps are as below.

#### Set primitive constraints by dragging to chip array

- In Netlist, double-click or right-click on the menu. Select "Edit Constraint" and generate primitive constraints, and add the corresponding primitive constraints to the primitive constraints editor.

- 2. After generating the constraints, set the constraint location, select the corresponding constraints in the primitive constraints editor, and drag it to the chip array, as shown in Figure 3-61.

#### Note!

- You can also right-click the menu in the primitive constraints editor to select "Select Primitives". The Primitive Finder is displayed. Select the primitive and click "OK". Add the corresponding primitive constraints to the primitive constraints editor.

- Alternatively, select the corresponding primitive in Netlist, drag it to the chip array, and set the location of the corresponding constraints.

SUG101-1.9E 45(150)

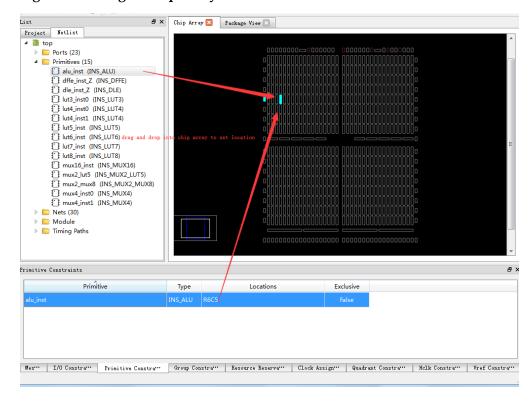

Figure 3-61 Drag to Chip Array and Set Primitive Constraints

#### Set the Primitive Constraints Location by clicking F3

- 1. Select primitive in the Netlist;

- 2. In the chip array, select the grid and press "F3" to set the primitive constraints location, as shown in Figure 3-62.

#### Note!

If no primitive constraints exist, FloorPlanner creates primitive constraints and restricts them to the selected grid location.

SUG101-1.9E 46(150)

Figure 3-62 Set Location of Primitive Constraints by Pressing F3

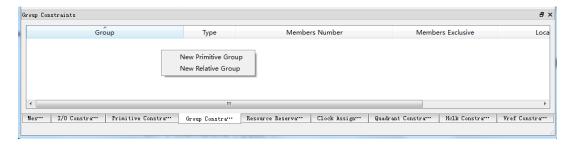

## 3.6.3 Create Group Constraints

As shown in Figure 3-63, create primitive group and relative group by right-clicking in the group constraints.

Figure 3-63 Right-Click Menu of Group Constraints Editor

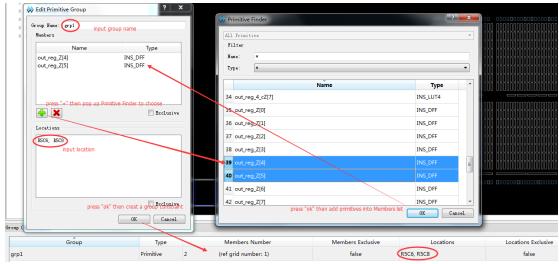

#### **Create Primitive Group Constraints**

- 1. Right-click on the menu and click "New Primitive Group", the Edit Primitive Group menu will open.

- 2. Input Group Name, click "+", and the Primitive Finder window will open.

- 3. Select the primitive, click "Primitive Finder" to select "OK", and add it into Members.

- 4. Input the constrained Location in Locations.

- 5. Select "OK" in the Edit Primitive Group and add Group Constraints in Group Constraints, as shown in Figure 3-64.

SUG101-1.9E 47(150)

- Right-click "Timing Paths > Path\_\*" in Netlist.

- 7. When the menu opens, click "Edit Constraints" to add the group constraint that corresponds to path to group constraints editor.

**Figure 3-64 Create Primitive Group Constraints**

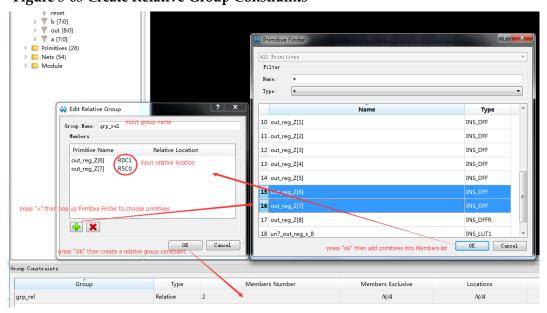

#### **Create Relative Group Constraints**

- Right-click on the menu and click "New Relative Group." The Edit Primitive Group menu will open.

- 2. Input group name, click "+", and the Primitive Finder window will open.

- 3. Select primitives.

- 4. Select "OK" and add it to the Member.

- 5. Add a relative position for each primitive.

- 6. Select "OK" in the Edit Primitive Group, as shown in Figure 3-65.

Figure 3-65 Create Relative Group Constraints

SUG101-1.9E 48(150)

#### 3.6.4 Resource Reservation Creation

#### **Create Resource Reservation**

- 1. Right-click on Resource Reservation and the menu will open.

- 2. Click "Reserve Resources" to add the Resource Reservation constraint to the editor, as shown in Figure 3-66.

Figure 3-66 Create Resource Reservation

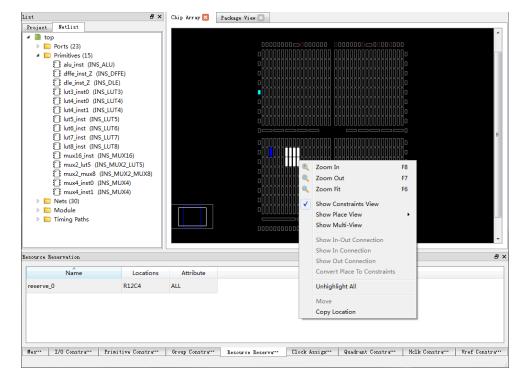

#### **Set Resource Reservation Location**

- 1. Select a constraint from the resource reservation and drag it to the target location in the chip array.

- Modify constraints location, as shown in Figure 3-67.

In chip array, press "Ctrl" and select the area. Right-click "Copy Location" and copy the location to "Resource Reservation > Location" to modify. Then drag to set the resource reservation constraint location.

#### Note!

Or manually input the location by double-clicking "Constraints > Location" to modify the position.

SUG101-1.9E 49(150)

Figure 3-67 Copy Location in Chip Array to Set Resource Reservation Constraint

# 3.6.5 Create Clock Assignment

#### **Create Clock Assignment Constraints**

- 1. Right-click the menu in clock assignment, select "Clock/Control Assignment". The "Clock Assignment" dialog box will open.

- Click "+" and the "Find" dialog box will open. Select Net and click "OK" in Find.

- 3. Set net, select type from the drop-down list and set position and signal. Click "OK" to add the constraint to Clock Assignment, as shown in Figure 3-68.

SUG101-1.9E 50(150)

Find Name: Туре Name Fanout Instance Type 10 b\_c[1] INS\_IBUF 11 b\_c[2] INS\_IBUF 12 b\_c[3] 2 INS\_IBUF Net clk\_c 13  $b_c[4]$  press "+" pop up Find to select net 2 INS IBUF Type BUFG 2 INS IBUF 14 b\_c[5] Signal 15 b\_c[6] INS IBUF 16 b c[7] CLK select signa INS IBUF LOGIC 17 SR 18 out\_c[0] INS\_DFF ress "ok" creat a clock Assigment OK Cancel press "ok" add selected net into clock Assigment OK Cancel

Figure 3-68 Create Clock Assignment Constraints

#### **Modify Clock Assignment Constraints**

In the Clock Assignment window, double-click on the name of the constraints to be modified. The clock assignment dialog box will open.

All properties except net, type, and the signal can all be modified, as shown in Figure 3-69.

Project Netlist ■ top ▶ Ports (23) Primitives (15)

alu\_inst (INS\_ALU) dffe\_inst\_Z (INS\_DFFE) dle\_inst\_Z (INS\_DLE)

lut3\_inst0 (INS\_LUT3) [] lut4\_inst0 (INS\_LUT4) [] lut4\_inst1 (INS\_LUT4) lut5\_inst (INS\_LUT5) Clock Assign lut6\_inst (INS\_LUT6) lut7\_inst (INS\_LUT7) Net CE\_c lut8\_inst (INS\_LUT8) Type BUFG T mux16 inst (INS MUX16) mux2\_lut5 (INS\_MUX2\_LUT5) ✓ CE mux2\_mux8 (INS\_MUX2\_MUX8) mux4\_inst0 (INS\_MUX4) CLK mux4\_inst1 (INS\_MUX4) ▼ LOGIC ▶ Nets (30) SR ▶ Module ▶ ☐ Timing Paths OK Cancel Clock Assignment Net Signal Type CE\_c Mes: I/O Constra: Frimitive Constra: Group Constra: Resource Reserva: Clock Assign: Quadrant Constra: Hclk Constra: Vref Constra:

Figure 3-69 Modify Clock Assignment Constraints

SUG101-1.9E 51(150)

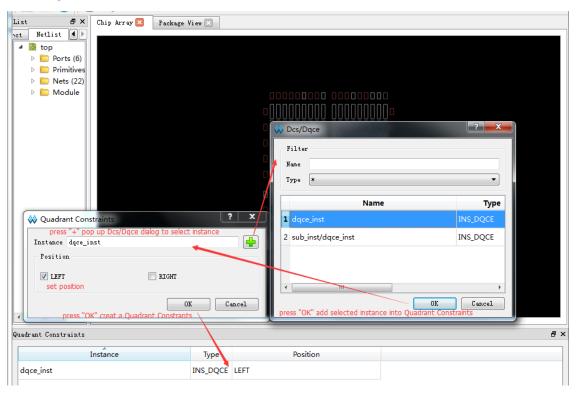

## 3.6.6 Quadrant Constraints Creation

The quadrant constraints only apply to the following instance types:

- Dcs

- Dqce

#### **Create Quadrant Constraints**

- 1. In the Quadrant Constraints editor, right-click the menu, select "Select Dcs/Dqce", and the quadrant constraints dialog box will open.

- Click "+" and the Dcs/Dqce will open. Select "Instance" and click "OK" in Dcs/Dqce to finish setting the instance. Select the constraint location in "Position". Click "OK" to add the constraint to the quadrant constraints view, as shown in Figure 3-70.

Figure 3-70 Create Quadrant Constraints

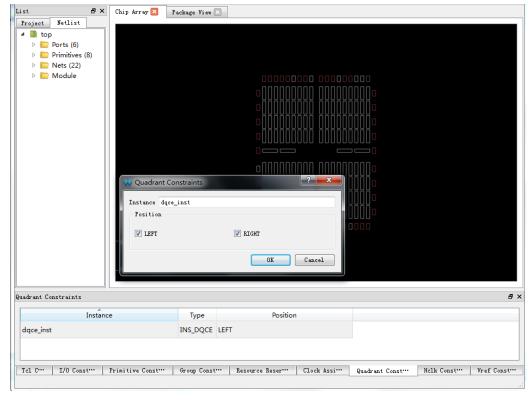

#### **Modify Quadrant Constraints**

Double click on the name of the constraint you would like to modify in the Quadrant Constraints. The Quadrant Constraints window will open. The instance cannot be changed; only the position property can be modified, as shown in Figure 3-71.

SUG101-1.9E 52(150)

Figure 3-71 Modify Quadrant Constraints

#### 3.6.7 Create Hclk Constraints

#### **Create Hclk Constraints**

The steps required to create Hclk Constraints are as follows:

- 1. In the Hclk Constraints window, right-click to open the menu and select "Select Hclk." Hclk Constraints will open.

- 2. Click "+" and Hclk will open.

- 3. Select the instance, and click "OK" in Hclk; set the instance, select the constraint position in position, and click "OK" to add the constraint to Hclk Constraints. As shown in Figure 3-72.

#### Note!

Hclk constraints only constrain the Instance of Clkdiv and dlltype types.

SUG101-1.9E 53(150)

Chip Array 🛛 Package View 🖂 Project Netlist ⊿ 🔤 top Ports (5) Primitives (6) ▶ Module Hclk Filter Туре W Hclk Constraints Name Туре Instance clkdiv\_inst Position 2 sub\_inst/clkdiv\_inst INS\_CLKDIV TOPSIDE[0] TOPSIDE[1] BOTTOMSIDE[0] set position BOTTOMSIDE[1] LEFTSIDE[1] RIGHTSIDE[0] RIGHTSIDE[1] Cancel press "OK" creat a Hclk Constraint OK Cancel Hclk Constraints Instance Туре Position clkdiv\_inst INS\_CLK... BOTTOMSIDE[0]

Figure 3-72 Create Hclk Constraints

#### **Modify Hclk Constraints**

The steps required to modify the Hclk constraints are as follows:

Double-click on the constraint name in Hclk Constraints. The "Hclk Constraints" dialog will open, as shown in Figure 3-73.

#### Note!

The instance cannot be changed. Only the position property can be modified.

SUG101-1.9E 54(150)

Chip Array 🛛 Package View 🖾 Project Netlist top ▶ Ports (5) Primitives (6) ▶ [ Nets (19) D Module Hclk Constraints Instance clkdiv inst Position TOPSIDE[0] TOPSIDE[1] ▼ BOTTOMSIDE[1] ▼ BOTTOMSIDE [0] LEFTSIDE[0] LEFTSIDE[1] RIGHTSIDE[0] RIGHTSIDE[1] OK Cancel Hclk Constraints Position Туре clkdiv\_inst INS\_CLK... BOTTOMSIDE[0]

Figure 3-73 Modify Hclk Constraints

### 3.6.8 Vref Constraints Creation

#### **Create Vref Constraints**

In Vref constraints, right-click the menu and select "Define Vref Driver", add the Vref Constraints into Vref Constraints Editor, as shown in Figure 3-74.

Figure 3-74 Create Vref Constraints

Customize the Vref constraint name. The Vref name cannot be duplicated. If the user attempts to reuse an existing Vref name, a prompt will be displayed, as shown in Figure 3-75.

SUG101-1.9E 55(150)

Figure 3-75 Vref Rename Check

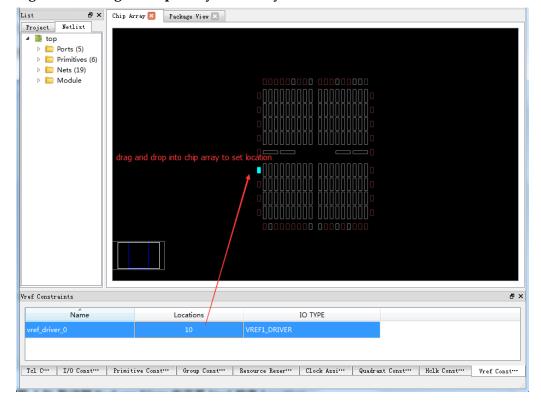

#### **Set Location for Vref Constraints**

Select a constraint in Vref Constraints, drag it into the chip array, and place it in a placeable grid, as shown in Figure 3-76.

#### Note!

- Users can also set the Vref constraints location in Vref Constraints;

- Select a constraint and drag it into the package view. If placeable, put it in an available place, as shown in Figure 3-77.

Figure 3-76 Drag to Chip Array to Modify Location

SUG101-1.9E 56(150)

| Fackage View | Fack

Figure 3-77 Drag to Package View to set Vref Constraint Location

SUG101-1.9E 57(150)

# 4 Timing Constraint

# 4.1 Static Timing Analysis (STA) Overview

Static timing analysis (STA) comprehensively analyzes the circuit netlist, calculates the establishment and maintenance time of the timing elements in the circuit, and determines whether it meets the requirements. The designer provides constraints incentives, and the software completes the computational analysis process automatically. Compared with the traditional analysis method, STA offers a short verification time and high coverage. STA starts with user constraints and analyzes specific timing models. Gowin software verifies the circuit performance, identifies possible timing violations, and generates timing analysis feedback to the user by analyzing data required time, data arrival time, and clock arrival time. Users can further adjust the circuit design as required to improve system working rate and stability.

Before STA, please learn the basic models, terms, and concepts described below.

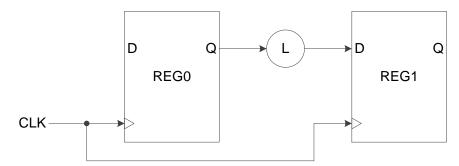

# 4.1.1 Basic Model of Static Timing Analysis

STA is used for a timing analysis model that starts from the timing component and end with the timing component. The basic model is shown in Figure 4-1. The REG0 trigger synchronizes data from D to Q at the clock effective edge. The data triggers REG1, which collects data from the REG0 trigger at the clock effective edge. STA is employed to verify whether REG1 can collect the data from the REG0 trigger correctly.

SUG101-1.9E 58(150)

Figure 4-1 Basic Model of Timing Analysis

The effective clock of the REG0 trigger is launch edge; the REG1 trigger effective clock edge is the latch edge. If we do not take into account the effect of the path constraints, the interval time of the two edges is usually one clock cycle or half a clock cycle.

# 4.1.2 Timing Analysis Terminology

The basic timing units involved in the timing model are as follows:

- Cells: Include LUT, DFF, MUX, DL, DDR, etc;

- Pins: Cells I/O port;

- Ports: I/O ports of the top-level module, usually the external pins of the device:

- Nets: Connection between pin and pin;

- Clocks: The clock set in timing constraint.

# 4.1.3 Timing Analysis Path

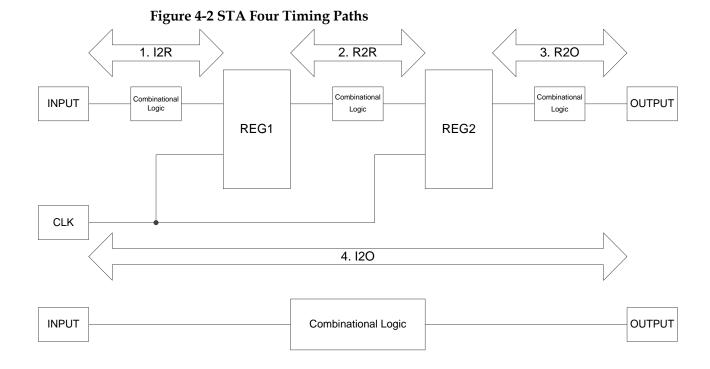

Usually, static timing analysis (STA) analyzes four types of paths and classifies them according to different start and end points, as shown in Figure 4-2:

- I2R: From input port to register;

- R2R: From register to register;

- R2O: From register to output port;

- I2O: From input to output.

SUG101-1.9E 59(150)

STA calculates the data arrival time and data required time through four types of paths.

The data arrival time refers to the time required from the beginning of the timing path to the end point. The data required time refers to the time required for the data to arrive. When calculating the data arrival time, the clock path has a clock skew, which refers to the time difference between the clock and the clock port.

# 4.1.4 Common Timing Checks

#### **Setup Time and Hold Time Check**

- Setup time: The shortest time for data stability before the clock effective edge. If the time is not met, the next level register cannot collect data properly.

- Hold time: The shortest time for data stability after the clock effective edge. If the time is not met, the data will be overwritten by the new data transmitted by the superior register.

#### **Recovery Time and Removal Time Check**

- Recovery time: Before clock effective edge; the shortest time for signal removing asynchronous reset to keep stable. If the time is not satisfied, the register may not enter the normal working state.

- 2. Removal time: After clock effective edge; the shortest time for signal removing asynchronous reset to keep stable. If the time is not satisfied, the register may not enter the normal working state.

SUG101-1.9E 60(150)

#### **MPW Check**

MPW: Min. width of high and low level recognized by internal chip components. The clock will not normally be recognized if the MPW is lower than the width.

STA usually checks the above three types of tests and recommends the layout process to better meet the user's requirements for timing.

# **4.2 Timing Constraints Editor**

#### 4.2.1 Overview

Gowin STA supports multiple timing commands, such as constraints on clock, I/O, path, and clock report command. The user can add timing constraints using GUI provided by the STA.

STA supports default timing analysis. The default clock rising edge is 0 ns, falling edge is 5 ns, and the cycle is 10 ns.

STA provides timing analysis in the cross-clock domain for all clocks by default. If cross-clock domain analysis is not selected, the relationship between clocks can be set via specific timing constraints.

STA provides two timing reports: HTML and text. HTML is the default setting. The default content of the timing report includes setup time check, hold time check, maximum frequency calculation, and minimum clock pulse check. A custom report based on the specific requirements is also supported.

# 4.2.2 Open Editor

#### **Start Timing Constraints Editor**

After creating a project and running Synthesize in Process window in Yun Yuan software, select "Process > Timing Constraints Editor" from the menu to open the timing constraints editor, as shown in Figure 4-3.

#### Note!

The netlist of the project is automatically loaded into the timing constraints editor.

SUG101-1.9E 61(150)

Figure 4-3 Process View

# 4.2.3 Create and Open the Constraints File

The usage of the timing constraints editor is introduced below with a set of examples.

#### **Create Constraints File**

The steps required to create a constraint file are as follows:

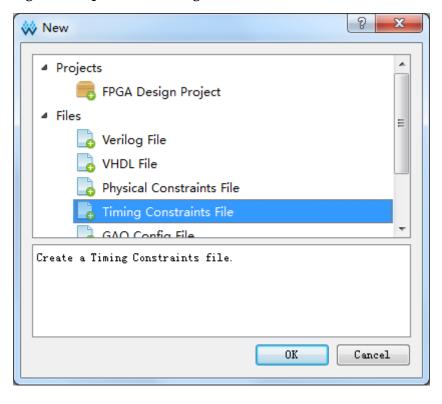

- 1. Click "File > New", the "Open File" dialogue will open.

- Select "Timing Constraints File", as shown in Figure 4-4.

#### Note!

You can also open a new timing constraints file by taking the following steps:

- Click the "New" icon on the toolbar.

- Use the "Ctrl+N" shortcut.

SUG101-1.9E 62(150)

Figure 4-4 Open New Timing Constraints File

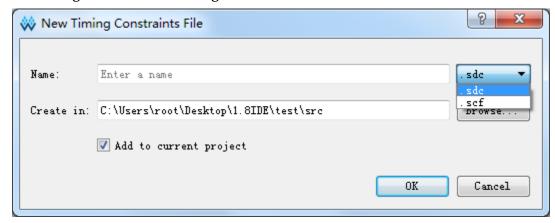

Click "OK", and a new timing constraints file will open, as shown in Figure 4-5.

Figure 4-5 Create Timing Constraint File

- Name: Input the name of the new sequential constraint file. The .sdc and .scf suffixes are supported.

- Create in: Select the constraint file location by clicking on the "Browse" button. New constraint files are stored in the src folder of the project by default.

- Add to current project: If this is checked, the constraints file will be added to the project automatically.

SUG101-1.9E 63(150)

#### **Open Constraint File**

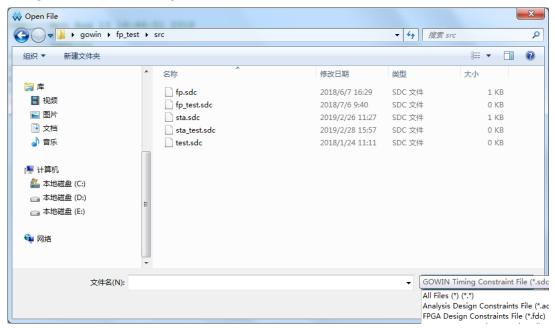

The steps required to open a constraint file are as follows:

- Click "File > Open".

- 2. Open the "Open File" dialogue box, as shown in Figure 4-6.

#### Note!

You can also open a constraints file by taking the following steps:

- Click the "Open" icon on the toolbar.

- Use the "Ctrl+O" shortcut.

Figure 4-6 Open Timing Constraint File

Select the location in which the timing constraint file is stored, and select the file you wish to open.

#### 4.2.4 Editor

After creating or opening the constraints file, the editor interface will be displayed, as shown in Figure 4-7.

SUG101-1.9E 64(150)

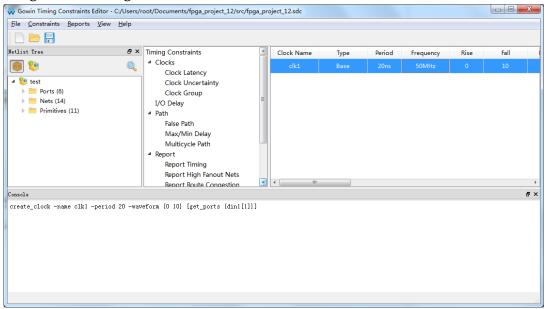

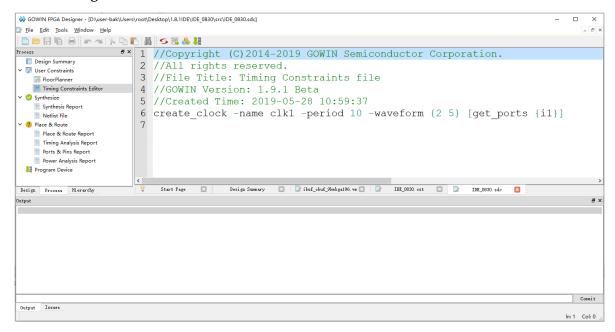

Figure 4-7 Timing Constraint Editor

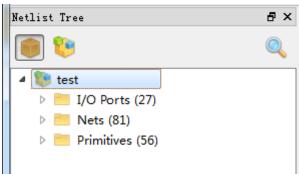

The Netlist Tree view is as shown in Figure 4-8.

Figure 4-8 Netlist Tree View

The Netlist Tree window contains various elements of the current network table file, including top module, I/O ports, nets, and primitives.

- ": check flatten.

- "": check hierarchy.

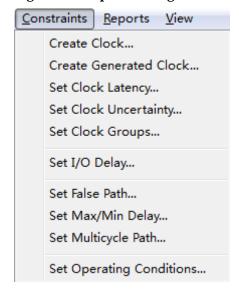

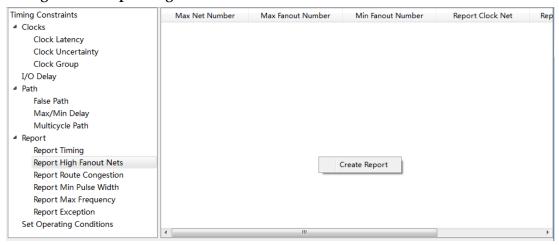

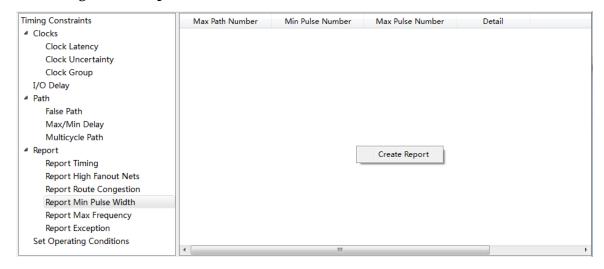

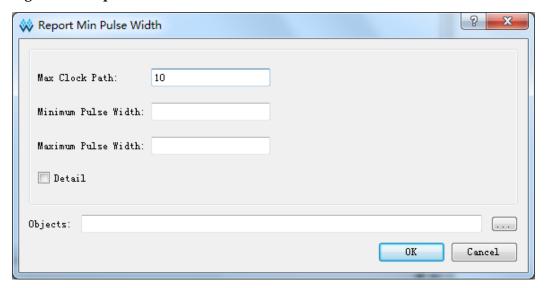

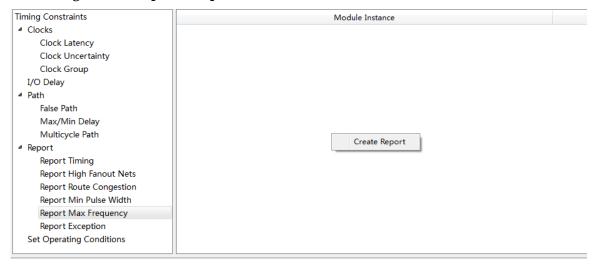

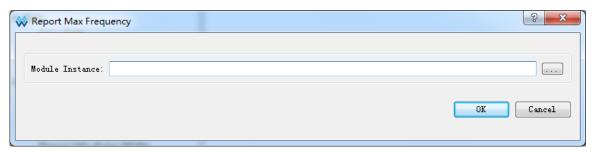

The middle and right area of the main interface is the constraint editing area, as shown in Figure 4-9. The left list is the timing constraint list, and the right side is the editing list. Click on a constraint type from the type list, and the constraint editing list will be displayed in the edit area list.

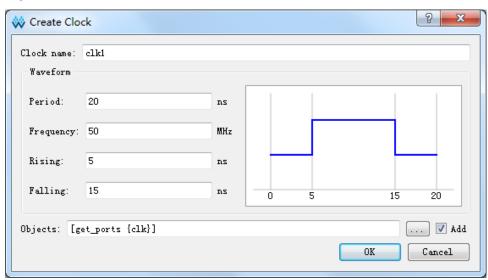

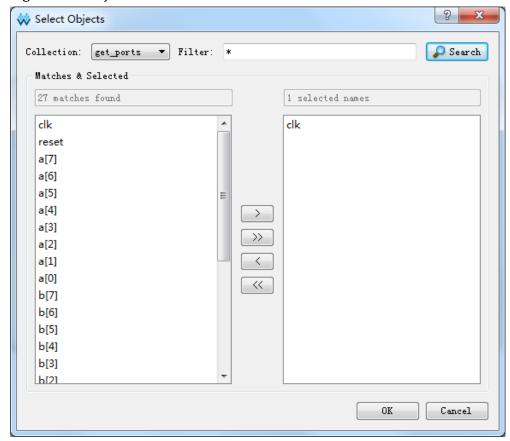

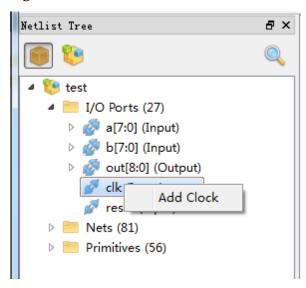

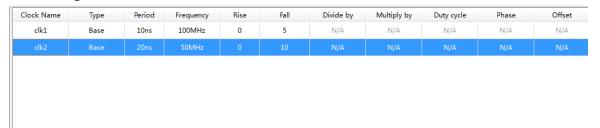

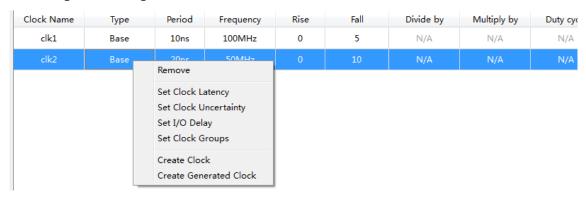

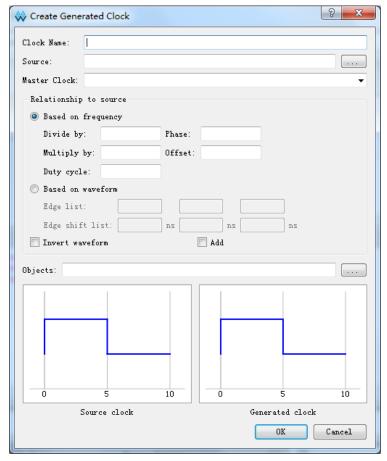

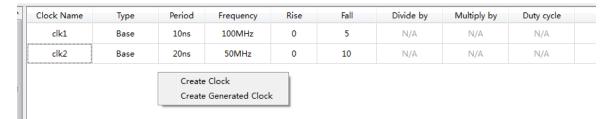

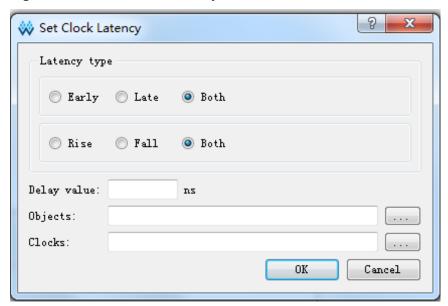

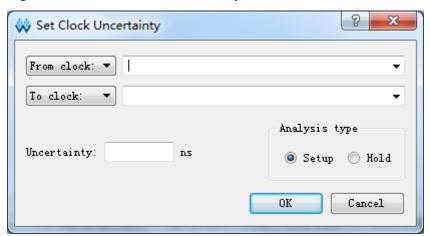

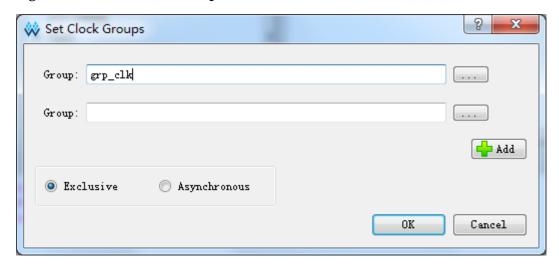

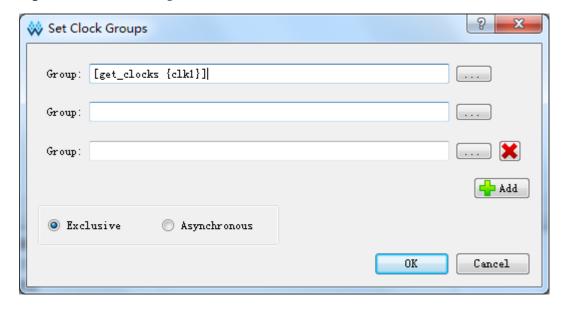

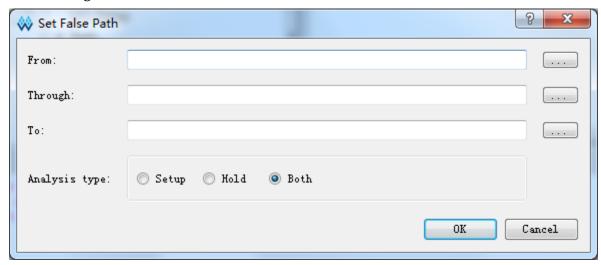

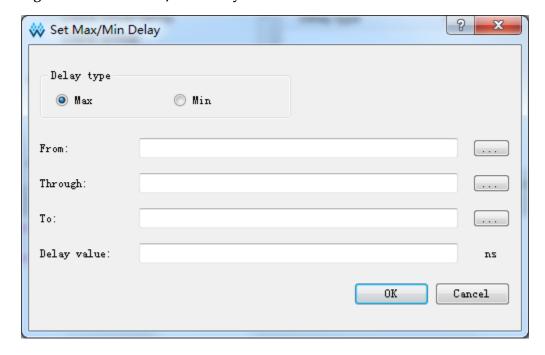

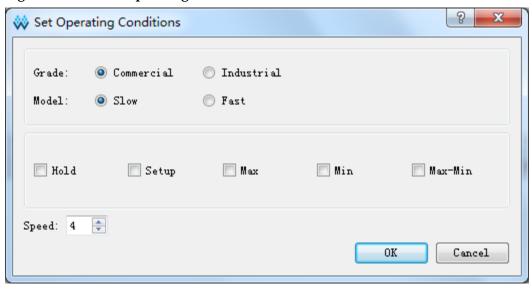

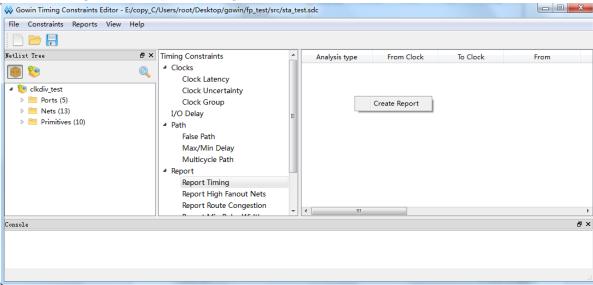

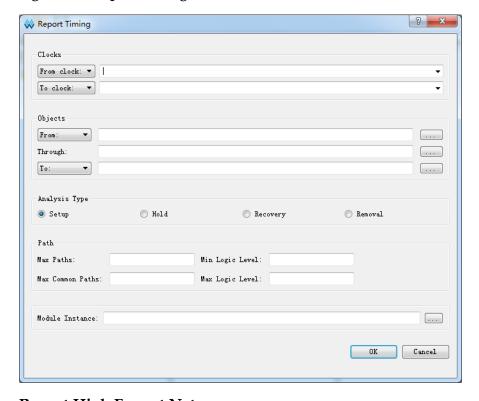

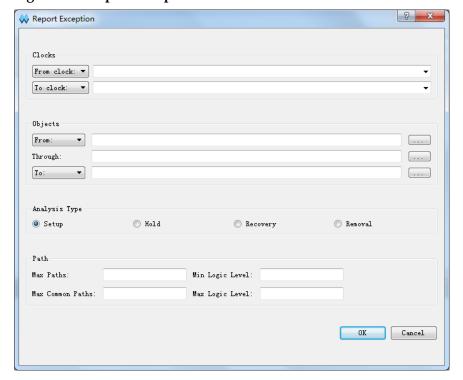

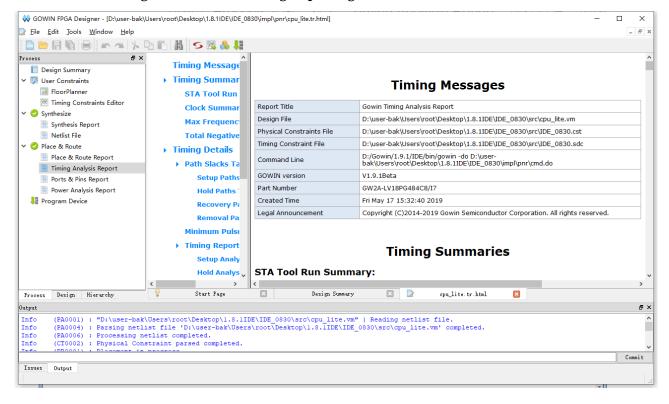

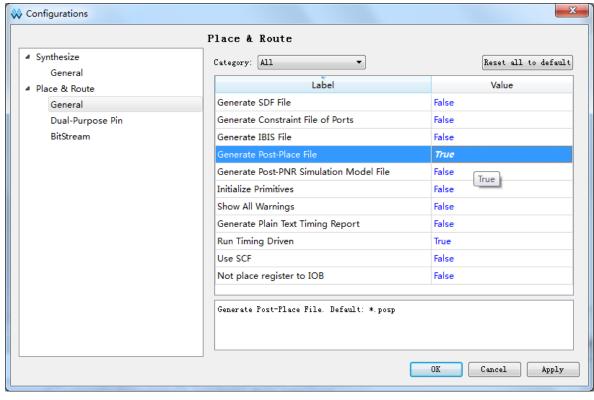

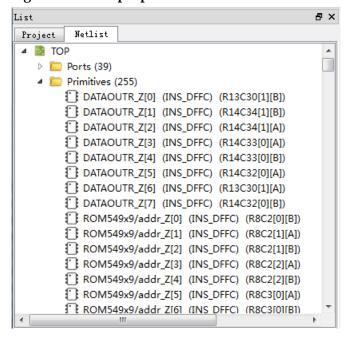

SUG101-1.9E 65(150)