# Gowin IP 核产生工具 用户指南

SUG284-1.9, 2019-11-28

#### 版权所有<sup>©</sup>2019 广东高云半导体科技股份有限公司

未经本公司书面许可,任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部,并不得以任何形式传播。

#### 免责声明

本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止发言或其它方式授予任何知识产权许可。除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。高云半导体不承诺对这些文档进行适时的更新。

### 版本信息

| 日期         | 版本  | 说明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2017/03/07 | 1.0 | 初始版本。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 2018/01/30 | 1.2 | <ul> <li>支持 GW1NR-4、GW1N-6、GW1N-9、GW1NR-9;</li> <li>更新了 BSRAM 部分;</li> <li>更新了 DSP 部分;</li> <li>更新了 PLL;</li> <li>更新了 User Flash。</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 2018/08/25 | 1.3 | ● 支持 GW1N-2B、GW1N-4B、GW1N-6ES、GW1N-9ES、GW1NR-4B、GW1NR-9ES、GW1NS-2、GW1NS-2C; ● 新增 IP DDR3、DDR3 PHY; ● 更新 PLL; ● 更新 OSC; ● 更新 User Flash; ● 优化界面显示; ● 新增 IP CORDIC、Complex Multiplier、DIVIDER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 2018/10/26 | 1.4 | ● 支持 GW1NZ-1、GW1NSR-2C;<br>● 新增 I3C、SPMI 硬核。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 2018/11/15 | 1.5 | ● 支持 GW1NSR-2;<br>● 删除 GW1N-6ES、GW1NS-9ES、GW1NR-9ES。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 2019/02/12 | 1.6 | ● 新增 IP RiscV N25、CAN;<br>● 更新 PSRAM、DDRx、MIPI。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 2019/02/25 | 1.7 | <ul> <li>新增 IP Basic FIR Filter、FD Adaptive Filter、Integer Multiply Divider、NLMS Adaptive Filter、XCORR、Triple Speed Ethernet MAC;</li> <li>优化界面显示(删除界面 Add to Current Project 选项)。</li> <li>支持 GW1N-1S</li> <li>新增 IP PSRAM Memory Interface 2CH、Advanced FIR Filter、Gowin_EMPU_M1、HyperRAM Memory Interface</li> <li>新增 Hard module 部分 Shadow Memory,包括RAM16S、RAM16SDP、ROM16</li> <li>更新 IP MIPI、DDR、DDR2、DDR3、GOWIN_EMPU</li> <li>支持 GW1NS-4、GW1NRF-4B、GW1NSE-2C、GW1NSER-4C、GW1NSR-4、GW1NSR-4C;</li> <li>支持综合工具选择 Synplify Pro 或 GowinSynthesis;</li> <li>Soft IP Core 部分调整分类;</li> <li>Hard Module 部分新增 BandGap、rPLL、PLLVR、DPB、DPBX9、SDPB、SDPBX9、rSDP、rSDPX9、rROM、rROMX9、pROM、pROMX9;</li> <li>对建议优先使用的原语添加引导备注。</li> </ul> |  |

| 2019/05/17 | 1.8 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 2019/11/28 | 1.9 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

# 目录

| 目 | 录                | i   |

|---|------------------|-----|

| 图 | 目录               | iii |

| 表 | 音录               | ix  |

|   | 关于本手册            |     |

| • |                  |     |

|   | 1.1 手册内容         |     |

|   | 1.2 适用产品         | 1   |

|   | 1.3 相关文档         | 1   |

|   | 1.4 术语、缩略语       | 2   |

|   | 1.5 技术支持与反馈      | 2   |

| 2 | 简介               | 3   |

|   | 使用               |     |

| J |                  |     |

|   | 3.1 Block Memory | 8   |

|   | 3.1.1 SP         | 8   |

|   | 3.1.2 DP         | 13  |

|   | 3.1.3 DPB        | 19  |

|   | 3.1.4 SDP        | 25  |

|   | 3.1.5 SDPB       | 30  |

|   | 3.1.6 rSDP       | 36  |

|   | 3.1.7 ROM        | 42  |

|   | 3.1.8 pROM       | 47  |

|   | 3.1.9 rROM       | 52  |

|   | 3.2 DSP          | 57  |

|   | 3.2.1 ALU54      | 57  |

|   | 3.2.2 MULT       | 64  |

|   | 3.2.3 MULTADDALU | 69  |

|   | 3.2.4 MULTALU    | 74  |

|   | 3.2.5 PADD       | 80  |

|   | 3.3 CLOCK        | 86  |

|   | 3.3.1 PLL        | 86  |

| 3.3.2 rPLL        | 97  |

|-------------------|-----|

| 3.3.3 PLLVR       | 100 |

| 3.3.4 DLL         | 107 |

| 3.3.5 OSC         | 112 |

| 3.4 User Flash    | 116 |

| 3.5 I3C           | 121 |

| 3.6 SPMI          | 129 |

| 3.7 Shadow Memory | 136 |

| 3.7.1 RAM16S      |     |

| 3.7.2 RAM16SDP    | 142 |

| 3.7.3 ROM16       | 147 |

| 3.8 BandGap       | 152 |

# 图目录

| 图 3-1 IP Core Generator 界面         | 4    |

|------------------------------------|------|

| 图 3-2 Select Device 窗口             | 6    |

| 图 3-3 IP Customization 窗口          | 7    |

| 图 3-4 ipc 文件的 IP Customization 窗口  | 7    |

| 图 3-5 SP 的信息概要                     | 8    |

| 图 3-6 SP 的 IP Customization 窗口结构   | 9    |

| 图 3-7 Language 下拉列表框               | 9    |

| 图 3-8 Module 名与原语名称一致时报 Error      | 10   |

| 图 3-9 Help 信息                      | . 11 |

| 图 3-10 配置的 IP Customization        | .12  |

| 图 3-11 例化 SP 设计文件                  | . 12 |

| 图 3-12 用户例化该 IP 设计文件的模板文件          | . 13 |

| 图 3-13 SP IP Customization 设置      | . 13 |

| 图 3-14 DP 的信息概要                    | .14  |

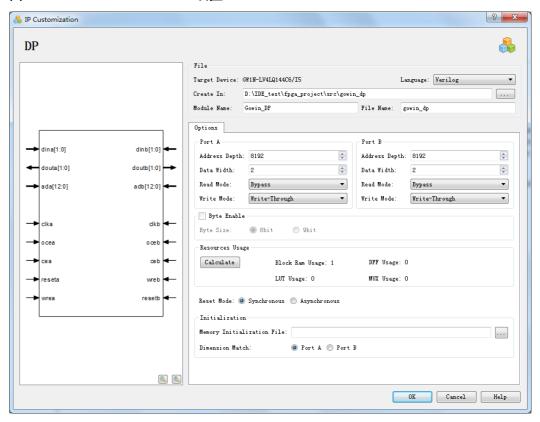

| 图 3-15 DP 的 IP Customization 窗口结构  | 15   |

| 图 3-16 DP 配置 Error 提示              | 16   |

| 图 3-17 Help 信息                     | 16   |

| 图 3-18 配置的 IP Customization        | . 17 |

| 图 3-19 例化 DP 设计文件                  | . 18 |

| 图 3-20 用户例化该 IP 设计文件的模板文件          | . 18 |

| 图 3-21 DP IP Customization 设置      | . 19 |

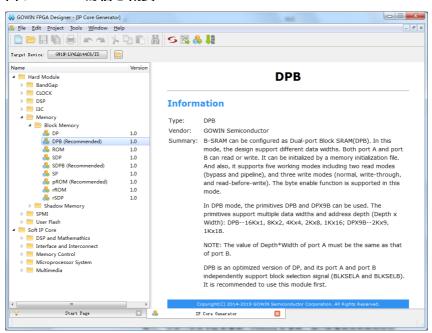

| 图 3-22 DPB 的信息概要                   | 20   |

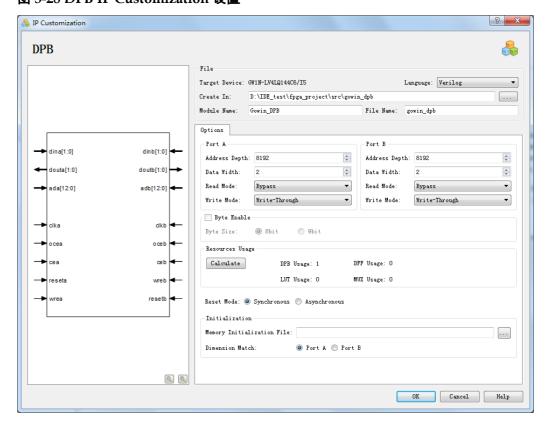

| 图 3-23 DPB 的 IP Customization 窗口结构 | 20   |

| 图 3-24 Help 信息                     | 21   |

| 图 3-25 配置的 IP Customization        | 22   |

| 图 3-26 例化 DPB 设计文件                 | 23   |

| 图 3-27 用户例化该 IP 设计文件的模板文件          | 24   |

| 图 3-28 DPB IP Customization 设置     | 24   |

| 图 3-29 SDP 信息概要                    | . 25 |

SUG284-1.9

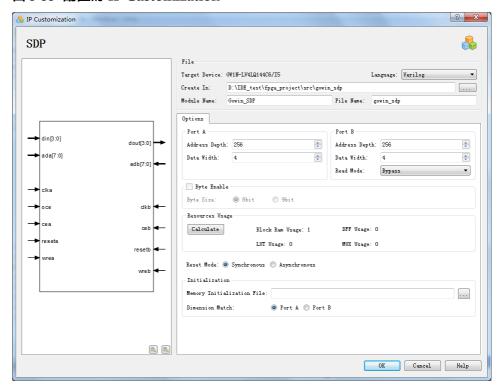

| 图 3-30 SDP 的 IP Customization 窗口结构  | 26 |

|-------------------------------------|----|

| 图 3-31 SDP 配置 Error 信息              | 27 |

| 图 3-32 Help 信息                      | 27 |

| 图 3-33 配置的 IP Customization         | 28 |

| 图 3-34 例化 SDP 设计文件                  | 29 |

| 图 3-35 用户例化该 IP 设计文件的模板文件           | 29 |

| 图 3-36 SDP 的 IP Customization 设置    | 30 |

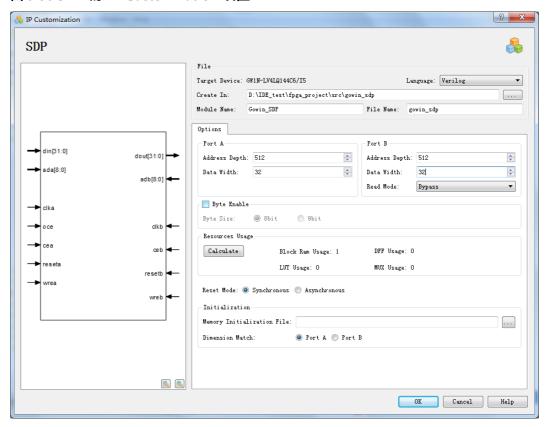

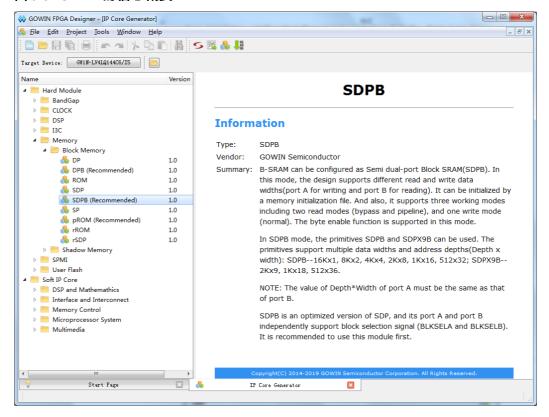

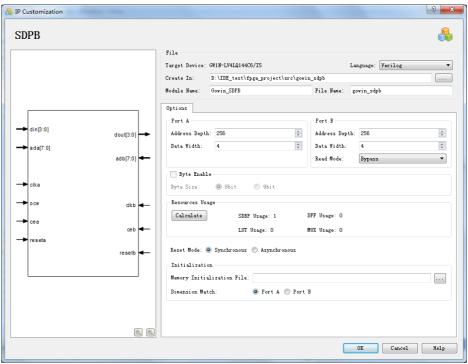

| 图 3-37 SDPB 的信息概要                   | 31 |

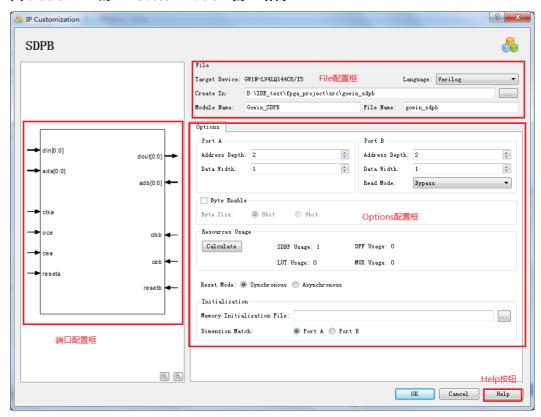

| 图 3-38 SDPB 的 IP Customization 窗口结构 | 32 |

| 图 3-39 Help 信息                      | 33 |

| 图 3-40 配置的 IP Customization         | 34 |

| 图 3-41 例化 SDPB 设计文件                 | 35 |

| 图 3-42 用户例化该 IP 设计文件的模板文件           | 35 |

| 图 3-43 SDPB 的 IP Customization 设置   | 36 |

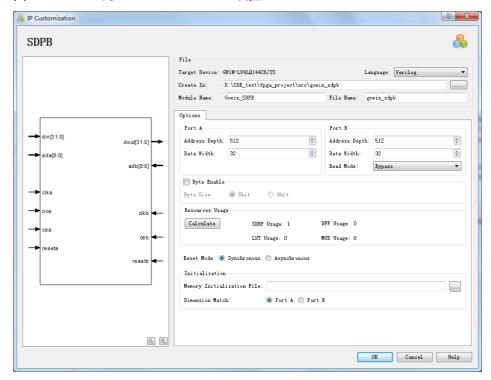

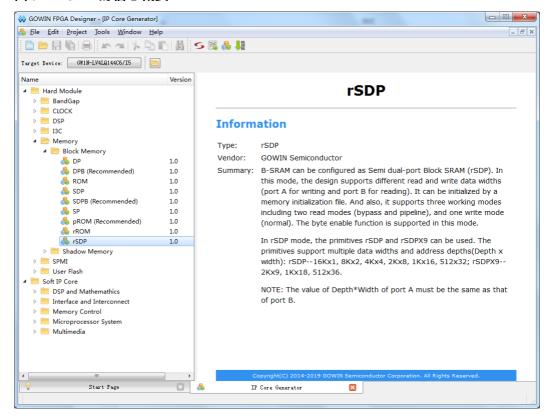

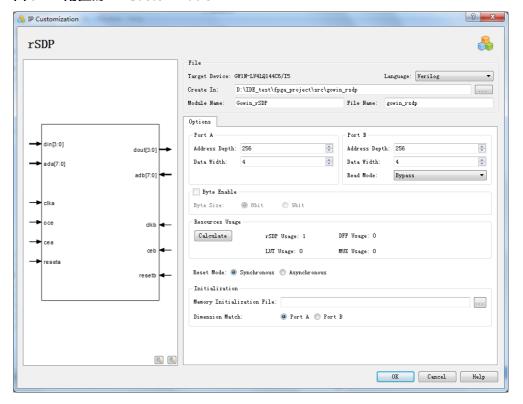

| 图 3-44 rSDP 的信息概要                   | 37 |

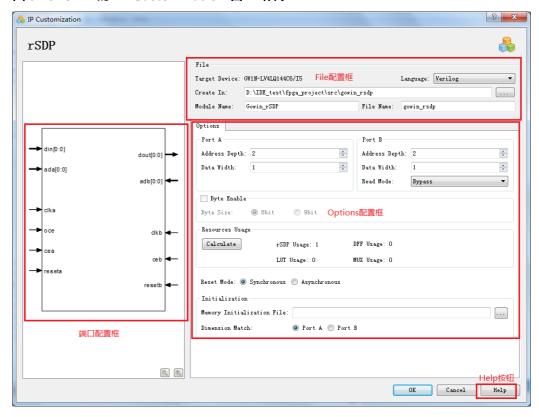

| 图 3-45 rSDP 的 IP Customization 窗口结构 | 38 |

| 图 3-46 Help 信息                      | 39 |

| 图 3-47 配置的 IP Customization         | 40 |

| 图 3-48 例化 rSDP 设计文件                 | 41 |

| 图 3-49 用户例化该 IP 设计文件的模板文件           | 41 |

| 图 3-50 rSDP 的 IP Customization 设置   | 42 |

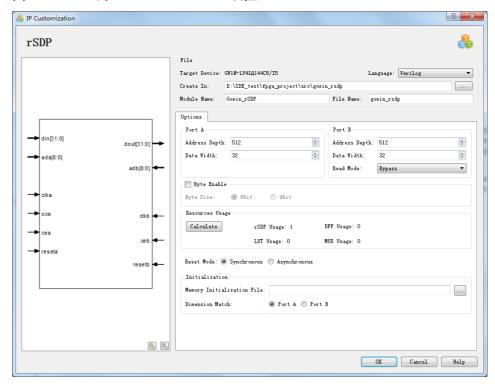

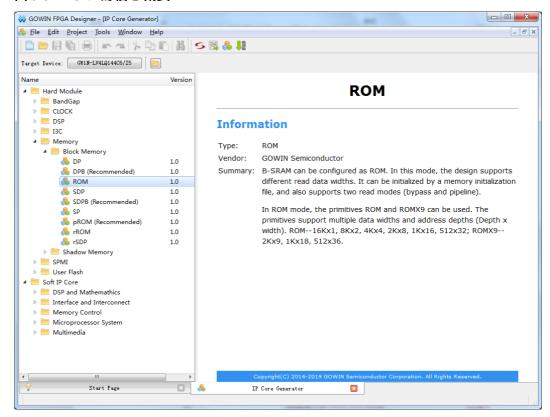

| 图 3-51 ROM 的信息概要                    | 43 |

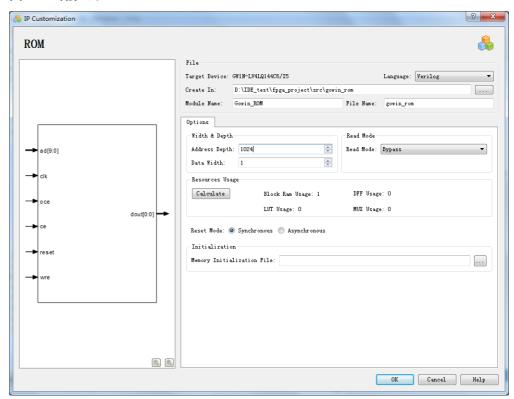

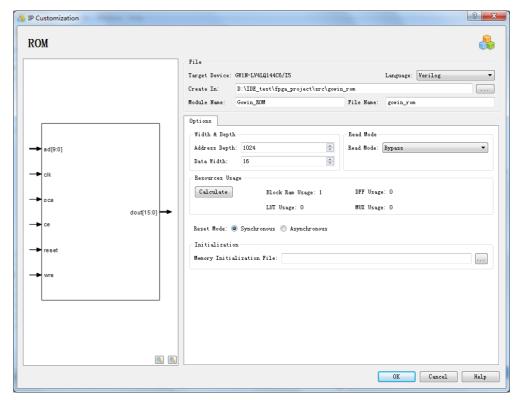

| 图 3-52 ROM 的 IP Customization 窗口结构  | 43 |

| 图 3-53 Help 信息                      | 44 |

| 图 3-54 配置的 IP Customization         | 45 |

| 图 3-55 例化 ROM 设计文件                  | 46 |

| 图 3-56 用户例化 IP 设计文件的模板文件            | 46 |

| 图 3-57 ROM 的 IP Customization 设置    |    |

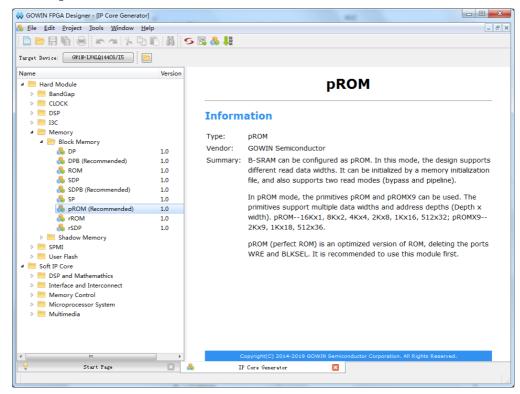

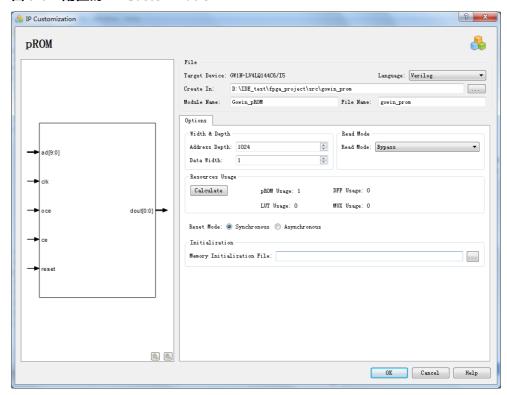

| 图 3-58 pROM 的信息概要                   | 48 |

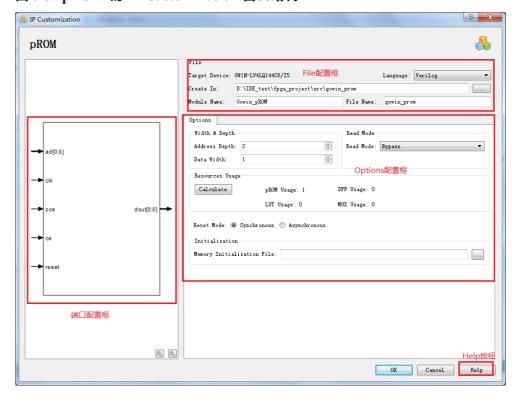

| 图 3-59 pROM 的 IP Customization 窗口结构 | 48 |

| 图 3-60 Help 信息                      | 49 |

| 图 3-61 配置的 IP Customization         | 50 |

| 图 3-62 例化 pROM 设计文件                 | 51 |

| 图 3-63 用户例化 IP 设计文件的模板文件            | 51 |

| 图 3-64 pROM 的 IP Customization 设置   |    |

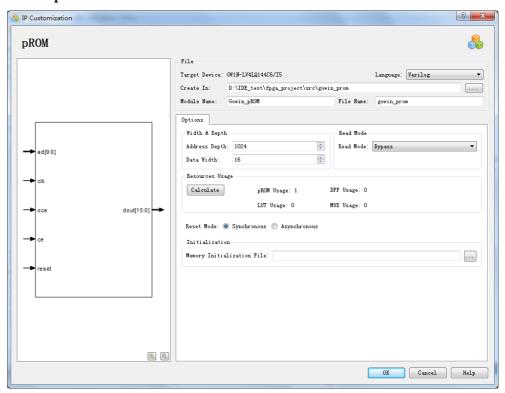

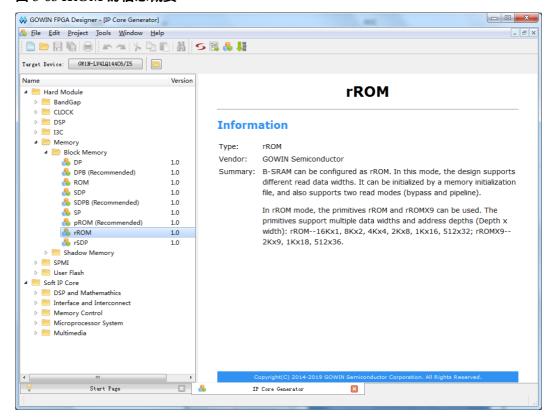

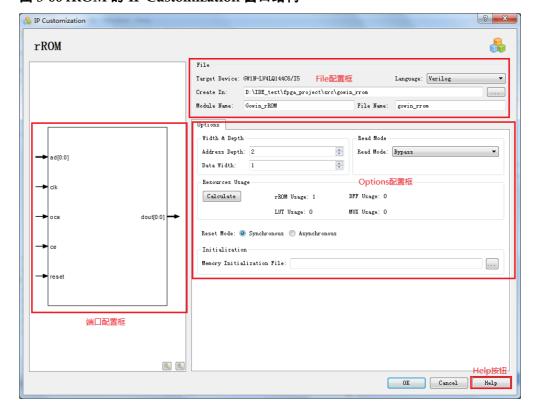

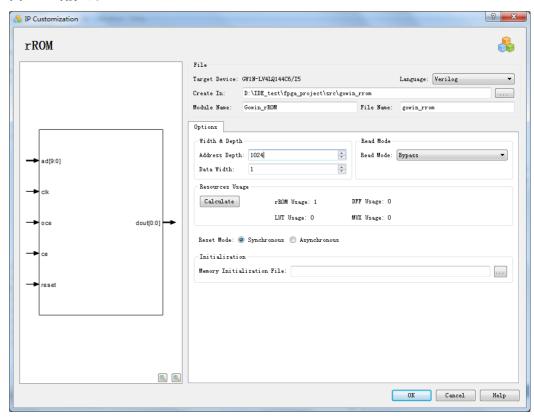

| 图 3-65 rROM 的信息概要                   | 53 |

| 图 3-66 rROM 的 IP Customization 窗口结构 | 53 |

| 图 3-67 Help 信息                            | 54 |

|-------------------------------------------|----|

| 图 3-68 配置的 IP Customization               | 55 |

| 图 3-69 例化 rROM 设计文件                       | 56 |

| 图 3-70 用户例化 IP 设计文件的模板文件                  | 56 |

| 图 3-71 rROM 的 IP Customization 设置         | 57 |

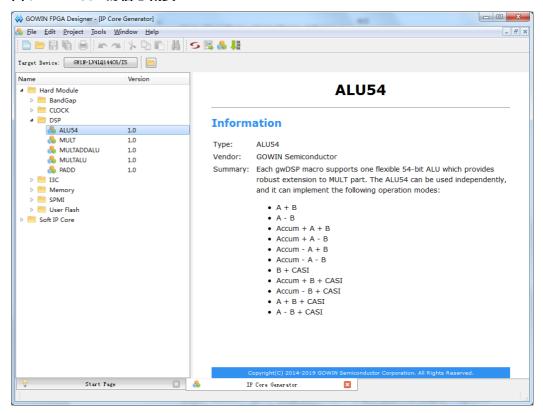

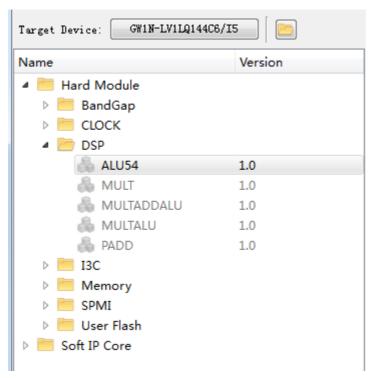

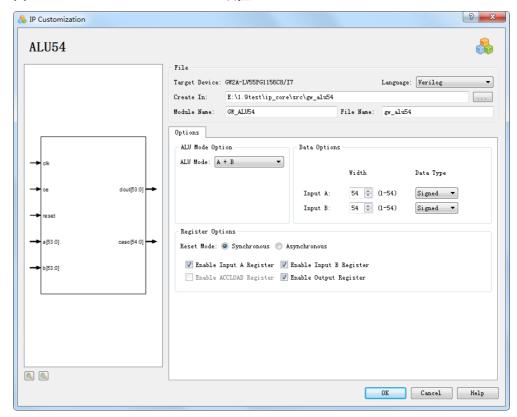

| 图 3-72 ALU54 的信息概要                        | 58 |

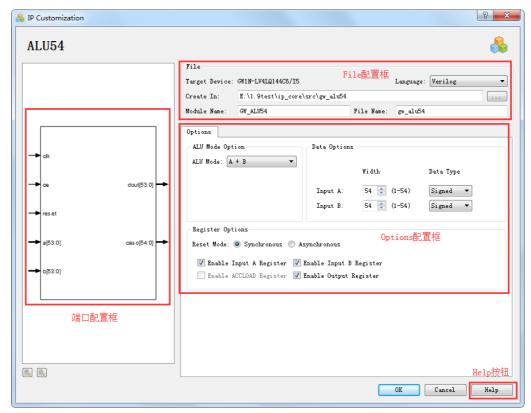

| 图 3-73 ALU54 的 IP Customization 窗口结构      | 59 |

| 图 3-74 DSP 部分界面变灰                         | 60 |

| 图 3-75 Help 信息                            | 61 |

| 图 3-76 配置的 IP Customization               | 62 |

| 图 3-77 例化 ALU54 设计文件                      | 63 |

| 图 3-78 用户例化该 IP 设计文件的模板文件                 | 63 |

| 图 3-79 ALU54 IP Customization 设置          | 64 |

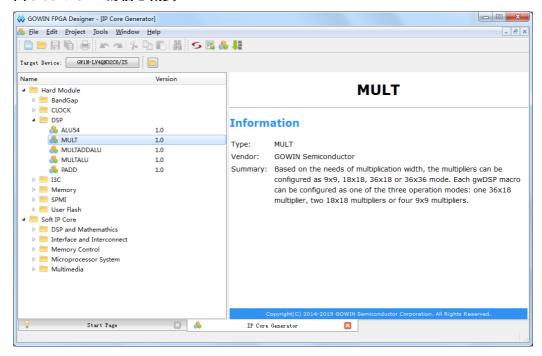

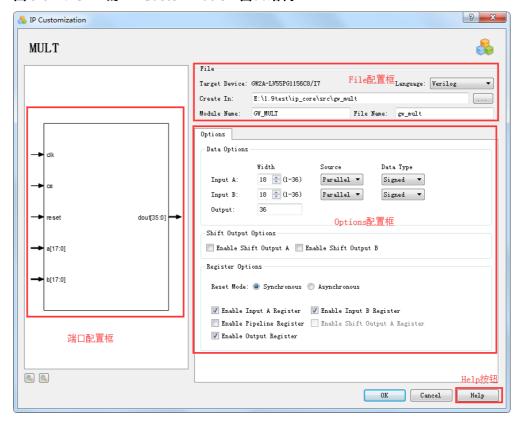

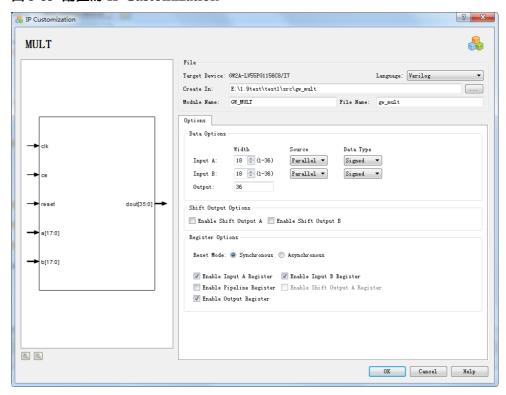

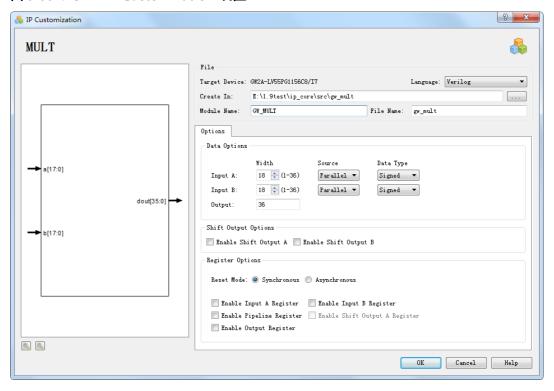

| 图 3-80 MULT 的信息概要                         | 65 |

| 图 3-81 MULT 的 IP Customization 窗口结构       | 65 |

| 图 3-82 Help 信息                            | 66 |

| 图 3-83 配置的 IP Customization               | 67 |

| 图 3-84 例化 MULT 设计文件                       | 68 |

| 图 3-85 用户例化该 IP 设计文件的模板文件                 | 68 |

| 图 3-86 MULT IP Customization 设置           | 69 |

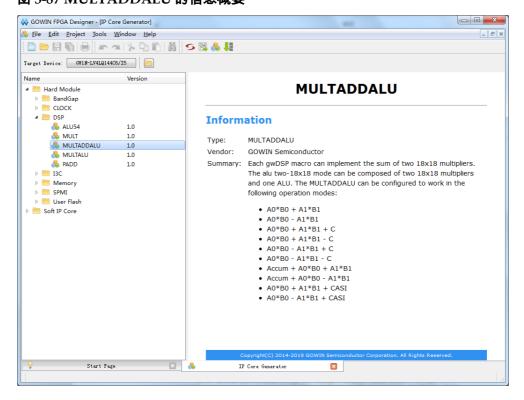

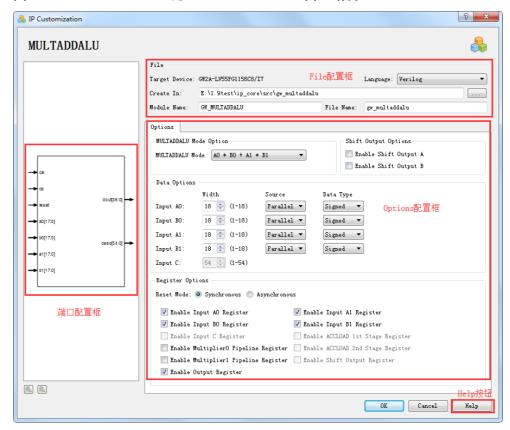

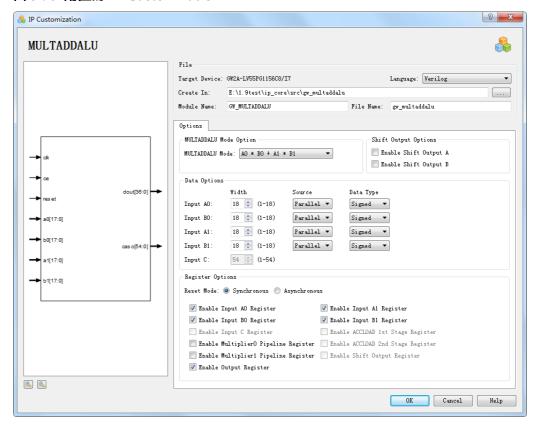

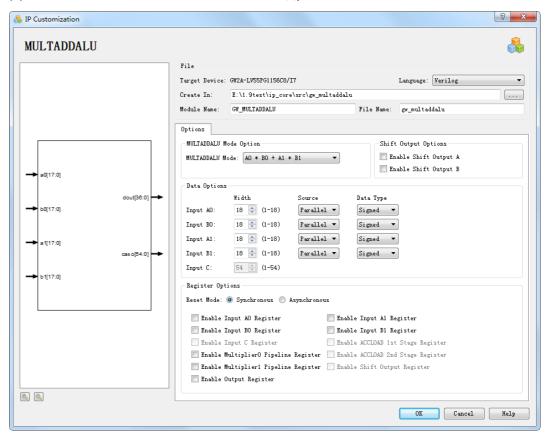

| 图 3-87 MULTADDALU 的信息概要                   | 69 |

| 图 3-88 MULTADDALU 的 IP Customization 窗口结构 |    |

| 图 3-89 Help 信息                            | 71 |

| 图 3-90 配置的 IP Customization               | 72 |

| 图 3-91 例化 MULTADDALU 设计文件                 | 73 |

| 图 3-92 用户例化该 IP 设计文件的模板文件                 | 73 |

| 图 3-93 MULTADDALU IP Customization 设置     | 74 |

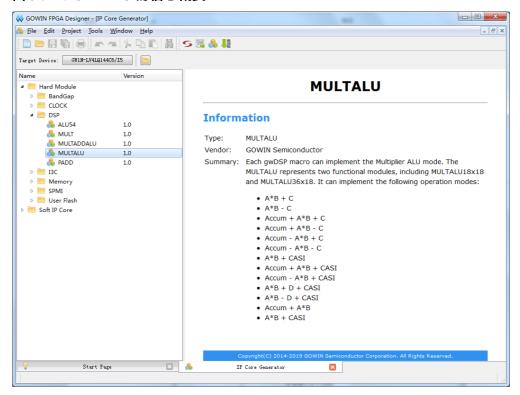

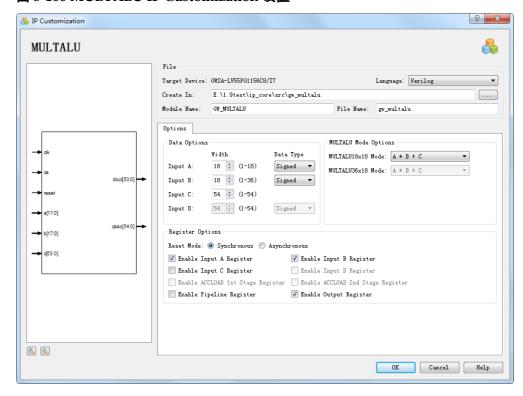

| 图 3-94 MULTALU 的信息概要                      |    |

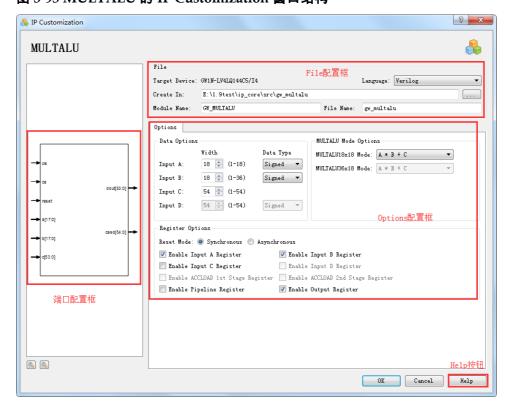

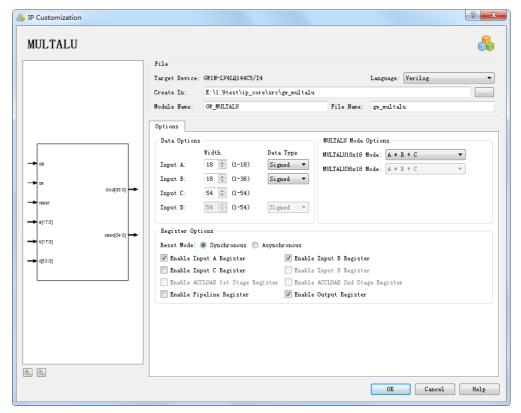

| 图 3-95 MULTALU 的 IP Customization 窗口结构    |    |

| 图 3-96 Help 信息                            | 77 |

| 图 3-97 配置的 IP Customization               | 78 |

| 图 3-98 例化 MULTALU 设计文件                    | 79 |

| 图 3-99 用户例化该 IP 设计文件的模板文件                 | 79 |

| 图 3-100 MULTALU IP Customization 设置       |    |

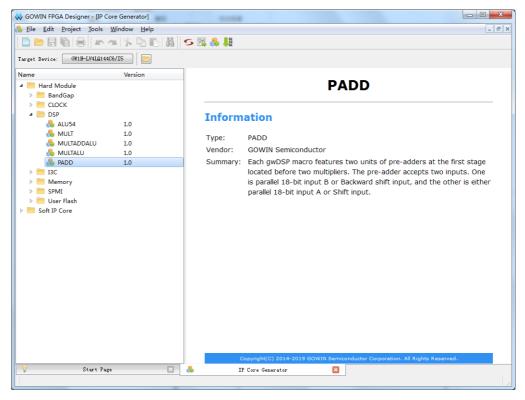

| 图 3-101 PADD 信息概要                         |    |

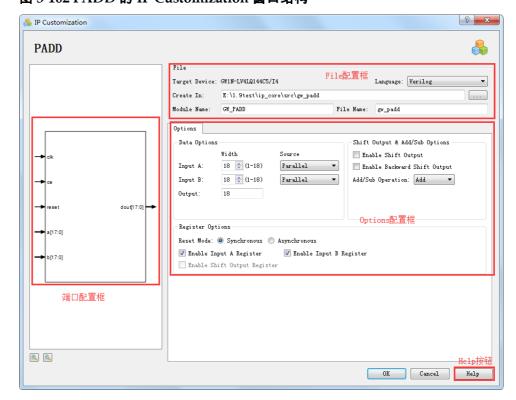

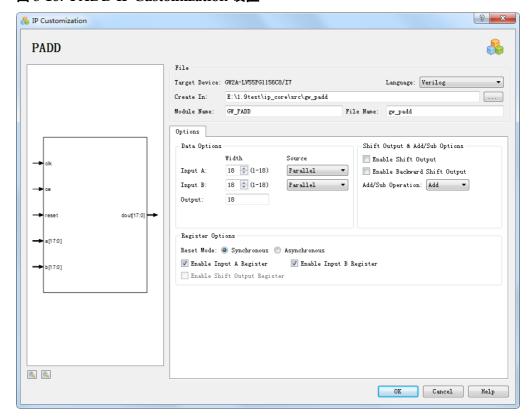

| 图 3-102 PADD 的 IP Customization 窗口结构      |    |

| 图 3-103 Help 信息                           | 83 |

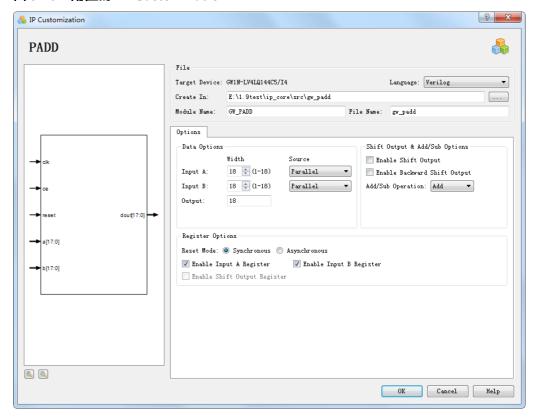

| 图 3-104 配置的 IP Customization                      | 84  |

|---------------------------------------------------|-----|

| 图 3-105 例化 PADD 设计文件                              | 85  |

| 图 3-106 用户例化该 IP 设计文件的模板文件                        | 85  |

| 图 3-107 PADD IP Customization 设置                  | 86  |

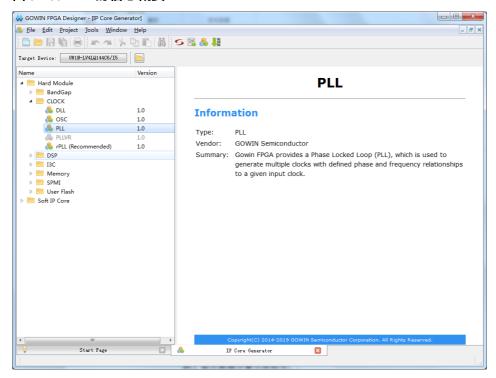

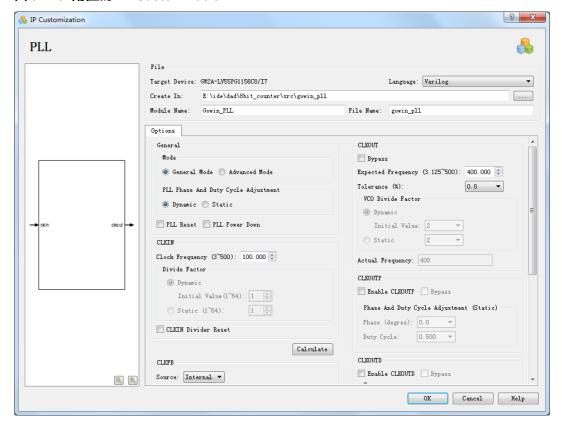

| 图 3-108 PLL 的信息概要                                 | 87  |

| 图 3-109 PLL 的 IP Customization 窗口结构               | 88  |

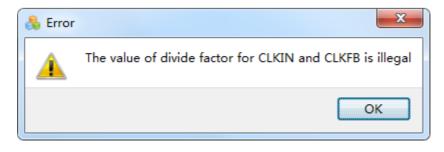

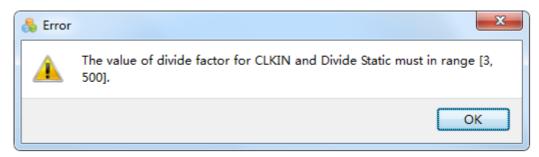

| 图 3-110 CLKIN/CLKFB Divide Factor 配置不合理的 error 窗口 | 90  |

| 图 3-111 CLKIN Divide Factor 配置不合理的 error 窗口       | 91  |

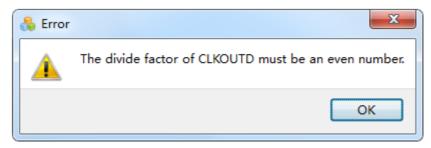

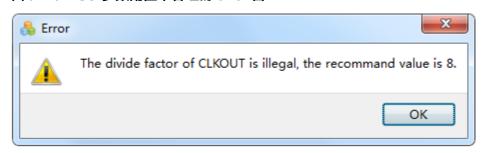

| 图 3-112 CLKOUTD 分频参数配置不合理的 Error 窗口               | 91  |

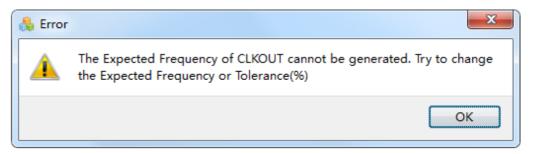

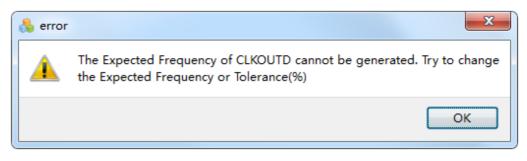

| 图 3-113 CLKOUT 期望频率与计算频率不等的 Error 窗口              | 91  |

| 图 3-114 CLKOUTD 期望频率与计算频率不等的 Error 窗口             | 91  |

| 图 3-115 VCO 参数配置不合理的 error 窗口                     | 92  |

| 图 3-116 参数配置合理的 info 窗口                           | 92  |

| 图 3-117 Help 信息                                   | 93  |

| 图 3-118 配置的 IP Customization                      | 95  |

| 图 3-119 例化 PLL 设计文件                               | 96  |

| 图 3-120 用户例化该 IP 设计文件的模板文件                        | 97  |

| 图 3-121 PLL IP Customization 设置                   | 97  |

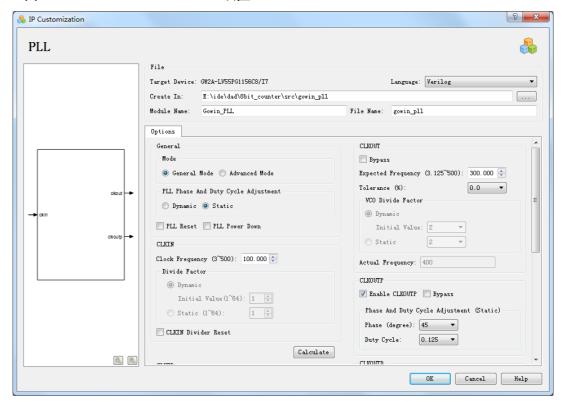

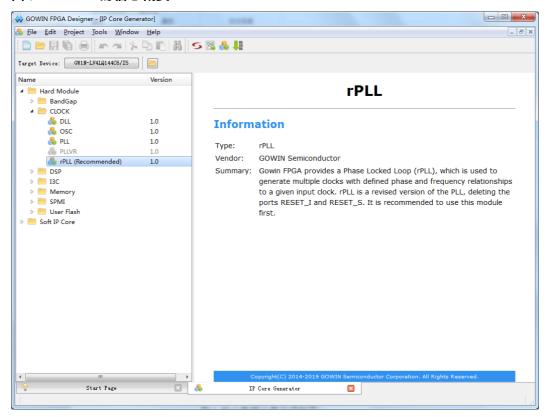

| 图 3-122 rPLL 的信息概要                                | 98  |

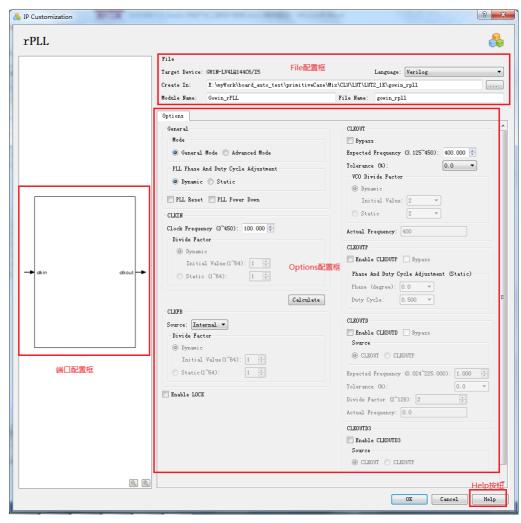

| 图 3-123 rPLL 的 IP Customization 窗口结构              | 99  |

| 图 3-124 Help 信息                                   | 100 |

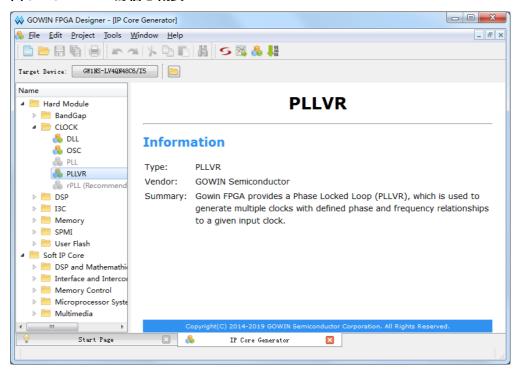

| 图 3-125 PLLVR 的信息概要                               | 101 |

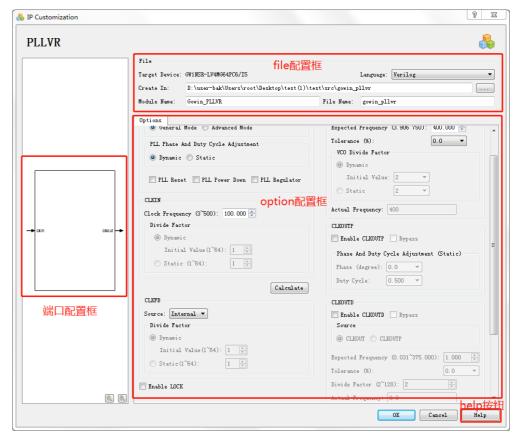

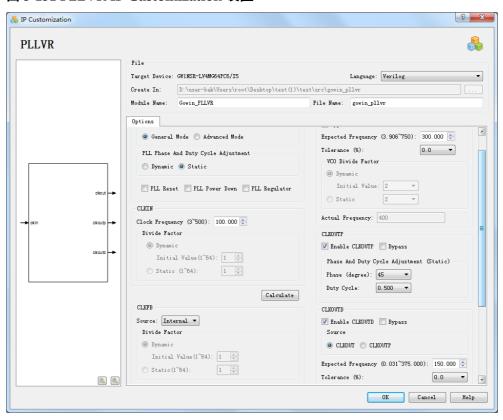

| 图 3-126 PLLVR 的 IP Customization 窗口结构             | 102 |

| 图 3-127 Help 信息                                   | 103 |

| 图 3-128 配置的 IP Customization                      | 105 |

| 图 3-129 例化 PLLVR 设计文件                             | 106 |

| 图 3-130 用户例化该 IP 设计文件的模板文件                        | 107 |

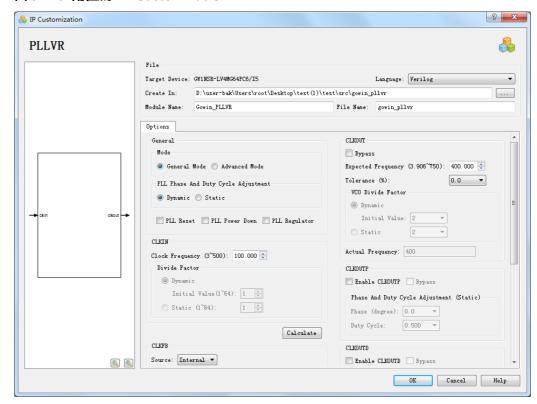

| 图 3-131 PLLVR IP Customization 设置                 | 107 |

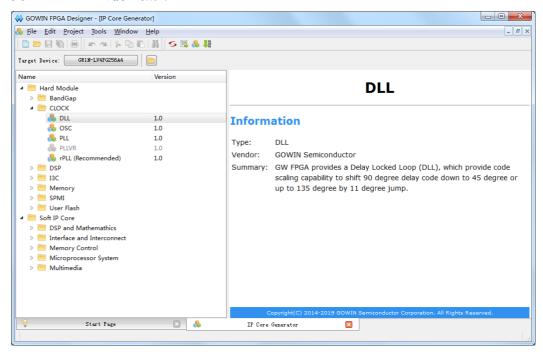

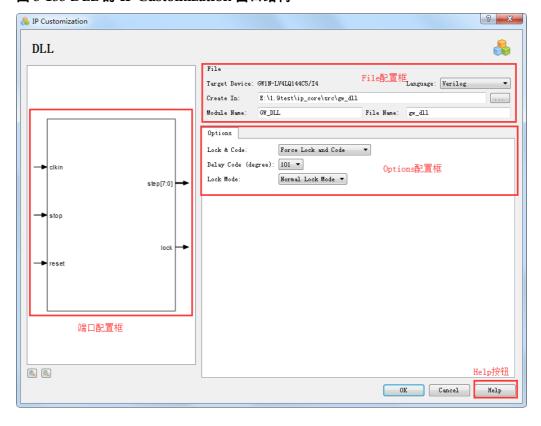

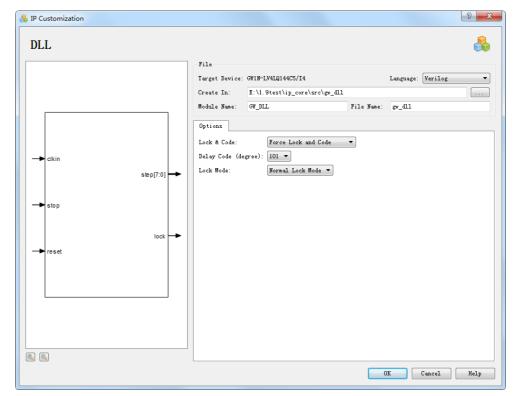

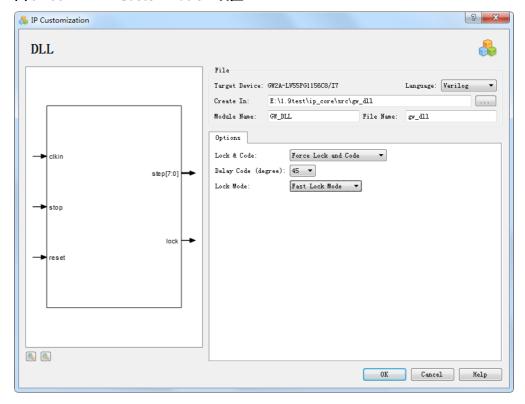

| 图 3-132 DLL 的信息概要                                 | 108 |

| 图 3-133 DLL 的 IP Customization 窗口结构               | 108 |

| 图 3-134 Help 信息                                   | 109 |

| 图 3-135 配置的 IP Customization                      | 110 |

| 图 3-136 例化 DLL 设计文件                               | 111 |

| 图 3-137 用户例化该 IP 设计文件的模板文件                        | 111 |

| 图 3-138 DLL IP Customization 设置                   | 112 |

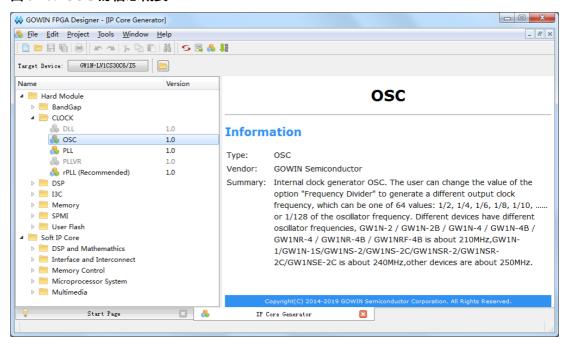

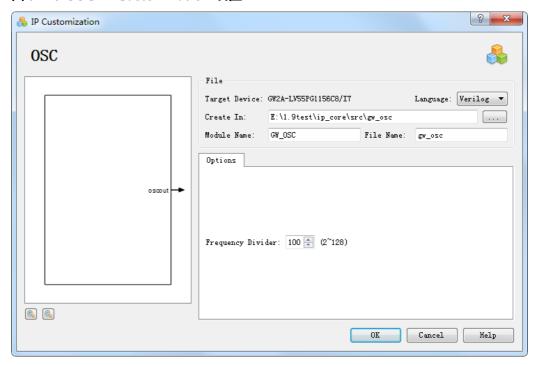

| 图 3-139 OSC 的信息概要                                 | 112 |

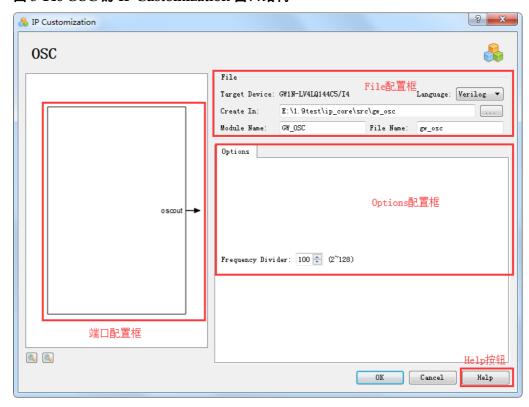

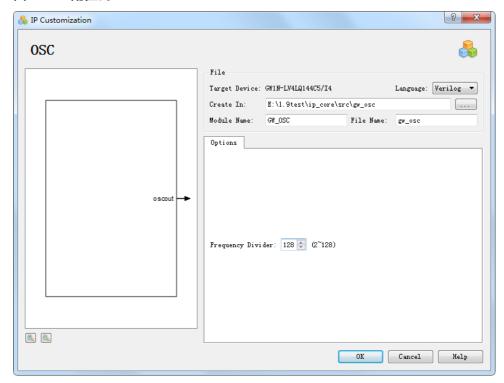

| 图 3-140 OSC 的 IP Customization 窗口结构               | 113 |

| 图 | 3-141 | Help 信息                            | 114 |

|---|-------|------------------------------------|-----|

| 图 | 3-142 | 配置的 IP Customization               | 114 |

| 图 | 3-143 | 例化 OSC 设计文件                        | 115 |

| 图 | 3-144 | 用户例化该 IP 设计文件的模板文件                 | 115 |

| 图 | 3-145 | OSC IP Customization 设置            | 116 |

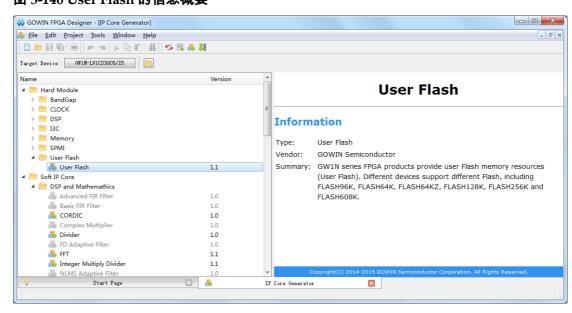

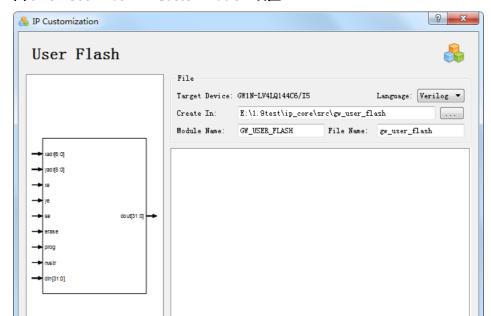

| 图 | 3-146 | User Flash 的信息概要                   | 116 |

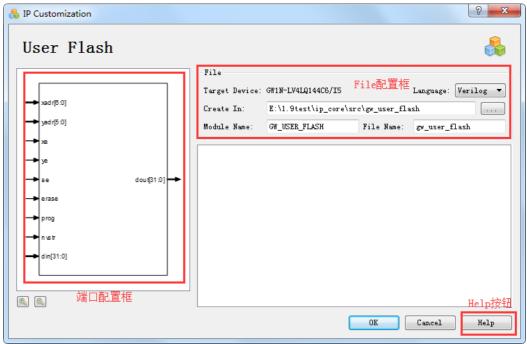

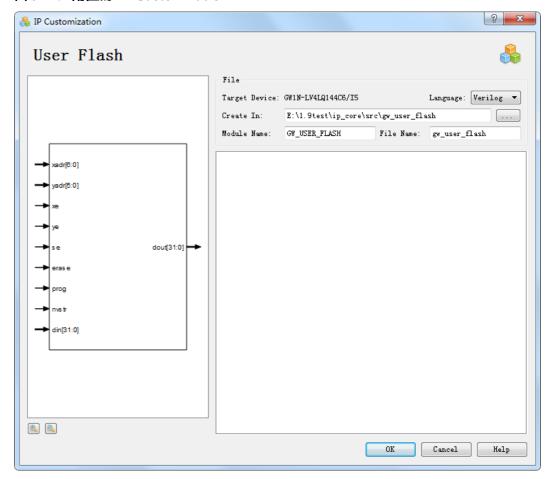

| 图 | 3-147 | User Flash 的 IP Customization 窗口结构 | 117 |

| 图 | 3-148 | Help 信息                            | 118 |

| 图 | 3-149 | 配置的 IP Customization               | 119 |

| 图 | 3-150 | 例化 User Flash 设计文件                 | 120 |

| 图 | 3-151 | 用户例化该 IP 设计文件的模板文件                 | 120 |

| 图 | 3-152 | User Flash IP Customization 设置     | 121 |

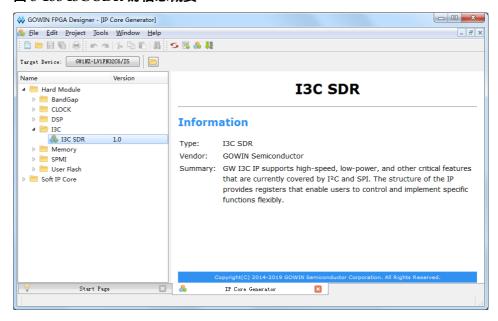

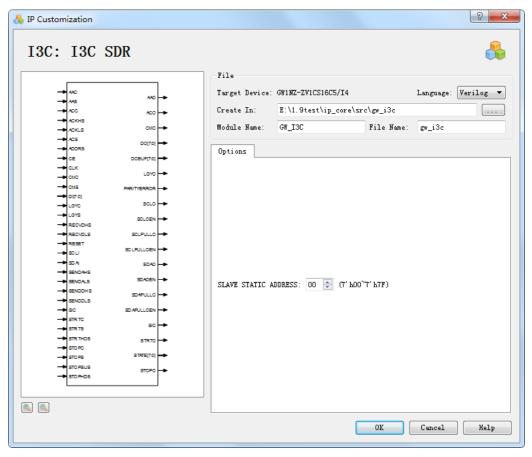

| 图 | 3-153 | I3C SDR 的信息概要                      | 121 |

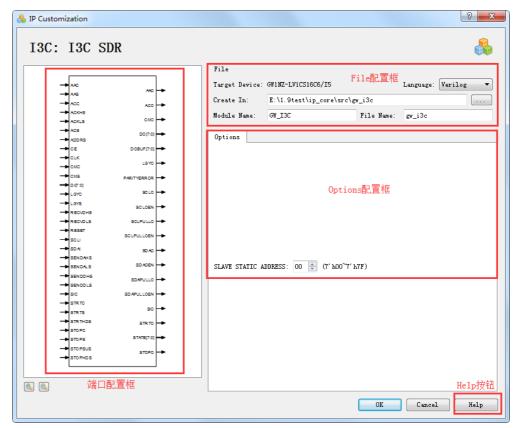

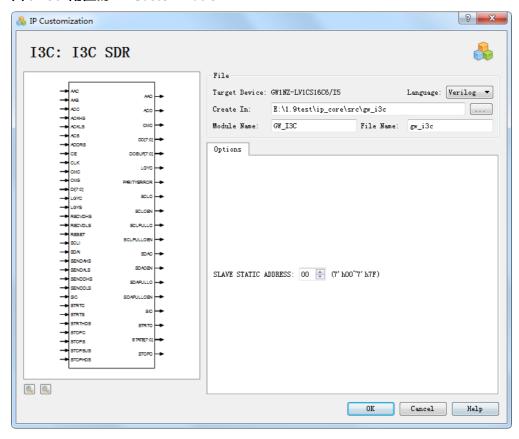

| 图 | 3-154 | I3C 的 IP Customization 窗口结构        | 122 |

| 图 | 3-155 | Help 信息                            | 123 |

| 图 | 3-156 | 配置的 IP Customization               | 124 |

| 图 | 3-157 | 例化 I3C 设计文件                        | 125 |

| 图 | 3-158 | 用户例化该 IP 设计文件的模板文件                 | 128 |

| 图 | 3-159 | I3C IP Customization 设置            | 129 |

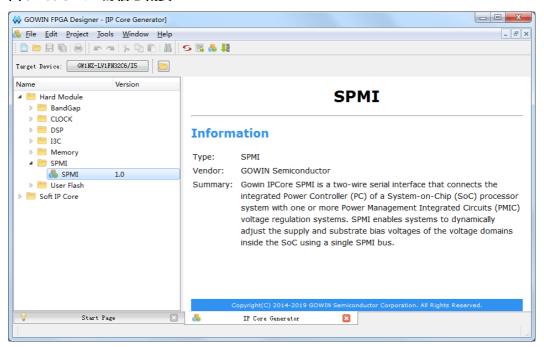

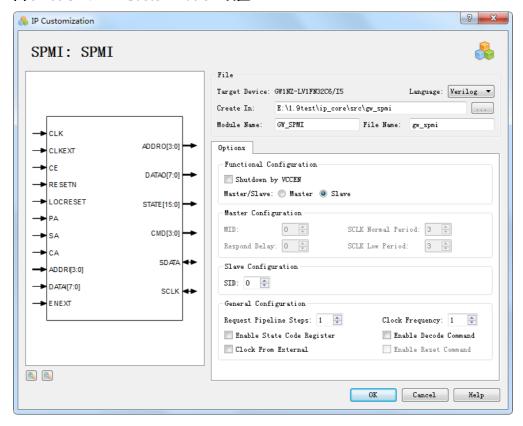

| 图 | 3-160 | SPMI 的信息概要                         | 130 |

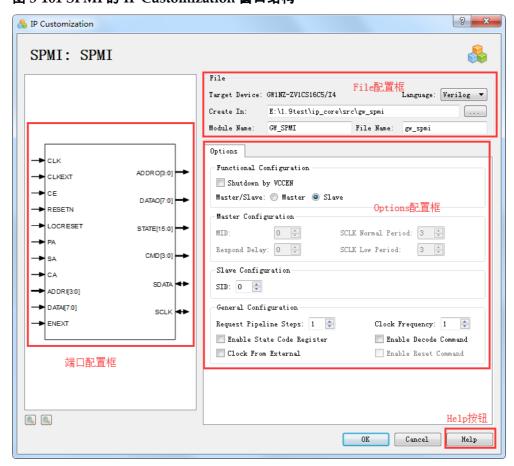

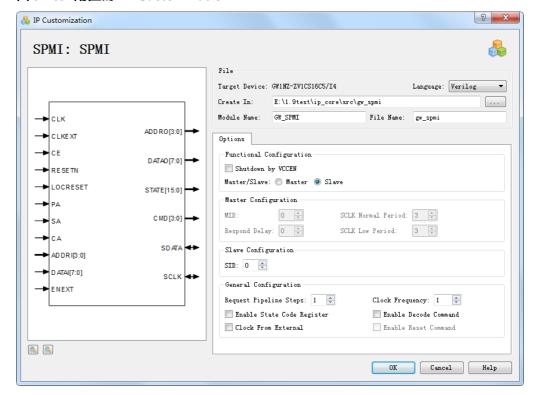

| 图 | 3-161 | SPMI 的 IP Customization 窗口结构       | 130 |

| 图 | 3-162 | Help 信息                            | 132 |

| 图 | 3-163 | 配置的 IP Customization               | 133 |

| 图 | 3-164 | 例化 SPMI 设计文件                       | 134 |

| 图 | 3-165 | 用户例化该 IP 设计文件的模板文件                 | 135 |

| 图 | 3-166 | SPMI IP Customization 设置           | 136 |

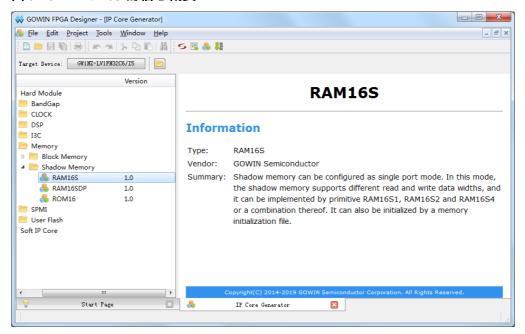

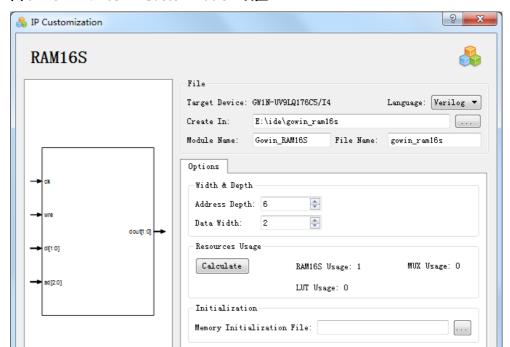

| 图 | 3-167 | RAM16S 的信息概要                       | 137 |

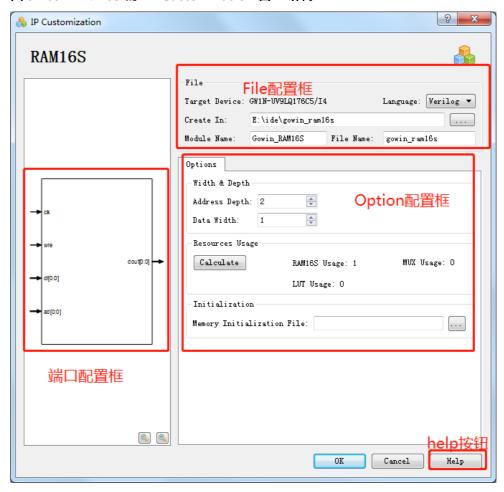

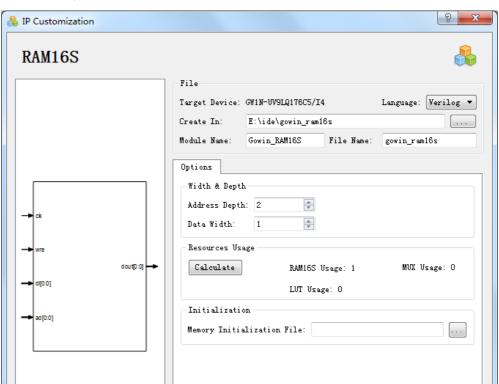

|   |       | RAM16S 的 IP Customization 窗口结构     |     |

| 图 | 3-169 | Help 信息                            | 139 |

| 图 | 3-170 | 配置的 IP Customization               | 140 |

| 图 | 3-171 | 例化 RAM16S 设计文件                     | 141 |

| 图 | 3-172 | 用户例化该 IP 设计文件的模板文件                 | 141 |

| 图 | 3-173 | RAM16S IP Customization 设置         | 142 |

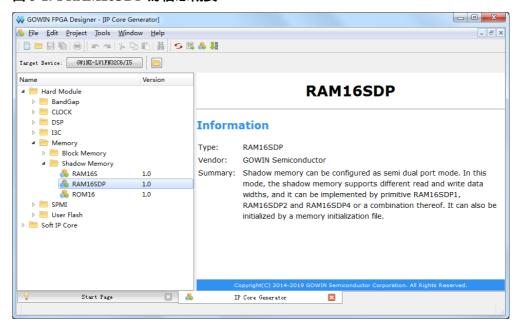

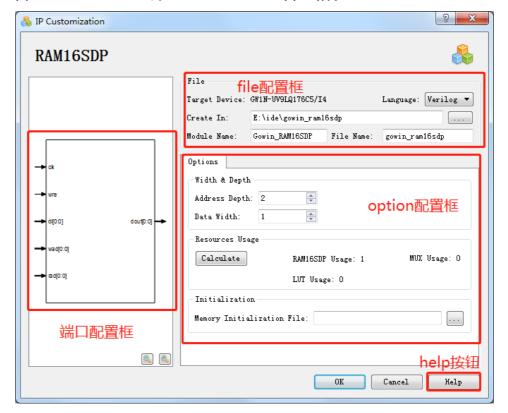

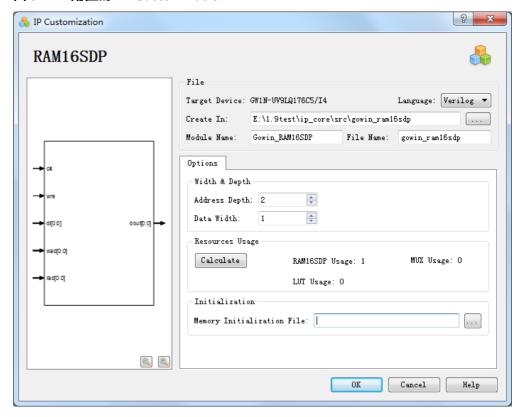

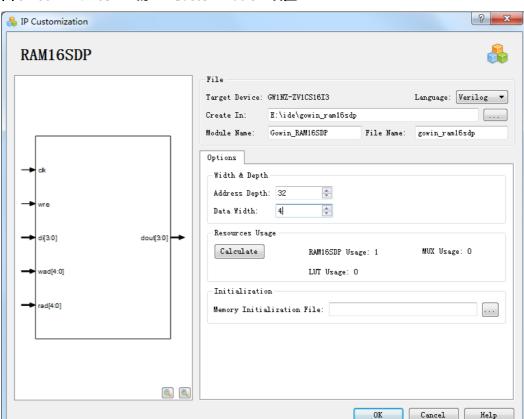

| 图 | 3-174 | RAM16SDP 的信息概要                     | 142 |

|   |       | RAM16SDP 的 IP Customization 窗口结构   |     |

| 图 | 3-176 | Help 信息                            | 144 |

| 图 | 3-177 | 配置的 IP Customization               | 145 |

| 图 3-178 | 例化 RAM16SDP 设计文件                | 146 |

|---------|---------------------------------|-----|

| 图 3-179 | 用户例化该 IP 设计文件的模板文件              | 146 |

| 图 3-180 | RAM16SDP 的 IP Customization 设置  | 147 |

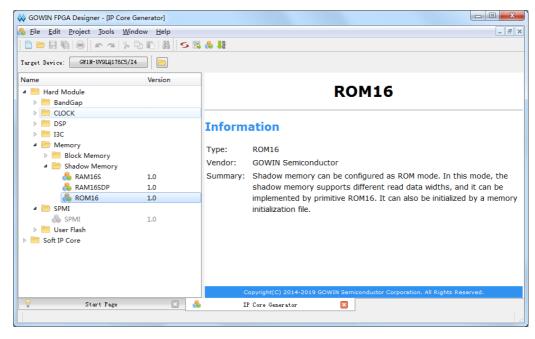

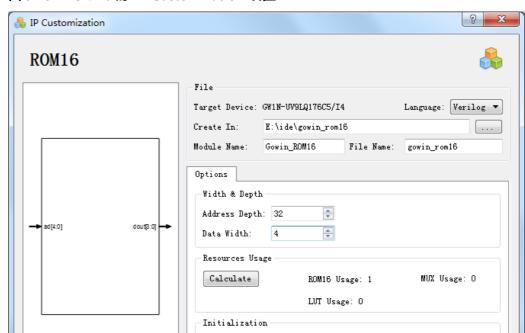

| 图 3-181 | ROM16 的信息概要                     | 147 |

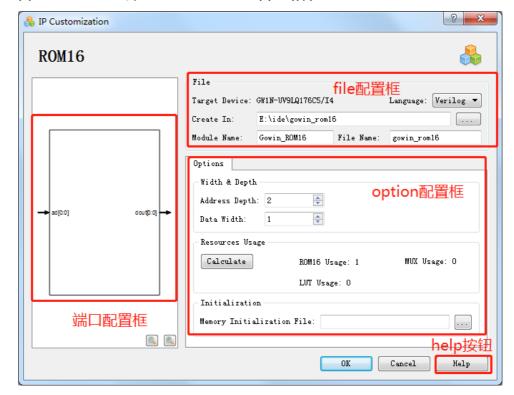

| 图 3-182 | ROM16 的 IP Customization 窗口结构   | 148 |

| 图 3-183 | Help 信息                         | 149 |

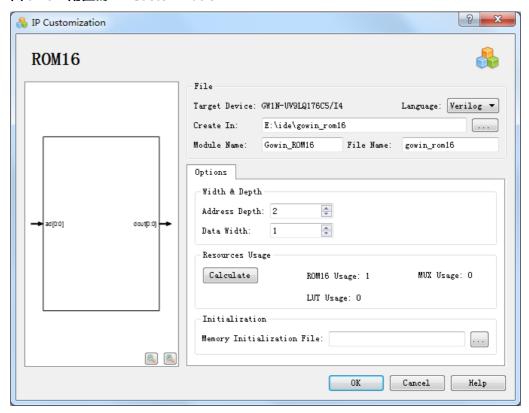

| 图 3-184 | 配置的 IP Customization            | 150 |

| 图 3-185 | 例化 ROM16 设计文件                   | 151 |

| 图 3-186 | 用户例化 IP 设计文件的模板文件               | 151 |

| 图 3-187 | ROM16 的 IP Customization 设置     | 152 |

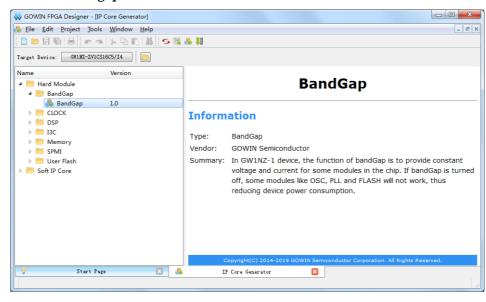

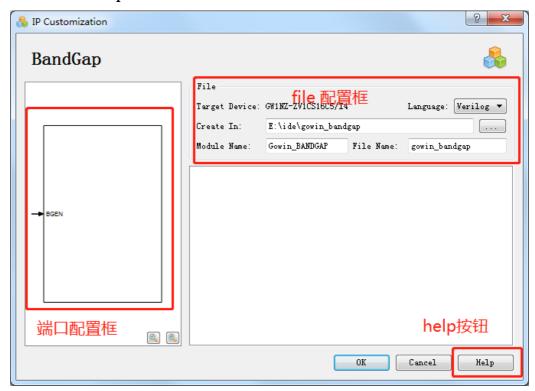

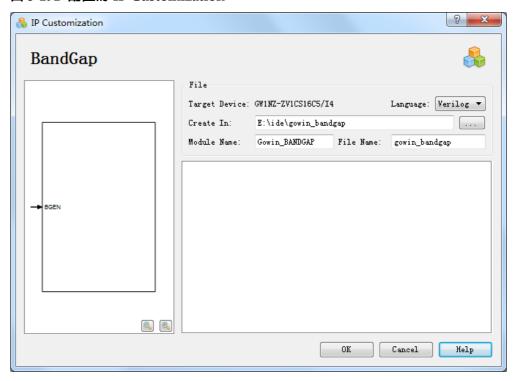

| 图 3-188 | Bandgap 的信息概要                   | 152 |

| 图 3-189 | BandGap 的 IP Customization 窗口结构 | 153 |

| 图 3-190 | Help 信息                         | 153 |

| 图 3-191 | 配置的 IP Customization            | 154 |

| 图 3-192 | 例化 BandGap 设计文件                 | 154 |

| 图 3-193 | 用户例化该 IP 设计文件的模板文件              | 155 |

# 表目录

| 主 4 4 予注  | 4字冊欠3五 | _     |

|-----------|--------|-------|

| 衣 1-1 小岇、 |        | <br>2 |

SUG284-1.9 ix

1 关于本手册 1.1 手册内容

#

### 1.1 手册内容

本手册主要描述高云半导体云源软件(Gowin 云源软件)的 IP 核产生工具(IP Core Generator)的使用,旨在帮助用户快捷实现复杂设计。Gowin 云源软件支持 Linux 和 Windows 系统。有关本手册中的软件界面截图和支持的产品列表等信息,参考的是 Windows 系统的 1.9.3Beta 版本。因软件版本更新,部分信息可能会略有差异,具体以用户软件版本信息为准。

## 1.2 适用产品

本手册中描述的信息适用于以下产品:

- GW1N 系列 FPGA 产品: GW1N-1, GW1N-2, GW1N-2B, GW1N-4, GW1N-4B, GW1N-6, GW1N-9, GW1N-1S

- GW1NR 系列 FPGA 产品: GW1NR-4, GW1NR-4B, GW1NR-9

- GW1NS 系列 FPGA 产品: GW1NS-2, GW1NS-2C, GW1NS-4

- GW2A 系列 FPGA 产品: GW2A-55, GW2A-18

- GW2AR 系列 FPGA 产品: GW2AR-18

- GW1NZ 系列 FPGA 产品: GW1NZ-1

- GW1NSR 系列 FPGA 产品: GW1NSR-2, GW1NSR-2C, GW1NSR-4, GW1NSR-4C

- GW1NRF 系列蓝牙 FPGA 产品: GW1NRF-4B

- GW1NSE 系列安全 FPGA 产品: GW1NSE-2C

- GW1NSER 系列安全 FPGA 产品: GW1NSER-4C

## 1.3 相关文档

通过登录高云半导体网站 <u>www.gowinsemi.com.cn</u>可下载、查看以下相关文档:

- 1. DS100, GW1N 系列 FPGA 产品数据手册

- 2. DS117, GW1NR 系列 FPGA 产品数据手册

- 3. DS821, GW1NS 系列 FPGA 产品数据手册

- 4. DS102, GW2A 系列 FPGA 产品数据手册

- 5. DS226, GW2AR 系列 FPGA 产品数据手册

- 6. DS841, GW1NZ 系列 FPGA 产品数据手册

SUG284-1.9 1(155)

1 关于本手册 1.4 术语、缩略语

- 7. <u>DS861</u>, GW1NSR 系列 FPGA 产品数据手册

- 8. DS891, GW1NRF 系列蓝牙 FPGA 产品数据手册

- 9. DS871, GW1NSE 系列安全 FPGA 产品数据手册

- 10. DS881, GW1NSER 系列安全 FPGA 产品数据手册

## 1.4 术语、缩略语

本手册中出现的相关术语、缩略语及相关释义请参考表 1-1。

表 1-1 术语、缩略语

| 术语、缩略语      | 全称                                 | 含义       |

|-------------|------------------------------------|----------|

| FPGA        | Field Programmable Gate Array      | 现场可编程门阵列 |

| IDE         | Integrated Development Environment | 集成开发环境   |

| IP Core     | Intellectual Property Core         | 知识产权核    |

| DP/DPX9     | Dual Port                          | 双端口存储器   |

| DPB/DPBX9   | Dual Port                          | 双端口存储器   |

| SP/SPX9     | Single Port                        | 单端口存储器   |

| SDP/SDPX9   | Semi-dual Port                     | 半双端口存储器  |

| SDPB/SDPBX9 | Semi-dual Port                     | 半双端口存储器  |

| rSDP/rSDPX9 | Semi-dual Port                     | 半双端口存储器  |

| ROM/ROMX9   | Read Only Memory                   | 只读存储器    |

| rROM/rROMX9 | Read Only Memory                   | 只读存储器    |

| pROM/pROMX9 | Read Only Memory                   | 只读存储器    |

| PADD        | Pre-adder                          | 前加器      |

| MULT        | Multiplier                         | 乘法器      |

| PLL         | Phase-locked Loop                  | 锁相环      |

| rPLL        | Phase-locked Loop                  | 锁相环      |

| PLLVR       | Phase-locked Loop                  | 锁相环      |

| DLL         | Delay Lock Loop                    | 延迟锁相环    |

| OSC         | Oscillator                         | 片内晶振     |

| SPMI        | System Power Management Interface  | 系统电源管理接口 |

# 1.5 技术支持与反馈

高云半导体提供全方位技术支持,在使用过程中如有任何疑问或建议,可直接与公司联系:

网址: <u>www.gowinsemi.com.cn</u> E-mail: <u>support@gowinsemi.com</u>

Tel: +86 755 8262 0391

SUG284-1.9 2(155)

# 26介

Gowin 云源软件 IP 核产生工具主要用于产生实例化的元件以及 IP,通过工具产生实例化的设计之后,用户可调用该实例化模块实现设计所需的功能,帮助用户快捷实现复杂设计。目前 IP Core Generator 包括原语相关的 Hard Module 部分和参考设计相关的 Soft IP Core 两个组成部分。

SUG284-1.9 3(155)

# **3**使用

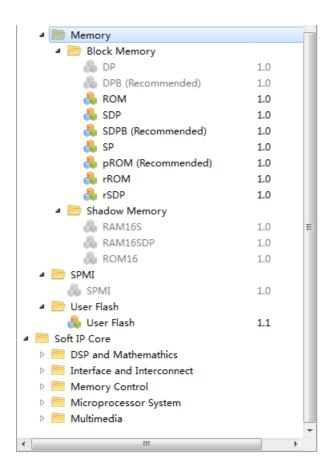

通过选择菜单栏 "Tools > IP Core Generator",或工具栏 " ",打 TIP Core Generator 界面,如图 3-1 所示。

该界面主要分为以下两个部分:

- 原语相关的 Hard Module 部分;

- 参考设计相关的 Soft IP Core 部分。

Hard Module 部分包括 BandGap、CLOCK、DSP、I3C、Memory、SPMI

和 User Flash 等:

Soft IP Core 部分包括 DSP and Mathematics、Interface and Interconnect、Memory Control、Microprocessor System、Multimedia 等。 本文档主要介绍 Hard Module 模块的使用。

#### 图 3-1 IP Core Generator 界面

SUG284-1.9 4(155)

界面顶端有两个控件,"Target Device" 按钮和 IP Core 配置文件打开按钮 "—"。

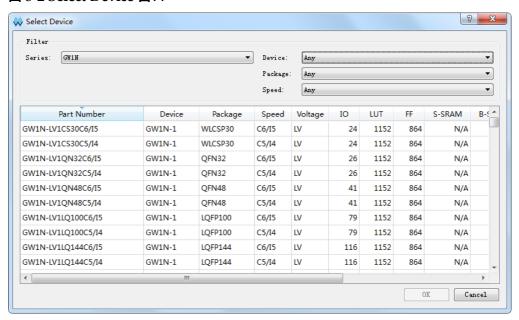

Target Device, 配置 Device。选择右侧显示框, 弹出"Select Device"窗口, 如图 3-2 所示。

通过该窗口可修改 Device 信息,修改后的内容显示在 Target Device 的右侧显示框中,双击某高亮显示的 IP,可打开 IP Customization 的对话框,修改后的 Device 信息也会显示在 IP Customization 对话框的 File 配置窗口的"Target Device"显示框中。

SUG284-1.9 5(155)

#### 图 3-2 Select Device 窗口

选定 Deivce 后, IP Core Generator 会根据设定的 Device 自动判断是否支持特定模块。

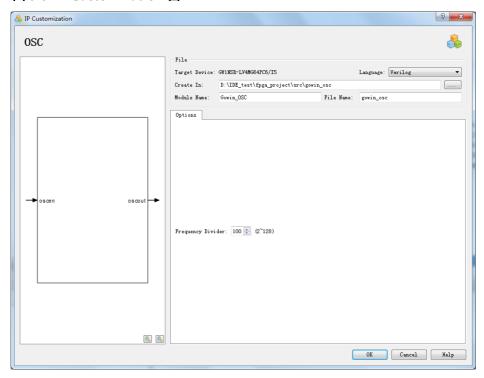

- 若支持,模块名为高亮,双击可打开"IP Customization"配置窗口,如图 3-3 中所示,用户可通过 IP Customization 配置窗口来配置 IP,配置完成后点击"OK"生成 IP,各 IP 的配置界面将在第三章的各个小节介绍:

- 若不支持,则模块名为灰色,不可用。如图 3-1 中所示, GW1NSR-4 不 支持 "SPMI"。

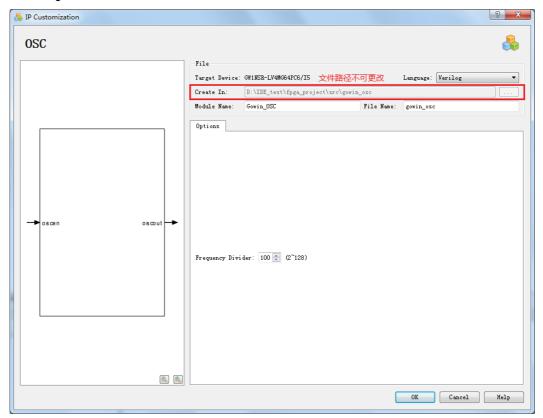

图标"—",用于打开已配置好的 IP Core 文件,并可根据需要进行编辑。点击图标,弹出"Select IP Config file"对话框,选择 IP Core 配置文件".ipc",弹出如图 3-4 所示的"IP Customization"页面,可对配置重新编辑,其中文件路径不可更改。

SUG284-1.9 6(155)

#### 图 3-3 IP Customization 窗口

### 图 3-4 ipc 文件的 IP Customization 窗口

SUG284-1.9 7(155)

## 3.1 Block Memory

当前,Block Memory (BSRAM) 模块可实现 SP (单端口模式)、SDP (半双端口模式)、rSDP (半双端口模式)、SDPB (半双端口模式)、DP (双端口模式)、pROM (只读模式)和ROM (只读模式)。

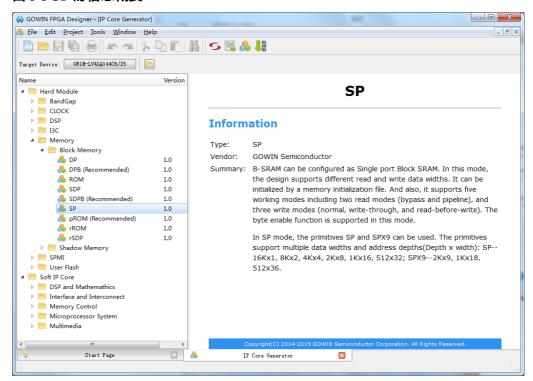

#### 3.1.1 SP

SP 为单端口工作模式,可以通过 SP、SPX9 两种高云器件实现。BSRAM 的最大存储容量根据芯片型号的不同而不同。在 IP Core Generator 界面中,单击 SP,界面右侧会显示 SP 的相关信息概要如图 3-5 所示。

#### 图 3-5 SP 的信息概要

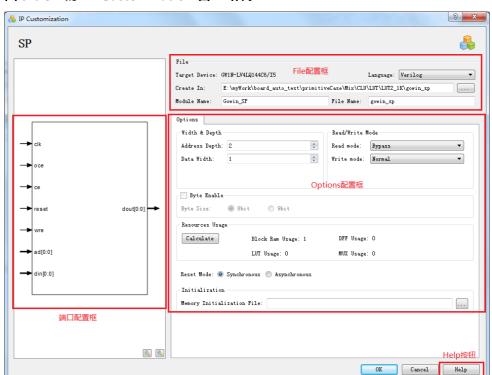

在 IP Core Generator 界面中,双击"SP",弹出"IP Customization"窗口,该窗口包括"File"配置框、"Options"配置框、端口配置框图和帮助按钮"Help",如图 3-6 所示。

SUG284-1.9 8(156)

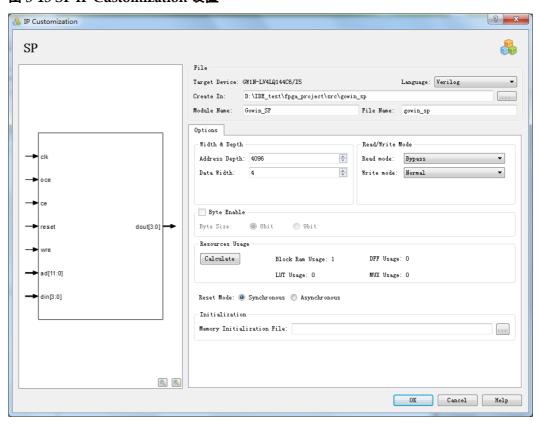

#### 图 3-6 SP的 IP Customization 窗口结构

#### 1. File 配置框

- File 配置框用于配置产生的 SP 实例化文件的相关信息。

- Target Device: 显示已配置的 Device 信息;

- Language: 配置产生的 IP Core 文件的硬件描述语言。选择右侧下 拉列表框,选择目标语言,支持 Verilog 和 VHDL,如图 3-7 所示;

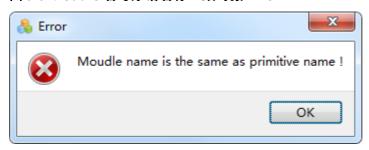

- Module Name: 配置产生的 IP Core 文件的 module name。在右侧文本框可重新编辑模块名称。Module Name 不能与原语名称相同,若相同,则报出 Error,提示"Module name is the same as primitive name!"如图 3-8 所示;

- File Name: 配置产生的 IP Core 文件的文件名。在右侧文本框可重新编辑文件名称;

- Create In: 配置产生的 IP Core 文件的目标路径。可在右侧文本框中 重新编辑目标路径,也可通过文本框右侧选择按钮选择目标路径。

#### 图 3-7 Language 下拉列表框

SUG284-1.9 9(155)

#### 图 3-8 Module 名与原语名称一致时报 Error

#### 2. Options 配置框

Options 配置框用于用户自定义单端口模式存储器的配置信息,Options 配置框如图 3-6 所示。

- Width & Depth: 配置 SP 的地址深度(Address Depth)和数据宽度 (Data Width)。当配置的地址深度和数据宽度无法通过单个模块实现时,IP Core 会实例化多个模块组合实现;

- Byte Enable: 用于配置是否使用字节写使能功能,当 Data Width 大于等于 9 时可勾选;当使用字节写使能功能时配置使能字节的大小,可选用 8 bit 或 9 bit;

- Resource Usage: 计算并显示当前容量配置上占用的 Block Ram、 DFF、LUT、MUX 的资源情况:

- Read/Write Mode: 配置读写模式。

- SP 支持以下模式:

- 两种读模式: Bypass 和 Pipeline;

- 三种写模式: Nomal、Write-Through、Read-before-Write;

- Reset Mode: 配置 SP 的复位模式;

- 支持同步模式 "Synchronous" 和异步模式 "Asynchronous";

- Initialization: 配置 SP 的 INIT 值;

- INIT 值以二进制或十六进制的格式写在初始化文件中,文件可通过 "Memory Initialization File"指定。

#### 注!

"Memory Initialization File"选取的初始化文件可通过手写或者 IDE 菜单栏 "File > New > Memory Initialization File"产生,具体产生方式及初始化文件的格式请参考文档<u>《Gowin</u> <u>云源软件用户指南》。</u>

- 3. 端口配置框图

- 端口配置框图显示当前 IP Core 的配置结果示例框图,输入输出端口的位宽根据 Options 配置实时更新,如图 3-6 中标注的端口配置框图所示。

- Options 配置中的地址深度 "Address Depth"配置影响 ad 的位宽,数据位宽 "Data Width"配置影响 din 和 dout 的位宽。

- 4. Help 按钮

单击 "Help",显示 IP Core 的配置信息的页面,如图 3-9 所示。

SUG284-1.9 10(155)

#### 图 3-9 Help 信息

SP

#### Information

| Type:    | SP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vendor:  | GOWIN Semiconductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Summary: | B-SRAM can be configured as Single port Block SRAM. In this mode, the design supports different read and write data widths. It can be initialized by a memory initialization file. And also, it supports five working modes including two read modes (bypass and pipeline), and three write modes (normal, write-through, and read-before-write). The byte enable function is supported in this mode.  In SP mode, the primitives SP and SPX9 can be used. The primitives support multiple data widths and address depths(Depth x width): SP16Kx1, 8Kx2, 4Kx4, 2Kx8, 1Kx16, 512x32; SPX92Kx9, 1Kx18, 512x36. |

#### Options

| Option          | Description                                                                                                                                                                                      |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Width & Depth   | Address Depth - Set the size of the address depth.                                                                                                                                               |

|                 | Data Width - Set the size of the data width.                                                                                                                                                     |

| Read/Write Mode | Read Mode - Set whether the read mode is bypass mode or pipeline mode.                                                                                                                           |

|                 | Write Mode - Set the write mode as normal mode, write-through mode or read-before-write mode.                                                                                                    |

| Byte Enable     | Byte Enable - Set whether to use byte enable function or not.                                                                                                                                    |

|                 | Byte Size - Set whether the byte size is 8bit or 9bit if the byte enable selected.                                                                                                               |

|                 | Note: Assume that the data width is represented by Width. (1) If Width<=8, byte enable function is invalid; (2) If Width=9, only 8 bit is valid; (3) If Width>9, both 8 bit and 9 bit are valid. |

|                 | Calculate - Calculate the resource usage in the design and display results below.                                                                                                                |

|                 | Block Ram Usage - Display the number of Block Ram used.                                                                                                                                          |

| Resource Usage  | DFF Usage - Display the number of DFF used.                                                                                                                                                      |

|                 | LUT Usage - Display the number of LUT used.                                                                                                                                                      |

|                 | MUX Usage - Display the number of MUX used.                                                                                                                                                      |

| Reset Mode      | Reset Mode - Set whether the reset mode is synchronous mode or asynchronous mode.                                                                                                                |

| Initialization  | Memory Initialization File - Set the memory initialization file (.mi) path.                                                                                                                      |

Help 页面包括当前 IP Core 的概要介绍,以及 Options 各项配置的简要说明。

#### IP 生成文件

如图 3-10 所示, SP 的"IP Customization"窗口完成配置后, 单击"OK", 产生以配置文件"File Name"命名的三个文件:

- 例化高云原语 SP 设计文件 "gowin\_sp.v";

- 用户例化该 IP 设计文件的模板文件 "gowin sp tmp.v";

- 例化原语 SP 的配置文件 "gowin\_sp.ipc"。

#### 注!

如配置中选择的语言是 VHDL,则产生的前两个文件名后缀为.vhd。下述以 verilog 语言为例介绍产生的文件。

SUG284-1.9 11(155)

#### 图 3-10 配置的 IP Customization

#### 例化 SP 设计文件

例化 SP 设计文件为完整的 verilog 模块,模块中根据"IP Customization"中的 SP 配置,产生实例化的 SP,如图 3-11 所示。

#### 图 3-11 例化 SP 设计文件

SUG284-1.9 12(155)

#### 用户例化该 IP 设计文件的模板文件

IP Core Generator 工具考虑用户的实际应用,在产生例化 SP 设计文件的同时,亦提供用户例化该 IP 设计文件的模板文件,如图 3-12 所示。

#### 图 3-12 用户例化该 IP 设计文件的模板文件

```

Gowin_SP your_instance_name(

.dout(dout_o), //output [0:0] dout

.clk(clk_i), //input clk

.oce(oce_i), //input oce

.ce(ce_i), //input ce

.reset(reset_i), //input reset

.wre(wre_i), //input wre

.ad(ad_i), //input [0:0] ad

.din(din_i) //input [0:0] din

);

```

#### IP Core Generator 生成 SP 示例

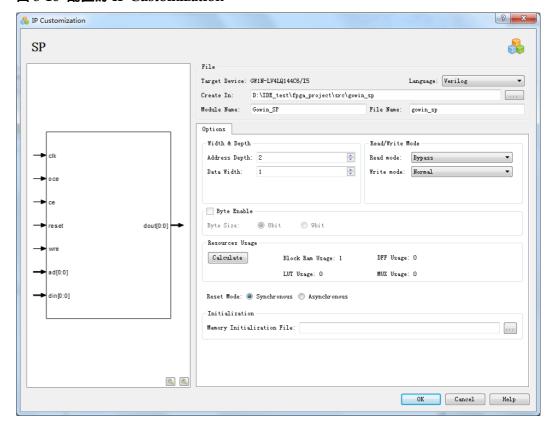

如用户需产生 4096X4、Bypass 读模式、Normal 写模式、同步复位模式下的 SP IP,以 device 选择 GW1N-LV4LQ144C6/I5 为例,界面配置如图 3-13 所示,可根据用户需要在 Initialization 窗口配置初始化文件,单击"OK",产生用户所需的 SP IP 设计文件。

产生的 SP IP 设计文件所在目录即为配置界面中"Create In"设置路径。

#### 图 3-13 SP IP Customization 设置

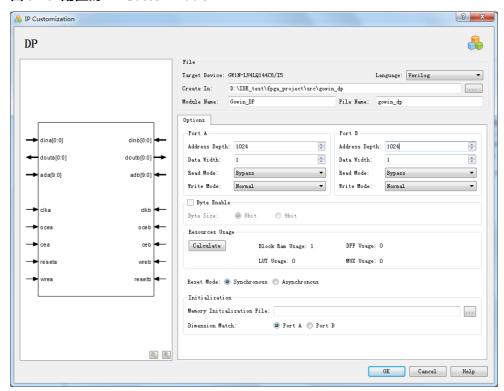

#### 3.1.2 DP

DP 是双端口工作模式,可通过 DP、DPX9 两种高云器件实现, BSRAM

SUG284-1.9 13(155)

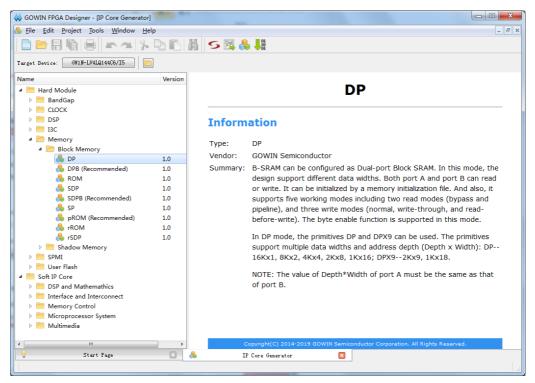

的最大存储容量根据芯片型号的不同而不同。在 IP Core Generator 界面中,单击"DP",界面右侧会显示 DP 的相关信息概要,如图 3-14 所示。

#### 图 3-14 DP 的信息概要

在 IP Core Generator 界面中,双击"DP",弹出 DP 的"IP Customization" 窗口。该窗口包括"File"配置框、"Options"配置框、端口配置框图和帮助按钮 "Help",如图 3-15 所示。

SUG284-1.9 14(155)

#### 💲 IP Customization ? X DP Target Device: GW1N-LV4LQ144C6/I5 File配置框 Language: Verilog Create In: D:\IDE test\fpga project\src\gowin dp Module Name: Gowin\_DF File Name: gowin\_dp Port A Port B dina[0:0] dinb[0:0] Address Depth: 2 Address Depth: 2 \* douta[0:0] doutb[0:0] \* Data Width: -Data Width: • Read Mode: Read Mode: adb[0:0] Write Mode: Write Mode: dkb Options配置框 oceb Resources Usage -DFF Usage: 0 Calculate Block Ram Usage: 1 LUT Usage: 0 MUX Usage: O wreb Reset Mode: Synchronous Asynchronous 端口配置框 Port A Port B Dimension Match: Help按钮 OK Cancel Help

#### 图 3-15 DP 的 IP Customization 窗口结构

#### 1. File 配置框

File 配置框用于配置产生 DP 实例化文件的相关信息,如图 3-15 中标注的 File 配置框所示。

DP 的 File 配置框的使用和 SP 模块类似, 具体请参考 <u>3.1</u>Block Memory > 3.1.1SP 的 File 配置框。

#### 2. Options 配置框

Options 配置框用于用户自定义双端口模式存储器的配置信息,如图 3-15 中 Options 配置框所示。

DP 的 Options 配置框的使用和 SP 模块类似,具体请参考 <u>3.1</u> Block Memory > <u>3.1.1</u>SP 中的 Options 配置框。

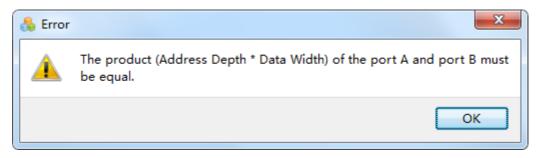

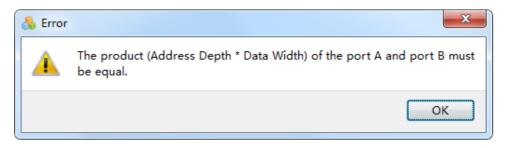

配置 DP 时,需注意以下事项:

- Options 配置框中可独立配置 DP 的 Port A 和 Port B 的地址深度、数据 宽度和读写模式。

- DP 的 Port A 和 Port B 是对同一块 memory 进行读写,因此 Port A 和 Port B 的 Address Depth\*Data Width 的结果必须相同。

- Options 配置中的初始化文件(Memory initialization File)中的数据宽度 应与 Dimension Match 选择的 Port 数据宽度一致。

#### 注:

- 如 Port A 和 Port B 的 Address Depth\*Data Width 的结果不同,则会弹出如图 3-16 所示的 Error 提示信息。

- 如数据宽度不一致,则产生的 DP 实例 Init 值默认初始化为 0,并且在 Output 窗口中,会弹出如下提示信息:

Error (MG2105): Initial values' width is unequal to user's width.

SUG284-1.9 15(155)

#### 图 3-16 DP 配置 Error 提示

#### 3. 端口配置框图

- 配置框图显示当前 IP Core 的配置结果示例框图,输入输出端口的位 宽根据 Options 配置实时更新,如图 3-15 中标注的端口配置框所示;

- Options 配置中的 Port A 和 Port B 的地址深度 Address Depth 配置 影响 ada 和 adb 的位宽,数据位宽 Data Width 配置影响 dina/douta 和 dinb/doutb 的位宽。

- 4. Help 按钮

单击"Help",显示 IP Core 的配置信息的页面,如图 3-17 所示。

#### 图 3-17 Help 信息

DP

#### Information

| Type:    | DP                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vendor:  | GOWIN Semiconductor                                                                                                                                                                                                                                                                                                                                                                                                           |

| Summary: | B-SRAM can be configured as Dual-port Block SRAM. In this mode, the design support different data widths. Both port A and port B can read or write. It can be initialized by a memory initialization file. And also, it supports five working modes including two read modes (bypass and pipeline), and three write modes (normal, write-through, and read-before-write). The byte enable function is supported in this mode. |

|          | In DP mode, the primitives DP and DPX9 can be used. The primitives support multiple data widths and address depth (Depth x Width): DP16Kx1, 8Kx2, 4Kx4, 2Kx8, 1Kx16; DPX92Kx9, 1Kx18.                                                                                                                                                                                                                                         |

|          | NOTE: The value of Depth*Width of port A must be the same as that of port B.                                                                                                                                                                                                                                                                                                                                                  |

#### **Options**

| Option                                  | Description                                                                                                                                                                                      |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port A                                  | Address Depth - Set the size of the address depth.                                                                                                                                               |

|                                         | Data Width - Set the size of the Data width.                                                                                                                                                     |

|                                         | Read Mode - Set whether the read mode is bypass mode or pipeline mode.                                                                                                                           |

|                                         | Write Mode - Set the write mode as normal mode, write-through mode or read-before-write mode.                                                                                                    |

| Port B                                  | Address Depth - Set the size of the address depth.                                                                                                                                               |

|                                         | Data Width - Set the size of the Data width.                                                                                                                                                     |

|                                         | Read Mode - Set whether the read mode is bypass mode or pipeline mode.                                                                                                                           |

|                                         | Write Mode - Set the write mode as normal mode, write-through mode or read-before-write mode.                                                                                                    |

|                                         | Byte Enable - Set whether to use byte enable function or not.                                                                                                                                    |

| Byte Enable                             | Byte Size - Set whether the byte size is 8bit or 9bit if the byte enable checkbox selected.                                                                                                      |

|                                         | Note: Assume that the data width is represented by Width. (1) If Width<=8, byte enable function is invalid; (2) If Width=9, only 8 bit is valid; (3) If Width>9, both 8 bit and 9 bit are valid. |

|                                         | Calculate - Calculate the resource usage in the design and display results below.                                                                                                                |

|                                         | Block Ram Usage - Display the number of Block Ram used.                                                                                                                                          |

| Resource Usage                          | DFF Usage - Display the number of DFF used.                                                                                                                                                      |

|                                         | LUT Usage - Display the number of LUT used.                                                                                                                                                      |

|                                         | MUX Usage - Display the number of MUX used.                                                                                                                                                      |

| Reset Mode                              | Reset Mode - Set whether the reset mode is synchronous mode or asynchronous mode.                                                                                                                |

| Initialization                          | Memory Initialization File - Set the memory initialization file (.mi) path.                                                                                                                      |

| IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII | Dimension Match - Set which port's dimensions the memory initialization file should conform to.                                                                                                  |

Help 页面包括当前 IP Core 的概要介绍,以及 Options 各项配置的简要

SUG284-1.9 16(155)

说明。

#### IP 生成文件

如图 3-18 所示, DP 的 IP Customization 窗口配置完成后, 单击"OK", 产生以配置文件"File Name"命名的三个文件:

- 例化高云原语 DP 设计文件 "gowin\_dp.v";

- 用户例化该 IP 设计文件的模板文件 "gowin dp tmp.v";

- 例化原语 DP 的配置文件 "gowin\_dp.ipc"。

如配置中选择的语言是 VHDL,产生的前两个文件名后缀为.vhd。下述以 verilog 语言为例介绍产生的文件。

#### 图 3-18 配置的 IP Customization

#### 例化 DP 设计文件

例化 DP 设计文件为完整的 verilog 模块,模块中根据 IP Customization 中的 DP 配置,产生实例化的 DP,如图 3-19 所示。

SUG284-1.9 17(155)

#### 图 3-19 例化 DP 设计文件

```

module Gowin DP (douta, doutb, clka, ocea, cea, reseta, wrea, clkb, oceb, ceb, resetb, wreb, ada, dina, adb, dinb);

output [0:0] douta;

output [0:0] doutb;

input clka;

input ocea;

input cea;

input reseta;

input clkb;

input oceb;

input ceb;

input resetb;

input [0:0] ada;

input [0:0] dina;

input [0:0] adb;

input [0:0] dinb;

wire gw gnd;

assign gw_gnd = 1'b0;

DP bram_dp_0 (

.DOA(douta[0]),

.DOB (doutb[0])

.OCEA (ocea),

.CEA(cea),

.RESETA(reseta),

.WREA(wrea)

.OCEB (oceb)

.RESETB (resetb),

.WREB (wreb)

.BLKSEL({gw_gnd,gw_gnd,gw_gnd}),

.ADA((gw_gnd,gw_gnd,gw_gnd,gw_gnd,gw_gnd,gw_gnd,gw_gnd,gw_gnd,gw_gnd,gw_gnd,gw_gnd,gw_gnd,gw_gnd,gw_gnd,ada[0])),

.ADB((gw gnd,gw

.DIB(dinb[0])

defparam bram_dp_0.READ_MODE0 = 1'b0;

defparam bram_dp_0.READ_MODE1 = 1'b0;

defparam bram_dp_0.WRITE_MODE0 = 2'b00;

defparam bram_dp_0.WRITE_MODE1 = 2'b00;

defparam bram_dp_0.BIT_WIDTH_0 = 1;

defparam bram_dp_0.BIT_WIDTH_1 = 1;

defparam bram_dp_0.BIK_SEL = 3'b000;

defparam bram_dp_0.RESET_MODE = "SYNC";

endmodule //Gowin DP

```

#### 用户例化该 IP 设计文件的模板文件

考虑用户的实际应用, IP Core Generator 工具在产生例化 DP 设计文件的同时, 亦提供用户例化该 IP 设计文件的模板文件, 如图 3-20 所示。

#### 图 3-20 用户例化该 IP 设计文件的模板文件

```

Gowin DP your instance name (

.douta(douta_o), //output [0:0] douta

.doutb(doutb_o), //output [0:0] doutb

.clka(clka_i), //input clka

.ocea(ocea_i), //input ocea

.cea(cea i), //input cea

.reseta(reseta_i), //input reseta

.wrea(wrea_i), //input wrea

.clkb(clkb_i), //input clkb

.oceb(oceb_i), //input oceb

.ceb(ceb i), //input ceb

.resetb(resetb_i), //input resetb

.wreb(wreb_i), //input wreb

.ada(ada i), //input [9:0] ada

.dina(dina_i), //input [0:0] dina

.adb(adb i), //input [9:0] adb

.dinb(dinb i) //input [0:0] dinb

) :

```

SUG284-1.9 18(155)

#### IP Core Generator 生成 DP 示例

如用户需产生 8192X2、Bypass 读模式、Write-Through 写模式、同步复位模式下的 DP IP,以 device 选择 GW1N-LV4LQ144C6/I5 为例,界面配置如图 3-21 所示,初始化文件可根据用户需要在 Initialization 窗口配置,单击"OK",产生用户所需的 DP IP 设计文件。

产生的 DP IP 设计文件所在目录即为配置界面中"Create In"设置路径。

#### 图 3-21 DP IP Customization 设置

#### 3.1.3 DPB

DPB 是双端口工作模式,可通过 DPB、DPBX9 两种高云器件实现, DPB 是 DP 的优化版,端口 A 和端口 B 独立支持片选信号(BLKSELA 和 BLKSELB),推荐用户优先使用 DPB。在 IP Core Generator 界面中,单击"DPB",界面右侧会显示 DPB 的相关信息概要,如图 3-22 所示。

SUG284-1.9 19(155)

#### 图 3-22 DPB 的信息概要

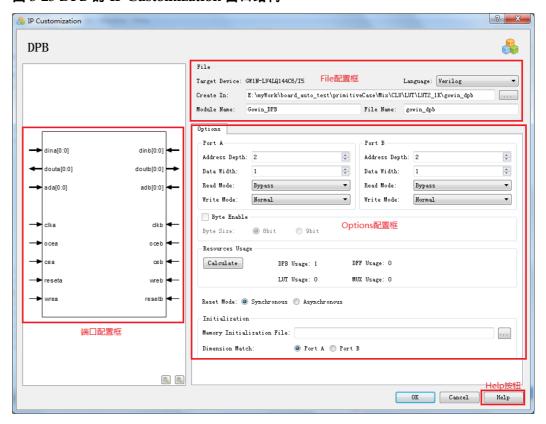

在 IP Core Generator 界面中,双击"DPB",弹出 DPB 的 IP Customization 窗口。该窗口包括"File"配置框、"Options"配置框、端口配置框图和帮助按钮"Help",如图 3-23 所示。

#### 图 3-23 DPB 的 IP Customization 窗口结构

1. File 配置框 File 配置框用于配置产生 DPB 实例化文件的相关信息,如图 3-23 中标注

SUG284-1.9 20(155)

的 File 配置框所示。

DPB 的 File 配置框的使用和 SP 模块类似, 具体请参考 <u>3.1</u>Block Memory > 3.1.1SP 的 File 配置框。

#### 2. Options 配置框

Options 配置框用于用户自定义双端口模式存储器的配置信息,如图 3-23 中 "Options 配置框"所示。

DPB 的 Options 配置框的使用和 SP 模块类似,具体请参考 <u>3.1 Block</u> Memory>3.1.1SP <u>中</u>的 Options 配置框。

配置 DPB 时,需注意的事项与配置 DP 时需要注意的事项一致,请参考 3.1 Block Memory > 3.1.2 DP 中的 Options 配置框。

#### 3. 端口配置框图

- 配置框图显示当前 IP Core 的配置结果示例框图,输入输出端口的位宽根据 Options 配置实时更新,如图 3-23 中标注的"端口配置框"所示:

- Options 配置中的 Port A 和 Port B 的地址深度 Address Depth 配置 影响 ada 和 adb 的位宽,数据位宽 Data Width 配置影响 dina/douta 和 dinb/doutb 的位宽。

#### 4. Help 按钮

单击"Help",显示 IP Core 的配置信息的页面,如图 3-24 所示。

#### 图 3-24 Help 信息

#### **DPB**

| Information |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type:       | DPB                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Vendor:     | GOWIN Semiconductor                                                                                                                                                                                                                                                                                                                                                                                                                |

| Summary:    | B-SRAM can be configured as Dual-port Block SRAM(DPB). In this mode, the design support different data widths. Both port A and port B can read or write. It can be initialized by a memory initialization file. And also, it supports five working modes including two read modes (bypass and pipeline), and three write modes (normal, write-through, and read-before-write). The byte enable function is supported in this mode. |

|             | In DPB mode, the primitives DPB and DPX9B can be used. The primitives support multiple data widths and address depth (Depth x Width): DPB16Kx1, 8Kx2, 4Kx4, 2Kx8, 1Kx16; DPX9B2Kx9, 1Kx18.                                                                                                                                                                                                                                         |

|             | NOTE: The value of Depth*Width of port A must be the same as that of port B.                                                                                                                                                                                                                                                                                                                                                       |

|             | DPB is an optimized version of DP, and its port A and port B independently support block selection signal (BLKSELA and BLKSELB). It is recommended to use this module first.                                                                                                                                                                                                                                                       |

#### Options

| Option         | Description                                                                                                                                 |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Port A         | Address Depth - Set the size of the address depth.                                                                                          |

|                | Data Width - Set the size of the Data width.                                                                                                |

|                | Read Mode - Set whether the read mode is bypass mode or pipeline mode.                                                                      |

|                | Write Mode - Set the write mode as normal mode, write-through mode or read-before-write mode.                                               |

| Port B         | Address Depth - Set the size of the address depth.                                                                                          |

|                | Data Width - Set the size of the Data width.                                                                                                |

|                | Read Mode - Set whether the read mode is bypass mode or pipeline mode.                                                                      |

|                | Write Mode - Set the write mode as normal mode, write-through mode or read-before-write mode.                                               |

| Byte Enable    | Byte Enable - Set whether to use byte enable function or not.                                                                               |

|                | Byte Size - Set whether the byte size is 8bit or 9bit if the byte enable checkbox selected.                                                 |

|                | Note:(1) If Width<=8, byte enable function is invalid; (2) If Width=9, only 8 bit is valid; (3) If Width>9, both 8 bit and 9 bit are valid. |

| Resource Usage | Calculate - Calculate the resource usage in the design and display results below.                                                           |

|                | DPB Usage - Display the number of DPB used.                                                                                                 |

|                | DFF Usage - Display the number of DFF used.                                                                                                 |

|                | LUT Usage - Display the number of LUT used.                                                                                                 |

Help 页面包括当前 IP Core 的概要介绍,以及 Options 各项配置的简要说明。

SUG284-1.9 21(155)

#### IP 生成文件

如图 3-25 所示, DPB 的"IP Customization"窗口配置完成后,单击"OK", 产生以配置文件 "File Name" 命名的三个文件:

- 例化高云原语 DPB 设计文件 "gowin\_dpb.v";

- 用户例化该 IP 设计文件的模板文件 "gowin\_dpb\_tmp.v";

- 例化原语 DP 的配置文件 "gowin\_dpb.ipc"。

如配置中选择的语言是 VHDL,产生的前两个文件名后缀为.vhd。下述以 verilog 语言为例介绍产生的文件。

#### 图 3-25 配置的 IP Customization

#### 例化 DPB 设计文件

例化 DPB 设计文件为完整的 verilog 模块,模块中根据"IP Customization"中的 DPB 配置,产生实例化的 DPB,如图 3-26 所示。

SUG284-1.9 22(155)

#### 图 3-26 例化 DPB 设计文件

```

module Gowin_DPB (douta, doutb, clka, ocea, cea, reseta, wrea, clkb, oceb, ceb, resetb, wreb, ada, dina, adb, dinb);

output [0:0] doutb;

input clka;

input ocea;

input cea;

input reseta;

input clkb;

input oceb;

input ceb;

input resetb;

input wreb;

input [9:0] ada;

input [0:0] dina;

input [9:0] adb;

input [0:0] dinb;

wire gw gnd;

assign gw_gnd = 1'b0;

DPB dpb_inst_0 (

.DOA(douta[0]),

.DOB(doutb[0]),

.CLKA(clka),

.OCEA (ocea),

.CEA(cea),

.RESETA(reseta),

.WREA(wrea),

.CLKB(clkb),

.OCEB (oceb)

.CEB (ceb),

.RESETB (resetb),

.WREB (wreb) ,

.BLKSELA({gw_gnd,gw_gnd,gw_gnd}),

.BLKSELB({gw_gnd,gw_gnd,gw_gnd}),

.ADA((gw_gnd,gw_gnd,gw_gnd,ada[9:0])),

.DIA(dina[0]),

.ADB([gw_gnd,gw_gnd,gw_gnd,adb[9:0]}),

.DIB(dinb[0])

defparam dpb_inst_0.READ_MODE0 = 1'b0;

defparam dpb_inst_0.READ_MODE1 = 1'b0;

defparam dpb_inst_0.WRITE_MODE0 = 2'b00;

defparam dpb_inst_0.WRITE_MODE1 = 2'b00;

defparam dpb_inst_0.BIT_WIDTH_0 = 1;

defparam dpb_inst_0.BIT_WIDTH_1 = 1;

defparam dpb_inst_0.BLK_SEL_0 = 3'b000;

defparam dpb_inst_0.BLK_SEL_1 = 3'b000;

defparam dpb_inst_0.RESET_MODE = "SYNC";

endmodule //Gowin_DPB

```

#### 用户例化该 IP 设计文件的模板文件

考虑用户的实际应用,IP Core Generator 工具在产生例化 DPB 设计文件的同时,亦提供用户例化该 IP 设计文件的模板文件,如图 3-27 所示。

SUG284-1.9 23(155)

#### 图 3-27 用户例化该 IP 设计文件的模板文件

```

Gowin DPB your instance name (

.douta(douta o), //output [0:0] douta

.doutb (doutb o), //output [0:0] doutb

.clka(clka i), //input clka

.ocea(ocea i), //input ocea

.cea(cea_i), //input cea

.reseta(reseta_i), //input reseta

.wrea(wrea_i), //input wrea

.clkb(clkb_i), //input clkb

.oceb(oceb_i), //input oceb

.ceb(ceb_i), //input ceb

.resetb(resetb_i), //input resetb

.wreb(wreb_i), //input wreb

.ada(ada i), //input [9:0] ada

.dina(dina_i), //input [0:0] dina

.adb(adb_i), //input [9:0] adb

.dinb(dinb i) //input [0:0] dinb

);

```

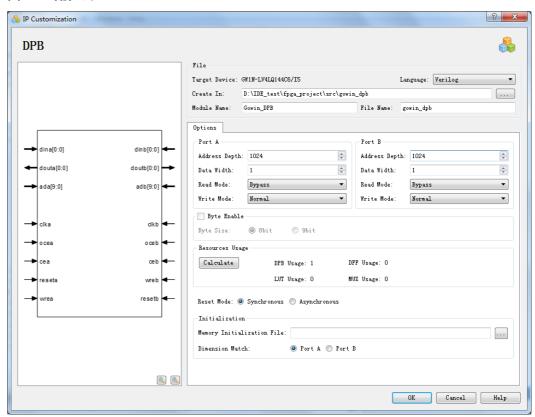

#### IP Core Generator 生成 DPB 示例

如用户需产生 8192X2、Bypass 读模式、Write-Through 写模式、同步复位模式下的 DPB IP,以 device 选择 GW1N-LV4LQ144C6/I5 为例,界面配置如图 3-28 所示,初始化文件可根据用户需要在 Initialization 窗口配置,单击"OK",产生用户所需的 DPB IP 设计文件。

产生的 DPB IP 设计文件所在目录即为配置界面中"Create In"设置路径。

#### 图 3-28 DPB IP Customization 设置

SUG284-1.9 24(155)

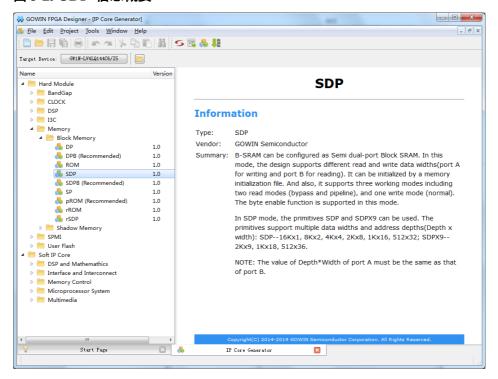

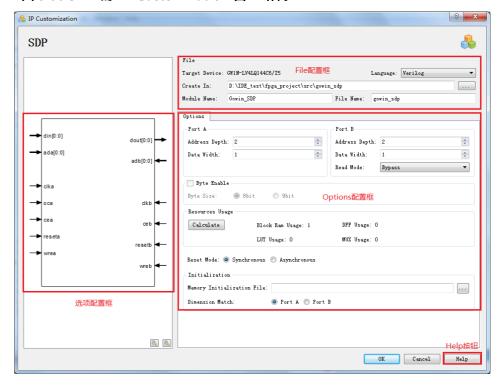

# 3.1.4 SDP

SDP 是半双端口工作模式,可通过 SDP、SDPX9 两种高云器件实现,BSRAM 的最大存储容量根据芯片型号的不同而不同。在 IP Core Generator 界面中,单击"SDP",界面右侧会显示 SDP 的相关信息概要,如图 3-29 所示。

# 图 3-29 SDP 信息概要

在 IP Core Generator 界面中,双击 "SDP",弹出 "IP Customization" 窗口。该窗口包括"File"配置框、"Options"配置框、端口配置框图和帮助按钮"Help",如图 3-30 所示。

SUG284-1.9 25(155)

#### 图 3-30 SDP 的 IP Customization 窗口结构

#### 1. File 配置框

File 配置框用于配置产生 SDP 实例化文件的相关信息,标注的"File 配置框"如图 3-30 所示。

SDP的 File 配置框的使用和 SP 模块的类似,请参考 <u>3.1</u>Block Memory > 3.1.1SP 中 File 配置框介绍。

#### 2. Options 配置框

Options 配置框用于用户自定义半双端口模式存储器的配置信息,如图 3-30 标注的 "Options 配置框"所示。

SDP 的 Options 配置框的使用和 SP 模块的类似,请参考 <u>3.1</u>Block Memory > <u>3.1.1</u>SP 中 Options 配置框。

#### 注!

- SDP 只支持 PortA 写操作,PortB 读操作; Options 配置框中 Read Mode 配置框可配置 PortB 的 Read Mode 为 Bypass 和 Pipeline;

- Options 配置框中可独立配置 SDP 的 Port A 和 Port B 的地址深度、数据宽度;

- SDP的 Port A和 Port B是对同一块 memory进行读写, 所以 Port A和 Port B的 Address Depth\*Data Width 的结果须相同, 否则会报出如如图 3-31 所示的 Error 提示信息;

- Options 配置中的初始化文件(Memory initialization File)中的数据宽度应和 Dimension Match 选择的 Port 数据宽度一致,否则产生的 SDP 实例 Init 值默认初始化为 0,并且 会在 Output 窗口显示如下信息: Error (MG2105): Initial values' width is unequal to user's width.

SUG284-1.9 26(155)

# 图 3-31 SDP 配置 Error 信息

#### 3. 端口配置框图

- 配置框图显示当前 IP Core 的配置结果示例框图,输入输出端口的位 宽根据 Options 配置实时更新,如图 3-30 中标注的配置框图所示;

- Options 配置中的 Port A 的地址深度 Address Depth 配置影响 ada 的位宽,数据位宽 Data Width 配置影响 din 的位宽; PortB 的地址深度 Address Depth 配置影响 adb 的位宽,数据位宽 Data Width 配置影响 dout 的位宽。

- 4. Help 按钮

单击"Help",显示 IP Core 的配置信息页面,如图 3-32 所示。

# 图 3-32 Help 信息

#### **SDP**

| Information |                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type:       | SDP                                                                                                                                                                                                                                                                                                                                                                                                         |

| Vendor:     | GOWIN Semiconductor                                                                                                                                                                                                                                                                                                                                                                                         |

| Summary:    | B-SRAM can be configured as Semi dual-port Block SRAM. In this mode, the design supports different read and write data widths(port A for writing and port B for reading). It can be initialized by a memory initialization file. And also, it supports three working modes including two read modes (bypass and pipeline), and one write mode (normal). The byte enable function is supported in this mode. |

|             | In SDP mode, the primitives SDP and SDPX9 can be used. The primitives support multiple data widths and address depths(Depth x width): SDP16Kx1, 8Kx2, 4Kx4, 2Kx8, 1Kx16, 512x32; SDPX92Kx9, 1Kx18, 512x36.                                                                                                                                                                                                  |

|             | NOTE: The value of Depth*Width of port A must be the same as that of port B.                                                                                                                                                                                                                                                                                                                                |

# Options

| Option         | Description                                                                                                                                                                                      |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port A         | Address Depth - Set the size of the address depth.                                                                                                                                               |

| Port A         | Data Width - Set the size of the Data width.                                                                                                                                                     |

|                | Address Depth - Set the size of the address depth.                                                                                                                                               |

| Port B         | Data Width - Set the size of the Data width.                                                                                                                                                     |

|                | Read Mode - Set whether the read mode is bypass mode or pipeline mode.                                                                                                                           |

|                | Byte Enable - Set whether to use byte enable function or not.                                                                                                                                    |

| Byte Enable    | Byte Size - Set whether the byte size is 8bit or 9bit if the byte enable checkbox selected.                                                                                                      |

|                | Note: Assume that the data width is represented by Width. (1) If Width<=8, byte enable function is invalid; (2) If Width=9, only 8 bit is valid; (3) If Width>9, both 8 bit and 9 bit are valid. |

|                | Calculate - Calculate the resource usage in the design and display results below.                                                                                                                |

|                | Block Ram Usage - Display the number of Block Ram used.                                                                                                                                          |

| Resource Usage | DFF Usage - Display the number of DFF used.                                                                                                                                                      |

|                | LUT Usage - Display the number of LUT used.                                                                                                                                                      |

|                | MUX Usage - Display the number of MUX used.                                                                                                                                                      |

| Reset Mode     | Reset Mode - Set whether the reset mode is synchronous mode or asynchronous mode.                                                                                                                |

| Initialization | Memory Initialization File - Set the memory initialization file (.mi) path.                                                                                                                      |

| THURIZAUUT     | Dimension Match - Set which port's dimensions the memory initialization file should conform to.                                                                                                  |

Help 页面包括当前 IP Core 的概要介绍,以及 Options 各项配置的简要说明。

SUG284-1.9 27(155)

## IP 生成文件

如图 3-33 所示, SDP 的"IP Customization"窗口配置完成后,单击"OK",产生以配置文件"File Name"命名的三个文件:

- 例化高云原语 SDP 设计文件 "gowin\_sdp.v";

- 用户例化该 IP 设计文件的模板文件 "gowin sdp tmp.v";

- 例化原语 SDP 的配置文件 "gowin\_sdp.ipc"。

如配置中选择的语言是 VHDL,则产生的前两个文件名后缀为.vhd。下述以 verilog 语言为例介绍产生的文件。

#### 图 3-33 配置的 IP Customization

# 例化 SDP 设计文件

例化 SDP 设计文件为完整的 verilog 模块,模块中根据"IP Customization"中的 SDP 配置,产生实例化的 SDP,如图 3-34 所示。

## 注!

产生的实例 SDP 的 din、dout 的数据宽度和"IP Customization"中的 SDP 配置一致。

SUG284-1.9 28(155)

#### 图 3-34 例化 SDP 设计文件

```

module Gowin_SDP (dout, clka, cea, reseta, wrea, clkb, ceb, resetb, wreb, oce, ada, din, adb);

input clka;

input cea;

input reseta;

input wrea;

input clkb;

input ceb;

input resetb;

input wreb:

input oce;

input [7:0] ada;

input [3:0] din;

input [7:0] adb;

wire gw gnd;

assign gw gnd = 1'b0;

SDP bram_sdp_0 (

.DO(dout[3:0])

.CLKA(clka),

.CEA(cea),

.RESETA (reseta).

.WREA(wrea),

.CLKB(clkb),

.CEB (ceb),

.RESETB (resetb),

.WREB (wreb) ,

.OCE (oce),

.BLKSEL({gw_gnd,gw_gnd,gw_gnd}),

.ADA({gw_gnd,gw_gnd,gw_gnd,gw_gnd,ada[7:0],gw_gnd,gw_gnd}),

.DI (din[3:01)

. \verb|ADB| (\{gw\_gnd, gw\_gnd, gw\_gnd, gw\_gnd, adb[7:0], gw\_gnd, gw\_gnd\})|\\

defparam bram_sdp_0.READ_MODE = 1'b0;

defparam bram_sdp_0.BIT_WIDTH_0 = 4;

defparam bram_sdp_0.BIT_WIDTH_1 = 4;

defparam bram_sdp_0.BLK_SEL = 3*b000;

defparam bram sdp 0.RESET MODE = "SYNC";

endmodule //Gowin SDP

```

#### 用户例化该 IP 设计文件的模板文件

考虑用户的实际应用,IP Core Generator 工具在产生例化 SDP 设计文件的同时,亦提供用户例化该 IP 设计文件的模板文件,如图 3-35 所示。

# 图 3-35 用户例化该 IP 设计文件的模板文件

```

Gowin_SDP your_instance_name(

.dout(dout_o), //output [3:0] dout

.clka(clka_i), //input clka

.cea(cea_i), //input cea

.reseta(reseta_i), //input reseta

.wrea(wrea_i), //input wrea

.clkb(clkb_i), //input clkb

.ceb(ceb_i), //input ceb

.resetb(resetb_i), //input resetb

.wreb(wreb_i), //input wreb

.oce(oce_i), //input oce

.ada(ada_i), //input [7:0] ada

.din(din_i), //input [3:0] din

.adb(adb_i) //input [7:0] adb

);

```

#### IP Core Generator 生成 SDP 示例

如用户需产生 512X32、Bypass 读模式、同步复位模式下的 SDP IP,

SUG284-1.9 29(155)

以 device 选择 GW1N-LV4LQ144C6/I5 为例,界面配置如图 3-36 所示,初始化文件可根据用户需要在 Initialization 窗口配置,单击"OK",产生用户所需的 SDP IP 设计文件。

产生的 SDP IP 设计文件所在目录即为配置界面中"Create In"设置路径。

# 图 3-36 SDP 的 IP Customization 设置

# 3.1.5 SDPB

SDPB 半双端口工作模式,可通过 SDPB、SDPBX9 两种高云器件实现, SDPB 是 SDP 的优化版本,端口 A 和端口 B 独立支持片选信号 (BLKSELA 和 BLKSELB),推荐用户优先使用 SDPB。在 IP Core Generator 界面中,单击"SDPB",界面右侧会显示 SDPB 的相关信息概要,如图 3-37 所示。

SUG284-1.9 30(155)

# 图 3-37 SDPB 的信息概要

在 IP Core Generator 界面中,双击"SDPB",弹出"IP Customization" 窗口。该窗口包括"File"配置框、"Options"配置框、端口配置框图和帮助按钮"Help",如图 3-38 所示。

SUG284-1.9 31(155)

#### 图 3-38 SDPB 的 IP Customization 窗口结构

#### 1. File 配置框

File 配置框用于配置产生 SDPB 实例化文件的相关信息,如图 3-38 标注的 File 配置框所示。

SDPB的 File 配置框的使用和 SP 模块的类似,请参考 <u>3.1</u>Block Memory > <u>3.1.1</u>SP 中 File 配置框介绍。

#### 2. Options 配置框

Options 配置框用于用户自定义半双端口模式存储器的配置信息,如图 3-38 中标注的 Options 配置框所示。

SDPB 的 Options 配置框的使用和 SP 模块的类似,请参考 <u>3.1</u>Block Memory > <u>3.1.1</u>SP 中 Options 配置框。

#### 注!

SDPB 需要注意的事项与 SDP 一致,请参考  $\underline{3.1}$ Block Memory >  $\underline{3.1.4}$  SDP 中 Options 配 置框

# 3. 端口配置框图

- 配置框图显示当前 IP Core 的配置结果示例框图,输入输出端口的位宽根据 Options 配置实时更新,如图 3-38 中标注的配置框图所示;

- Options 配置中的 Port A 的地址深度 Address Depth 配置影响 ada 的位宽,数据位宽 Data Width 配置影响 din 的位宽;PortB 的地址深度 Address Depth 配置影响 adb 的位宽,数据位宽 Data Width 配置影响 dout 的位宽。

# 4. Help 按钮

单击 "Help",显示 IP Core 的配置信息页面,如图 3-39 所示。

SUG284-1.9 32(155)

## 图 3-39 Help 信息

#### **SDPB**

#### **Information**

| Type:    | SDPB                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vendor:  | GOWIN Semiconductor                                                                                                                                                                                                                                                                                                                                                                                               |

|          | B-SRAM can be configured as Semi dual-port Block SRAM(SDPB). In this mode, the design supports different read and write data widths(port A for writing and port B for reading). It can be initialized by a memory initialization file. And also, it supports three working modes including two read modes (bypass and pipeline), and one write mode (normal). The byte enable function is supported in this mode. |

| Summary: | In SDPB mode, the primitives SDPB and SDPX9B can be used. The primitives support multiple data widths and address depths(Depth x width): SDPB16Kx1, 8Kx2, 4Kx4, 2Kx8, 1Kx16, 512x32; SDPX9B2Kx9, 1Kx18, 512x36.                                                                                                                                                                                                   |

|          | NOTE: The value of Depth*Width of port A must be the same as that of port B.                                                                                                                                                                                                                                                                                                                                      |

|          | SDPB is an optimized version of SDP, and its port A and port B independently support block selection signal (BLKSELA and BLKSELB). It is recommended to use this module first.                                                                                                                                                                                                                                    |

#### Options

| Option         | Description                                                                                                                                 |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| D-+ A          | Address Depth - Set the size of the address depth.                                                                                          |

| Port A         | Data Width - Set the size of the Data width.                                                                                                |

|                | Address Depth - Set the size of the address depth.                                                                                          |

| Port B         | Data Width - Set the size of the Data width.                                                                                                |

|                | Read Mode - Set whether the read mode is bypass mode or pipeline mode.                                                                      |

|                | Byte Enable - Set whether to use byte enable function or not.                                                                               |

| Byte Enable    | Byte Size - Set whether the byte size is 8bit or 9bit if the byte enable checkbox selected.                                                 |

| -,             | Note:(1) If Width<=8, byte enable function is invalid; (2) If Width=9, only 8 bit is valid; (3) If Width>9, both 8 bit and 9 bit are valid. |

|                | Calculate - Calculate the resource usage in the design and display results below.                                                           |

|                | SDPB Usage - Display the number of Block Ram used.                                                                                          |

| Resource Usage | DFF Usage - Display the number of DFF used.                                                                                                 |

|                | LUT Usage - Display the number of LUT used.                                                                                                 |

|                | MUX Usage - Display the number of MUX used.                                                                                                 |

| Reset Mode     | Reset Mode - Set whether the reset mode is synchronous mode or asynchronous mode.                                                           |

| Initialization | Memory Initialization File - Set the memory initialization file (.mi) path.                                                                 |

| micialization  | Dimension Match - Set which port's dimensions the memory initialization file should conform to.                                             |

Help 页面包括当前 IP Core 的概要介绍,以及 Options 各项配置的简要说明。

#### IP 生成文件

如图 3-40 所示,SDPB 的"IP Customization"窗口配置完成后,单击"OK",产生以配置文件"File Name"命名的三个文件:

- 例化高云原语 SDPB 设计文件 "gowin\_sdpb.v";

- 用户例化该 IP 设计文件的模板文件 "gowin\_sdpb\_tmp.v";

- 例化原语 SDPB 的配置文件 "gowin\_sdpb.ipc"。

如配置中选择的语言是 VHDL,则产生的前两个文件名后缀为.vhd。下述以 verilog 语言为例介绍产生的文件。

SUG284-1.9 33(155)

# 图 3-40 配置的 IP Customization

# 例化 SDPB 设计文件

例化 SDPB 设计文件为完整的 verilog 模块,模块中根据"IP Customization"中的 SDPB 配置,产生实例化的 SDPB,如图 3-41 所示。 注!

产生的实例 SDPB 的 din、dout 的数据宽度和 "IP Customization"中的 SDPB 配置一致。

SUG284-1.9 34(155)

#### 图 3-41 例化 SDPB 设计文件

```

module Gowin_SDPB (dout, clka, cea, reseta, clkb, ceb, resetb, oce, ada, din, adb);

output [3:0] dout;

input clka:

input cea;

input reseta;

input clkb;

input ceb;

input resetb;

input oce;

input [7:0] ada;

input [3:0] din;

input [7:0] adb;

wire gw gnd;

assign gw gnd = 1'b0;

SDPB sdpb inst 0 (

.DO(dout[3:0]),

.CLKA(clka),

.CEA(cea),

.RESETA (reseta),

.CLKB(clkb),

.CEB (ceb),

.RESETB(resetb),

.OCE (oce),

.BLKSELA({gw_gnd,gw_gnd,gw_gnd}),

.BLKSELB({gw gnd,gw gnd,gw gnd}),

.ADA((gw_gnd,gw_gnd,gw_gnd,gw_gnd,ada[7:0],gw_gnd,gw_gnd)),