# $Gowin Synthesis ^{\circledR}$

# 用户指南

SUG550-1.2,2020-03-03

#### 版权所有© 2020 广东高云半导体科技股份有限公司

未经本公司书面许可,任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部,并不得以任何形式传播。

#### 免责声明

本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止发言或其它方式授予任何知识产权许可。除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。高云半导体不承诺对这些文档进行适时的更新。

# 版本信息

| 日期         | 版本  | 说明                                     |  |

|------------|-----|----------------------------------------|--|

| 2019/08/02 | 1.0 | 初始版本。                                  |  |

| 2019/12/05 | 1.1 | 增加综合前后对象命名规则说明(适用于高云云源软件 1.9.3 及以后版本)。 |  |

| 2020/03/03 | 1.2 | 增加支持 VHDL 语法的设计(用于高云云源软件 1.9.5 及以后版本)。 |  |

i

# 目录

| 目:         | 录                                                       | i        |

|------------|---------------------------------------------------------|----------|

| 图          | 目录                                                      | iii      |

| 表          | 目录                                                      | . v      |

| 1 =        | 关于本手册                                                   | . 1      |

| • /        |                                                         |          |

|            | 1.1 手册内容                                                |          |

|            | 1.2 适用产品                                                |          |

|            | 1.3 相关文档                                                |          |

|            | 1.4 术语、缩略语                                              |          |

|            |                                                         |          |

| 2          | 既述                                                      | . 3      |

|            | 2.1 简介                                                  | 3        |

|            | 2.2 运行环境                                                | 3        |

|            | 2.3 软件版本                                                | . 3      |

| 3 (        | GowinSynthesis <sup>®</sup> 的使用方法介绍                     | . 4      |

|            | 3.1 GowinSynthesis <sup>®</sup> 输入输出                    | 4        |

|            | 3.2 使用 GowinSynthesis <sup>®</sup> 进行综合                 |          |

|            | 3.3 综合前后的对象命名规则                                         | 4        |

|            | 3.3.1 综合后网表文件命名                                         | 4        |

|            | 3.3.2 综合后网表 module 命名                                   | 5        |

|            | 3.3.3 综合后网表 Instance 命名                                 | 5        |

|            | 3.3.4 综合后网表连线命名                                         | . 5      |

| <b>4</b> } | 更件描述语言代码支持                                              | . 7      |

|            | 4.1 寄存器的硬件描述语言代码支持                                      |          |

|            | 4.1.1 寄存器特征介绍                                           |          |

|            | 4.1.2 寄存器相关的约束                                          |          |

|            | 4.1.3 寄存器代码示例                                           |          |

|            | <b>4.1.3</b> 可作输化剂列//////////////////////////////////// | . /      |

|            |                                                         |          |

|            | 4.2 RAM 的硬件描述语言代码支持                                     | 13       |

|            |                                                         | 13<br>13 |

|   | 4.2.3 RAM 推导相关的约束               | 13 |

|---|---------------------------------|----|

|   | 4.2.4 RAM 推导代码示例                | 14 |

|   | 4.3 DSP 的硬件描述语言代码支持             | 22 |

|   | 4.3.1 DSP 推导的基本功能介绍             | 22 |

|   | 4.3.2 DSP 特征介绍                  | 22 |

|   | 4.3.3 DSP 相关的约束                 | 23 |

|   | 4.3.4 DSP 推导代码示例                | 23 |

|   | 4.4 有限状态机的综合实现规则                | 30 |

|   | 4.4.1 有限状态机的综合规则                | 30 |

|   | 4.4.2 有限状态机代码示例                 | 30 |

| 5 | 综合约束支持                          | 33 |

|   | 5.1 syn_dspstyle                | 34 |

|   | 5.2 syn_ramstyle                |    |

|   | 5.3 syn_romstyle                | 37 |

|   | 5.4 syn_maxfan                  | 38 |

|   | 5.5 syn_encoding                | 40 |

|   | 5.6 syn_insert_pad              | 41 |

|   | 5.7 syn_netlist_hierarchy       | 41 |

|   | 5.8 syn_preserve                | 42 |

|   | 5.9 syn_keep                    | 44 |

|   | 5.10 syn_probe                  | 45 |

|   | 5.11 Translate_off/Translate_on | 46 |

|   | 5.12 Full_case                  |    |

|   | 5.13 syn_tlvds_io/syn_elvds_io  |    |

|   | 5.14 syn_looplimit              | 49 |

| 6 | Report 用户文档                     | 50 |

|   | 6.1 Synthesis Message           | 50 |

|   | 6.2 Design Settings             | 50 |

|   | 6.3 Resource                    | 51 |

|   | 6.4 Timing                      |    |

|   | 6.5 Message                     | 53 |

|   | 6.6 Summary                     | 53 |

| 7 | 层级资源信息文档                        | 54 |

# 图目录

| 图 3-1 综合前后对象名称对比                      | 6  |

|---------------------------------------|----|

| 图 4-1 示例 1 同步复位时钟触发器示意图               | 8  |

| 图 4-2 示例 2 同步置位且带有使能功能的触发器示意图         | 9  |

| 图 4-3 示例 3 异步复位且带有时钟使能功能的触发器示意图       | 10 |

| 图 4-4 示例 4 带有复位和高电平使能功能的锁存器示意图        | 10 |

| 图 4-5 示例 5 同步复位时钟触发器及逻辑电路示意图          | 11 |

| 图 4-6 示例 6 初始值为 0 的基本时钟触发器及逻辑电路示意图    | 12 |

| 图 4-7 示例 7 异步置位触发器示意图                 | 13 |

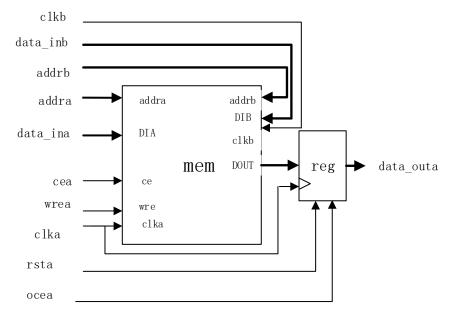

| 图 4-8 示例 1 RAM 电路图                    | 14 |

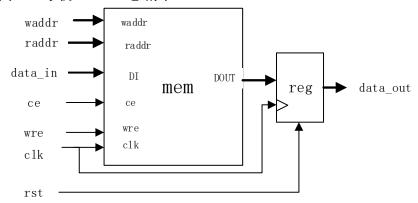

| 图 4-9 示例 2 RAM 电路图                    | 15 |

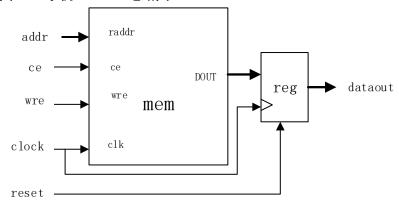

| 图 4-10 示例 3 RAM 电路图                   | 16 |

| 图 4-11 示例 4 RAM 电路图                   | 17 |

| 图 4-12 示例 5 RAM 电路图                   | 19 |

| 图 4-13 示例 6 RAM 电路图                   | 20 |

| 图 4-14 示例 7 ROM 电路图                   | 21 |

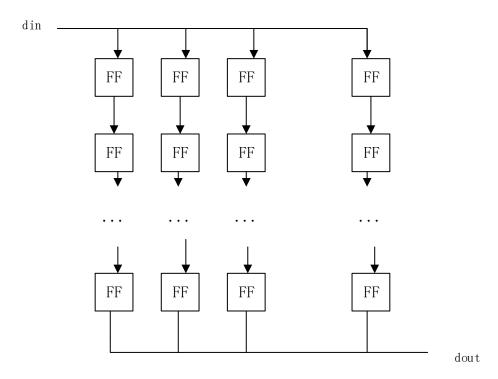

| 图 4-15 示例 8 RAM 电路图                   | 22 |

| 图 4-16 示例 1 DSP 电路图                   | 24 |

| 图 4-17 示例 2 DSP 电路图                   | 27 |

| 图 4-18 示例 3 DSP 电路图                   | 28 |

| 图 4-19 示例 4 DSP 电路图                   | 29 |

| 图 4-20 示例 5 DSP 电路图                   | 30 |

| 图 6-1 Synthesis Message               | 50 |

| 图 6-2 Design Settings                 | 50 |

| 图 6-3 Resource                        | 51 |

| 图 6-4 Timing                          | 52 |

| 图 6-5 Performance Summary             | 52 |

| 图 6-6 Detail Timing Paths Information | 52 |

| 图 6-7 连接关系、时延及扇出信息                    | 53 |

| 图 6-8 综合输出信息                          | 53 |

| 图 6-9 Sumr  | nmary                 | 53 |

|-------------|-----------------------|----|

| 图 7-1 Hiera | archy Module Resource | 54 |

SUG550-1.2 iv

# 表目录

| 表 1 | -1 术语: | 、缩略 | 各语 | 2 |

|-----|--------|-----|----|---|

|     |        |     |    |   |

SUG550-1.2 v

1 关于本手册 1.1 手册内容

# **1** 关于本手册

# 1.1 手册内容

本手册主要描述高云半导体综合工具(GowinSynthesis<sup>®</sup>)的功能及操作,旨在帮助用户快速熟悉 GowinSynthesis<sup>®</sup>软件的相关功能,指导用户设计,提高设计效率。本手册中的软件界面截图和支持的产品列表等信息均参考高云半导体云源设计软件 1.9.3Beta(1.9.5 版本增加 VHDL 支持)版本,因软件版本升级,部分信息可能会略有差异,具体以用户软件版本的信息为准。

# 1.2 适用产品

本手册中描述的信息适用于以下产品:

- GW1N 系列 FPGA 产品: GW1N-1, GW1N-1S, GW1N-2, GW1N-2B, GW1N-4, GW1N-4B, GW1N-6, GW1N-9

- GW1NR 系列 FPGA 产品: GW1NR-4, GW1NR-4B, GW1NR-9

- GW1NS 系列 FPGA 产品: GW1NS-2

- GW2A 系列 FPGA 产品: GW2A-55, GW2A-18

- GW2AR 系列 FPGA 产品: GW2AR-18

- GW1NZ 系列 FPGA 产品: GW1NZ-1

- GW1NSR 系列 FPGA 产品: GW1NSR-2

- GW1NSE 系列安全 FPGA 产品: GW1NSE-2C

- GW1NSER 系列安全 FPGA 产品: GW1NSER-4C

- GW1NRF 系列蓝牙 FPGA 产品: GW1NRF-4B

# 1.3 相关文档

通过登录高云半导体网站 <u>www.gowinsemi.com.cn</u> 可以下载、查看以下相关文档:

- DS100, GW1N 系列 FPGA 产品数据手册

- DS117, GW1NR 系列 FPGA 产品数据手册

- DS821, GW1NS 系列 FPGA 产品数据手册

SUG550-1.2 1(54)

1 关于本手册 1.4 术语、缩略语

- DS102, GW2A 系列 FPGA 产品数据手册

- DS226, GW2AR 系列 FPGA 产品数据手册

- <u>DS841</u>, GW1NZ 系列 FPGA 产品数据手册

- DS861, GW1NSR 系列 FPGA 产品数据手册

- DS871, GW1NSE 系列安全 FPGA 产品数据手册

- DS881, GW1NSER 系列安全 FPGA 产品数据手册

- DS891, GW1NRF 系列蓝牙 FPGA 产品数据手册

# 1.4 术语、缩略语

本手册中的相关术语、缩略语及相关释义请参见表 1-1。

表 1-1 术语、缩略语

| 术语、缩略语 | 全称                            | 含义                                 |

|--------|-------------------------------|------------------------------------|

| FPGA   | Field Programmable Gate Array | 现场可编程门阵列                           |

| SSRAM  | Shadow SRAM                   | 分布式静态随机存储器                         |

| B-SRAM | Block SRAM                    | 块状静态随机存储器                          |

| DSP    | Digitial Signal Processing    | 数字信号处理                             |

| FSM    | Finite State Machine          | 有限状态机                              |

| GSC    | Gowin Synthesis Constraint    | GowinSynthesis <sup>®</sup> 综合约東文件 |

# 1.5 技术支持与反馈

高云半导体提供全方位技术支持,在使用过程中如有任何疑问或建议,可直接与公司联系:

网址: www.gowinsemi.com.cn

E-mail: support@gowinsemi.com

Tel: +86 755 8262 0391

SUG550-1.2 2(54)

2.1 简介

# 2 概述

# 2.1 简介

本手册是高云半导体 RTL 设计综合工具 GowinSynthesis<sup>®</sup>的用户使用说明。

GowinSynthesis<sup>®</sup>是高云半导体自主研发的综合工具,以工程文件为输入,支持 FSM、Register、Add/Sub 等设计的综合及高云器件原语 RAM/DSP 的综合,综合过程支持常见的属性约束,以满足不同应用条件下综合结果的要求。GowinSynthesis<sup>®</sup>生成基于高云器件原语库的综合后网表,可作为高云布局布线工具的输入文件。

# 2.2 运行环境

Windows: Win7/10 (64bit/32bit)

Linux:: CentOS6.8/7/7.3, Ubuntu (64bit/32bit)

# 2.3 软件版本

本手册适用的软件版本号: V1.9.3Beta 及以后版本

SUG550-1.2 3(54)

# 3 GowinSynthesis®的使用方法介绍

# 3.1 GowinSynthesis®输入输出

GowinSynthesis<sup>®</sup>以工程文件(.prj)格式读入用户 RTL 文件,工程文件由 Gowin 云源软件自动生成。GowinSynthesis<sup>®</sup>工程文件中除指定用户 RTL 文件外,同时还指定了综合器件信息、用户约束文件信息(综合属性约束文件或时序约束文件)、综合后网表文件(.vg)信息及部分综合选项,如综合项层模块(top module)指定、文件包含路径(include path)指定等。

# 3.2 使用 GowinSynthesis®进行综合

在云源软件的 Process 窗口右键单击 Synthesize,选择 Configuration > GowinSynthesis<sup>®</sup>,则可使用 GowinSynthesis<sup>®</sup>工具。Configurations 页面也可以指定 top module,设置 include path,选择支持语言版本,相关配置信息会写入工程文件。

在云源软件的 Process 窗口双击 Synthesize 执行综合,Output 窗口会输出综合执行过程中的信息。GowinSynthesis<sup>®</sup>综合后生成综合报告及门级网表文件,双击 Process 窗口中的 Synthesis Report 和 Netlist File 即可查看具体内容。

具体操作流程请参考文档 <u>SUG100</u>,Gowin 云源软件用户指南 > 5.4.3 Synthesis 章节。

# 3.3 综合前后的对象命名规则

为便于用户的验证与调试,GowinSynthesis<sup>®</sup>综合工具在整个综合过程中将最大程度的保留用户原始 RTL 设计信息,如用户设计中的 module 模块信息、Instance 例化名称信息、用户定义的 wire/reg 连线名称等。对必须要经过优化或转化重新生成的对象,这些对象的名称也将由用户定义的连线名称通过一些衍生规则来生成,具体规则如下:

## 3.3.1 综合后网表文件命名

- 1. 综合后网表文件名称取决于工程文件(\*.prj)中指定的输出网表的文件名称;

- 2. 若工程文件中未指定综合后网表名称,默认生成名称同工程文件名,

SUG550-1.2 4(54)

后缀为.vg 的综合后网表文件。

#### 3.3.2 综合后网表 module 命名

- 1. 综合后网表的 module 名称来源于原始 RTL 设计中例化该 module 的 module Instance 名称:

- 2. 当 module 名称需要层级表示时,斜线'/'将作为层级分隔符。

# 3.3.3 综合后网表 Instance 命名

- 1. 用户 RTL 设计中被例化的 Instance, 若该 Instance 在综合过程中不被优化,则在综合后网表中保持 Instance 名称不变:

- 2. 综合过程中生成的 Instance, Instance 名称来源于该 Instance 在用户原始 RTL 中所表示的功能设计块的外部输出信号名,若该功能设计块有多个输出信号,则该 Instance 名取决于第一个输出信号的名称;

- 3. 对综合过程中综合工具生成的 Instance, Instance 名组成除上述所述的信号名外,其后还有"\_insID"的后缀,其中 ID 为该 Instance 在综合过程中所拥有的唯一识别码:

- 4. 当 Instance 名称需要层级表示时,斜线'/'将作为层级分隔符。

#### 3.3.4 综合后网表连线命名

- 1. 用户在 RTL 设计中定义的 wire/reg 信号,若该信号在综合过程中未被优化,则综合后网表的相关模块仍将保留该信号名;

- 2. GowinSynthesis<sup>®</sup>的综合过程中,会针对某些 RTL 设计中的一整块功能设计模块进行置换或优化,综合后,网表中这些功能设计模块的输出信号的信号名会被保留,对模块内部的信号,将根据输出信号名称做衍化,具体为在原始信号名称基础上增加相关数字后缀(\_idx)来形成衍化后的信号名:

- 3. 当多位宽的信号(bus 格式)名作为衍生信号名,衍生出其他信号名或 Instance 名称时,该信号名称中的bus 位信息将以下划线加位信息("\_idx") 的形式被保留:

- 4. 当 Instance 名称需要层级表示时,斜线'/'将作为层级分隔符。

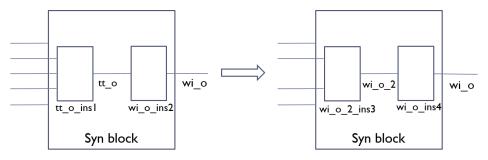

例如下图,为某个功能设计模块的综合前后名字改变过程,左边为综合前模块,模块外部信号名称为 wi\_o,内部模块之间有名为 tt\_o 的信号,驱动 tt\_o 信号的 Instance 为 tt\_o\_ins1。经过综合后,模块外部输出信号名称保留,仍为 wi\_o,内部模块之间的信号名改为由 wi\_o 衍生的信号 wi\_o\_2,相应的驱动 Instance 名称被改为 wi o 2 ins3。

SUG550-1.2 5(54)

#### 图 3-1 综合前后对象名称对比

SUG550-1.2 6(54)

# 4 硬件描述语言代码支持

# 4.1 寄存器的硬件描述语言代码支持

#### 4.1.1 寄存器特征介绍

Gowin 寄存器包含时钟触发器和锁存器。

#### 时钟触发器

Gowin 时钟触发器全部为 D 触发器。其复位/置位方式有两种:同步复位/置位和异步复位/置位。同步复位/置位指只有当时钟信号 CLK 的上升沿或下降沿到来时,且 set/reset 为高电平时,复位/置位才能完成;异步复位、置位指 set 和 reset 信号值的变化会激发过程进入到执行状态,只要 set/reset 由低电平变为高电平,复位、置位即可完成,不受时钟信号 CLK 的控制。

#### 锁存器

Gowin 锁存器触发方式含高电平触发及低电平触发。高电平触发是当控制信号为高电平时,锁存器允许数据端信号通过;低电平触发是当控制信号为低电平时,锁存器允许数据端信号通过。

# 4.1.2 寄存器相关的约束

用户可使用 preserve 属性对寄存器进行约束。当有此约束时,除了输出悬空的寄存器会被删除外,其他寄存器都会原样保留到综合结果中,详细请参考 5.8 章节。

# 4.1.3 寄存器代码示例

Gowin 的芯片设计同步复位时钟触发器的初始值仅可置为 0,同步置位时钟触发器的初始值仅可置为 1,故当用户在 RTL 中设置的同步时钟触发器的初始值与 Gowin 同步时钟触发器的初始值不同时,综合工具将优先依据 RTL 中的初始值,转换同步时钟触发器的类型。异步时钟触发器不做处理。具体转换策略是:

1. RTL 设计为同步复位时钟触发器,但指定初始值为 1 时,综合工具将其替换为同步置位的时钟触发器,将原同步复位信号添加相关逻辑以实现同步置位功能;

SUG550-1.2 7(54)

2. RTL 设计为同步置位时钟触发器,但指定初始值为 0 时,综合工具将其替换为普通触发器,并在原同步置位信号上添加相关逻辑作为触发器数据端输入。

#### 不指定触发器初始值

CLK 上升沿触发的触发器和 CLK 下降沿触发的触发器的区别仅仅是 CLK 触发方式不同,所以下面只列出能综合出 CLK 上升沿触发的触发器的示例。

```

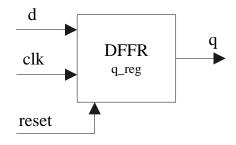

示例 1 可被综合为同步复位的时钟触发器

```

```

module top (q, d, clk, reset);

input d;

input clk;

input reset;

output q;

reg q_reg;

always @(posedge clk)begin

if(reset)

q_reg<=1'b0;

else

q_reg<=d;

end

assign q = q_reg;

endmodule

同步复位时钟触发器示意如图 4-1 所示:

```

#### 图 4-1 示例 1 同步复位时钟触发器示意图

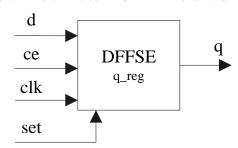

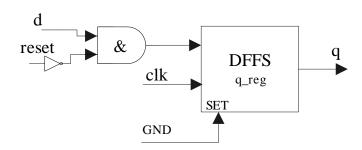

示例 2 可被综合为同步置位且带有时钟使能功能的触发器 *module top (q, d, clk, ce, set); input d; input clk;*

SUG550-1.2 8(54)

```

input ce;

input set;

output q;

reg q_reg;

always @(posedge clk)begin

if(set)

q_reg<=1'b1;

else if(ce)

q_reg<=d;

end

assign q = q_reg;

endmodule</pre>

```

同步置位且带有时钟使能功能的触发器示意如图 4-2 所示:

#### 图 4-2 示例 2 同步置位且带有使能功能的触发器示意图

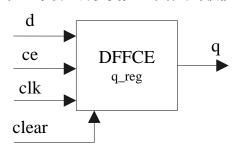

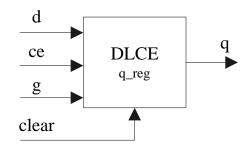

示例 3 可被综合为异步复位且带有时钟使能功能的触发器

module top (q, d, clk, ce, clear);

input d;

input clk;

input ce;

input clear;

output q;

reg q\_reg;

always @(posedge clk or posedge clear)begin

if(clear)

q\_reg<=1'b0;

else if(ce)

q\_reg<=d;

SUG550-1.2 9(54)

end

assign q = q\_reg;

endmodule

异步复位且带有时钟使能功能的触发器示意如图 4-3 所示:

#### 图 4-3 示例 3 异步复位且带有时钟使能功能的触发器示意图

示例 4 可被综合为带有复位和高电平使能功能的锁存器 module top(d,g,clear,q,ce); input d,g,clear,ce; output q; reg q\_reg;

if(clear)

q\_reg = 0;

else if(g && ce)

q\_reg = d;

always @(g or d or clear or ce) begin

end

$assign q = q\_reg;$

endmodule

带有复位和高电平使能功能的锁存器示意如图 4-4 所示:

#### 图 4-4 示例 4 带有复位和高电平使能功能的锁存器示意图

#### 指定触发器初始值

示例 5 为同步复位的时钟触发器,其初始值应为 0,但 RTL 中设置初始

SUG550-1.2 10(54)

值为 1,将被综合为初始值为 1 的同步置位的时钟触发器及用于实现同步复位功能的逻辑电路。

```

module top (q, d, clk, reset);

input d;

input clk;

input reset;

output q;

reg q_reg = 1'b1;

always @(posedge clk)begin

if(reset)

q_reg<=1'b0;

else

q_reg<=d;

end

assign q = q_reg;

endmodule

如上的同步复位时钟触发器示意如图 4-5 所示:

```

# 图 4-5 示例 5 同步复位时钟触发器及逻辑电路示意图

示例 6 为同步置位的时钟触发器, 其初始值应为 1, 但 RTL 中设置初始值为 0, 将被综合为初始值为 0 的普通时钟触发器及一个用于实现同步置位功能的逻辑电路。

```

module top (q, d, clk, set);

input d;

input clk;

input set;

output q;

reg q_reg = 1'b0;

always @(posedge clk)begin

```

SUG550-1.2 11(54)

```

if(set)

q_reg<=1'b1;

else

q_reg <= d;

end

assign q = q\_reg;

endmodule

```

如上初始值为0的基本时钟触发器及逻辑电路示意如图 4-6 所示:

#### 图 4-6 示例 6 初始值为 0 的基本时钟触发器及逻辑电路示意图

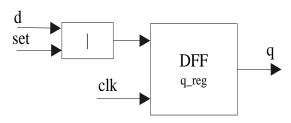

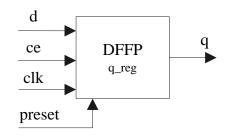

示例7为设置初值为1的异步置位触发器。

module top (q, d, clk, ce, preset); input d; input clk; input ce; input preset; output q;  $reg q\_reg = 1'b1;$ always @(posedge clk or posedge preset)begin *if(preset) q\_reg*<=1'*b*1; else if(ce)  $q_reg <= d;$ end  $assign q = q\_reg;$ endmodule

SUG550-1.2 12(54)

如上的异步置位触发器示意如图 4-7 所示:

#### 图 4-7 示例 7 异步置位触发器示意图

# 4.2 RAM 的硬件描述语言代码支持

#### 4.2.1 RAM 置换基本功能介绍

RAM 置换是 RTL 综合过程中将用户设计中的存储功能部分推导置换为块状静态随机存储器(B-SRAM)或分布式随机存储器(SSRAM)的过程。用户在设计 RTL 时既可以直接实例化 B-SRAM 或 SSRAM 原语,也可以写不依赖器件的 RTL 格式的存储器描述。对 RTL 格式的存储器块,

GowinSynthesis<sup>®</sup>将依据 RTL 描述, 将符合相应条件的 RTL 描述置换为相应的 RAM 模块。

当逻辑模块需要使用 B-SRAM 来实现时,需要满足以下原则:

- 1. 所有的输出寄存器有相同的控制信号;

- 2. RAM 必须为同步存储器,不可以有异步的控制信号相连,综合工具不支持异步 RAM:

- 3. 需要在读地址或者输出端连接寄存器。

## 4.2.2 RAM 特征介绍

#### **B-SRAM**

B-SRAM 的配置模式分为单端口模式,双端口模式,伪双端口模式,只读模式;读模式分为寄存器输出模式(pipeline)及旁路模式(bypass)两种;写模式支持普通模式(normal Mode)、通写模式(write-through Mode)及先读后写模式(read-before-write Mode)三种。

#### **SSRAM**

配置模式分为单端口模式,伪双端口模式,只读模式三种,SSRAM 不支持双端口模式。

#### 4.2.3 RAM 推导相关的约束

syn\_ramstyle 指定存储器的实现方式, syn\_romstyle 指定只读存储器的实现方式。

如果设计中指定要生成 SSRAM 或者 B-SRAM,请使用约束语句 ram\_style 或者 rom\_style 来控制。

约束语句具体使用方式请参考5.2、5.3章节。

SUG550-1.2 13(54)

#### 4.2.4 RAM 推导代码示例

按照 RAM 的不同特征举例如下:

示例 1 为 1 个写端口, 1 个读端口并且读写端口地址相同的存储器, 可以被综合为普通模式的单端口 B-SRAM。

```

module normal(data_out, data_in, addr, clk,ce, wre,rst);

output [7:0]data_out;

input [7:0]data_in;

input [7:0]addr;

input clk,wre,ce,rst;

reg [7:0] mem [127:0];

reg [7:0] data_out;

always@(posedge clk or posedge rst)

if(rst)

data\_out <= 0;

else

if(ce & !wre)

data_out <= mem[addr];</pre>

always @(posedge clk)

if (ce & wre)

mem[addr] <= data_in;</pre>

endmodule

```

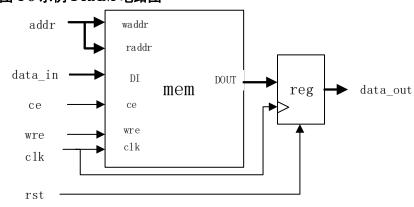

如上的单端口 B-SRAM 电路描述示意图如图 4-8 所示。

#### 图 4-8 示例 1 RAM 电路图

示例 2 为 1 个写端口, 1 个读端口并且读写端口地址相同的存储器, 当 wre 为 1 时,输入数据可以直接传输给输出,此案例被综合为通写模式的单端口 B-SRAM。

SUG550-1.2 14(54)

```

module wt11(data_out, data_in, addr, clk, wre,rst);

output [31:0]data_out;

input [31:0]data_in;

input [6:0]addr;

input clk,wre,rst;

reg [31:0] mem [127:0];

reg [31:0] data_out;

always@(posedge clk or posedge rst)

if(rst == 1)

data\_out <= 0;

else

if(wre == 1)

data_out <= data_in;</pre>

else

data_out <= mem[addr];</pre>

always @(posedge clk)

if (wre) mem[addr] <= data_in;</pre>

endmodule

如上的单端口 B-SRAM 电路描述示意图如图 4-9 所示。

```

#### 图 4-9 示例 2 RAM 电路图

示例 3 为 1 个写端口, 1 个读端口并且读写端口地址相同的存储器, 当 wre 为 1 时,输入数据写入存储器中,此案例被综合为先读后写模式的单端口 B-SRAM。

```

module wt11_2(data_out, data_in, addr, clk, wre,rst);

output [31:0]data_out;

input [31:0]data_in;

```

SUG550-1.2 15(54)

```

input [6:0]addr;

input clk,wre,rst;

reg [31:0] mem [127:0];

reg [31:0] data_out;

always@(posedge clk)

if(!wre)

data_out <= mem[addr];

else

data_out <= data_in;

always @(posedge clk)

if (!wre) mem[addr] <= data_in;

endmodule

如上的单端口 B-SRAM 电路描述示意图如图 4-10 所示。

```

#### 图 4-10 示例 3 RAM 电路图

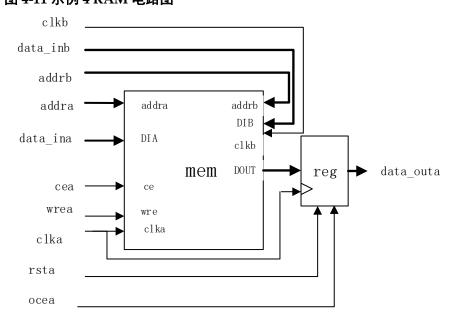

示例 4 为 2 个写端口, 1 个读端口的存储器,两个写端口一个有 WRE 信号,另外 1 个没有,读端口有吸收异步置位的寄存器,此案例被综合为 A端为先读后写模式,B端为普通模式的异步置位双端口 B-SRAM。

module read\_first\_01(data\_outa, data\_ina, addra, clka, rsta,cea, wrea,ocea,data\_outb, data\_inb, addrb, clkb, rstb,ceb, wreb,oceb);

output [17:0]data\_outa,data\_outb; input [17:0]data\_ina,data\_inb; input [6:0]addra,addrb; input clka, rsta,cea, wrea,ocea; input clkb, rstb,ceb, wreb,oceb; reg [17:0] mem [127:0]; reg [17:0] data\_outa,data\_outb;

SUG550-1.2 16(54)

```

reg [17:0] data_out_rega,data_out_regb;

always@(posedge clkb or posedge rstb)

if(rstb == 1)

data\_out\_regb <= 0;

else begin

if(ceb)

data_out_regb <= mem[addrb];</pre>

end

always@(posedge clkb or posedge rstb)

if(rstb == 1)

data_outb <= 0;

else if (oceb)

data_outb <= data_out_regb;</pre>

always @(posedge clkb)

if (ceb & wreb) mem[addrb] <= data_inb;</pre>

always @(posedge clka)

if (cea & wrea) mem[addra] <= data_ina;</pre>

endmodule

如上的双端口 B-SRAM 电路描述示意图如图 4-11 所示。

```

#### 图 4-11 示例 4 RAM 电路图

示例 5 为 2 个写端口,1 个读端口的存储器,一个写端口没有 wre 信号, 另外一个写端口有 wre 信号, 1 个读端口吸收异步置位的寄存器。此案例被

SUG550-1.2 17(54)

综合为写模式 A 端为普通模式, B 端为先读后写模式, 读模式为寄存器输出模式的异步置位双端口 B-SRAM。

```

module read first 02 1(data outa, data ina, addra, clka, rsta,cea,

wrea,ocea,data_outb, data_inb, addrb, clkb, rstb,ceb, wreb,oceb);

output [17:0]data_outa,data_outb;

input [17:0]data_ina,data_inb;

input [6:0]addra,addrb;

input clka, rsta,cea, wrea,ocea;

input clkb, rstb,ceb, wreb,oceb;

reg [17:0] mem [127:0];

reg [17:0] data_outa,data_outb;

reg [17:0] data_out_rega,data_out_regb;

always @(posedge clkb)

if (ceb & wreb) mem[addrb] <= data_inb;</pre>

always@(posedge clka or posedge rsta)

if(rsta == 1)

data\_out\_rega <= 0;

else begin

data_out_rega <= mem[addra];</pre>

end

always@(posedge clka or posedge rsta)

if(rsta == 1)

data_outa <= 0;

else if (ocea)

data_outa <= data_out_rega;</pre>

always @(posedge clka)

if (cea & wrea) mem[addra] <= data ina;

endmodule

如上的双端口 B-SRAM 电路描述示意图如图 4-12 所示。

```

SUG550-1.2 18(54)

#### 图 4-12 示例 5 RAM 电路图

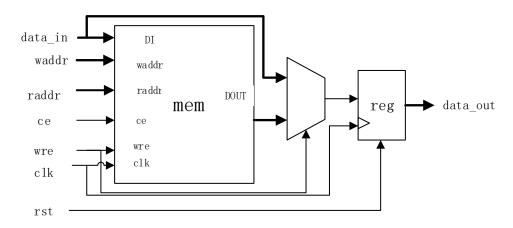

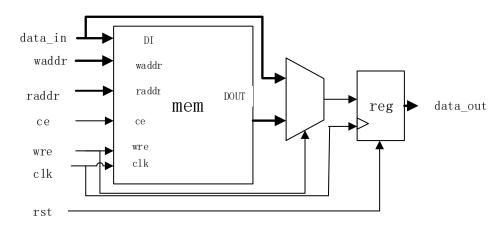

示例 6 为 1 个读端口, 1 个写端口且读写地址不同的存储器,被综合为写模式为普通模式,读模式为旁路模式的伪双端口 B-SRAM。

module read\_first\_wp\_pre\_1(data\_out, data\_in, waddr, raddr,clk, rst,ce,

wre);

SUG550-1.2 19(54)

#### 图 4-13 示例 6 RAM 电路图

示例 7 为具有初值的只有 1 个读端口的存储器,被综合为读模式为旁路模式的异步置位只读存储器。

```

module test_invce (clock,ce,wre,reset,addr,dataout) ;

input clock,ce,wre,reset;

input [5:0] addr;

output [7:0] dataout;

reg [7:0] dataout;

always @(posedge clock or posedge reset)

if(reset) begin

dataout \ll 0;

end else begin

if (!ce&(!wre)) begin

case (addr)

6'b000000: dataout <= 32'h87654321;

6'b000001: dataout <= 32'h18765432;

6'b000010: dataout <= 32'h21876543;

6'b111110: dataout <= 32'hdef89aba;

6'b111111: dataout <= 32'hef89abce;

default: dataout <= 32'hf89abcde;

endcase

end

end

endmodule

如上的只读存储器电路描述示意图如图 4-14 所示:

```

SUG550-1.2 20(54)

#### 图 4-14 示例 7 ROM 电路图

示例 8 为 shift register 模式的存储器,被综合为普通模式的伪双端口 B-SRAM。

```

module seqshift_bsram (clk, din, dout);

parameter SRL_WIDTH = 65;

parameter SRL_DEPTH = 4;

input clk;

input [SRL_WIDTH-1:0] din;

output [SRL_WIDTH-1:0] dout;

reg [SRL_WIDTH-1:0] regBank[SRL_DEPTH-1:0];

integer i;

always @(posedge clk) begin

for (i=SRL_DEPTH-1; i>0; i=i-1) begin

regBank[i] <= regBank[i-1];</pre>

end

regBank[0] <= din;

end

assign dout = regBank[SRL_DEPTH-1];

endmodule

如上的伪双端口 B-SRAM 电路描述示意图如图 4-15 所示。

```

SUG550-1.2 21(54)

#### 图 4-15 示例 8 RAM 电路图

注!

更多示例,请参见高云官网 GowinSynthesis<sup>®</sup>推导置换编码模板文档 "GowinSynthesis Inference Coding Template"。

# 4.3 DSP 的硬件描述语言代码支持

## 4.3.1 DSP 推导的基本功能介绍

DSP 推导是 RTL 综合过程中将用户设计中的乘法及部分加法推导置换为 DSP 的算法。用户在设计 RTL 时既可以实例化 DSP 也可以写不依赖器件的 RTL 格式的 DSP 描述,对 RTL 格式的乘加模块,GowinSynthesis<sup>®</sup>将依据 RTL 描述,将符合相应条件的 RTL 描述推导置换为相应的 DSP 模块。

DSP 模块具有乘法以及加法和寄存器的功能。当用户当前使用的器件不支持 DSP 模块时,GowinSynthesis<sup>®</sup>会使用逻辑电路来实现乘法器的功能。

#### 4.3.2 DSP 特征介绍

Gowin DSP 分为乘法器,乘加器,预加器。具有以下功能:

- 1. 支持输入符号位不同的乘法置换;

- 2. 支持同步或异步模式;

- 3. 支持乘法的链加;

- 4. 支持乘法的累加:

- 5. 支持预加功能;

- 6. 支持寄存器的吸收,包括输入寄存器,输出寄存器,旁路寄存器的吸收。

SUG550-1.2 22(54)

#### 4.3.3 DSP 相关的约束

syn\_dspstyle 用来控制具体对象或者全局范围的乘法器使用 DSP 还是逻辑电路实现。

syn\_perserve 用来保留寄存器,当 DSP 周围的寄存器有此属性时, DSP 不可以吸收此寄存器。

约束语句的具体使用方式请参考 5.1 、5.8 章节。

#### 4.3.4 DSP 推导代码示例

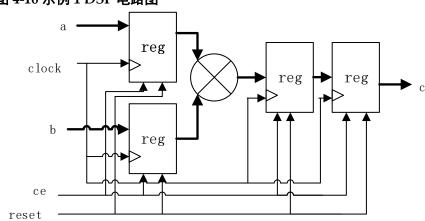

示例 1 可综合出带符号位的同步置位的乘法器,该乘法器的输入寄存器为 ina 和 inb,输出寄存器为 out\_reg,旁路寄存器为 pp\_reg。

```

module top(a,b,c,clock,reset,ce);

parameter\ a\_width = 18;

parameter b_width = 18;

parameter c width = 36;

input signed [a_width-1:0] a;

input signed [b_width-1:0] b;

input clock;

input reset;

input ce;

output signed [c_width-1:0] c;

reg signed [a_width-1:0] ina;

reg signed [b_width-1:0] inb;

reg signed [c_width-1:0] pp_reg;

reg signed [c_width-1:0] out_reg;

wire signed [c_width-1:0] mult_out;

always @(posedge clock) begin

if(reset)begin

ina \le 0;

inb \le 0;

end else begin

if(ce)begin

ina \le a;

inb \le b;

end

end

```

SUG550-1.2 23(54)

```

end

assign mult_out=ina*inb;

always @(posedge clock) begin

if(reset)begin

pp_reg<=0;

end else begin

if(ce)begin

pp_reg<=mult_out;</pre>

end

end

end

always @(posedge clock) begin

if(reset)begin

out_reg<=0;

end else begin

if(ce)begin

out_reg<=pp_reg;</pre>

end

end

end

assign c=out_reg;

endmodule

```

#### 图 4-16 示例 1 DSP 电路图

如上的乘法器电路描述示意图如图 4-16 所示。

示例2可综合出异步模式的乘加器,该乘加器的输入端寄存器为a0\_reg,

SUG550-1.2 24(54)

a1\_reg, b0\_reg 和 b1\_reg, 输出端寄存器为 s\_reg, 旁路寄存器为 p0\_reg 和 p1\_reg。

```

module\ top(a0,\ a1,\ b0,\ b1,\ s,\ reset,\ clock,\ ce);

parameter a0_width=18;

parameter a1_width=18;

parameter b0_width=18;

parameter b1_width=18;

parameter s_width=37;

input unsigned [a0_width-1:0] a0;

input unsigned [a1_width-1:0] a1;

input unsigned [b0_width-1:0] b0;

input unsigned [b1_width-1:0] b1;

input reset, clock, ce;

output unsigned [s_width-1:0] s;

wire unsigned [s_width-1:0] p0, p1, p;

reg unsigned [a0_width-1:0] a0_reg;

reg unsigned [a1_width-1:0] a1_reg;

reg unsigned [b0_width-1:0] b0_reg;

reg unsigned [b1_width-1:0] b1_reg;

reg unsigned [s_width-1:0] p0_reg, p1_reg, s_reg;

always @(posedge clock or posedge reset)

begin

if(reset)begin

a0\_reg \le 0;

a1\_reg \le 0;

b0\_reg \le 0;

b1 reg \le 0;

end else begin

if(ce)begin

a0\_reg \le a0;

a1\_reg \le a1;

b0\_reg \le b0;

b1\_reg \le b1;

end

```

SUG550-1.2 25(54)

```

end

end

assign p0 = a0\_reg*b0\_reg;

assign p1 = a1\_reg*b1\_reg;

always @(posedge clock or posedge reset)

begin

if(reset)begin

p0\_reg \le 0;

p1\_reg \le 0;

end else begin

if(ce)begin

p0\_reg \le p0;

p1_reg <= p1;

end

end

end

assign p = p0\_reg - p1\_reg;

always @(posedge clock or posedge reset)

begin

if(reset)begin

s\_reg \le 0;

end else begin

if(ce) begin

s\_reg \le p;

end

end

end

assign s = s\_reg;

endmodule

如上的乘加器电路描述示意图如图 4-17 所示。

```

SUG550-1.2 26(54)

# 图 4-17 示例 2 DSP 电路图 a0 reg reg reg reg reg reg

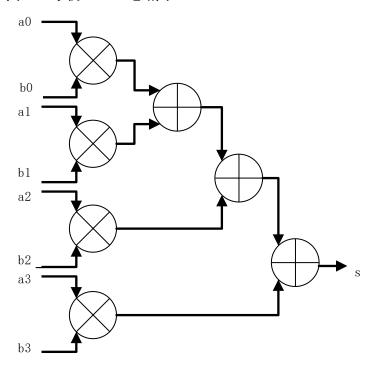

示例 3 可以综合出两个无符号位的乘加器,这两个乘加器为链加关系。 module top(a0, a1, a2, b0, b1, b2, a3, b3, s);

parameter a\_width=18;

parameter b\_width=18;

parameter s\_width=36;

input unsigned [a\_width-1:0] a0, a1, a2, b0, b1, b2, a3, b3;

output unsigned [s\_width-1:0] s;

reg

assign s = a0\*b0+a1\*b1+a2\*b2+a3\*b3;

endmodule

b1

clock reset

如上的乘加器电路描述示意图如图 4-18 所示。

SUG550-1.2 27(54)

#### 图 4-18 示例 3 DSP 电路图

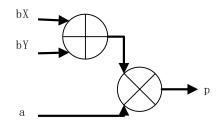

示例 4 可以综合出一个符号位为 0 的乘法器和符号位为 0 的预加器 (乘加器),该乘加器的一个输入端与预加器的输出端 b 相互连接。

```

module top(a, bX, bY, p);

parameter a_width=36;

parameter b_width=18;

parameter p_width=54;

input [a_width-1:0] a;

input [b_width-1:0] bX, bY;

output [p_width-1:0] p;

wire [b_width-1:0] b;

assign b = bX + bY;

assign p = a*b;

endmodule

如上的乘加器电路描述示意图如图 4-19 所示。

```

SUG550-1.2 28(54)

#### 图 4-19 示例 4 DSP 电路图

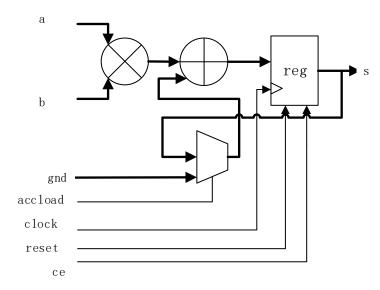

示例 5 可综合出一个具有累加功能的符号位为 0 的乘加器,该乘加器的输出寄存器为 s。

```

module acc(a, b, s, accload, reset, ce, clock);

parameter a_width=36; //18 36

parameter b_width=18; //18 36

parameter s_width=54; //54

input unsigned [a_width-1:0] a;

input unsigned [b_width-1:0] b;

input accload, reset, ce, clock;

output unsigned [s_width-1:0] s;

wire unsigned [s_width-1:0] s_sel;

wire unsigned [s_width-1:0] p;

reg [s_width-1:0] s;

assign p = a*b;

assign \ s\_sel = (accload == 1'b1) ? s : 54'h0000000;

always @(posedge clock)

begin

if(reset)begin

s \leq 0;

end else begin

if(ce)begin

s \le s_sel + p;

end

end

end

endmodule

如上的乘加器电路描述示意图如图 4-20 所示。

```

SUG550-1.2 29(54)

# 图 4-20 示例 5 DSP 电路图

#### 注!

更多示例,请参见 GowinSynthesis®推导置换编码模板文档 "GowinSynthesis\_Inference\_Coding\_Template"。

# 4.4 有限状态机的综合实现规则

# 4.4.1 有限状态机的综合规则

综合工具支持有限状态机(Finate State Machine,FSM)的综合,编码方式支持独热码、格雷码、二进制码等。有限状态机的综合结果与状态机的编码方式、编码个数、编码位宽、编码约束等信息有关。在不设定编码约束的情况下,综合工具自动选用独热码或格雷码实现状态机;若有编码约束的情况下优先根据约束指定的编码方式进行实现,有关状态机的编码约束请参考 5.5 章节。

需要注意的是,有限状态机的输出若直接驱动输出端口,综合工具不将 其作为状态机进行综合,此时状态机上的编码约束将被忽略。

# 4.4.2 有限状态机代码示例

有限状态机的综合规则介绍如下。

# 独热码状态机

若 RTL 设计中状态机采用独热码进行编码,在不设定编码约束的情况下,综合工具默认选择独热码实现状态机的功能,在有编码约束的情况下则依据约束指定的编码方式实现状态机功能。独热码的编码方式举例如下:

reg [3:0] state,next\_state; parameter state0=4'b0001, parameter state1=4'b0010, parameter state2=4'b0100, parameter state3=4'b1000;

SUG550-1.2 30(54)

上述案例中 RTL 采用独热码编码,综合工具采用独热码进行实现。

## 格雷码状态机

若 RTL 设计中状态机采用格雷码进行编码,在不设定编码约束的情况下,综合工具默认选择格雷码实现状态机的功能,在有编码约束的情况下则依据约束指定的编码方式实现状态机功能。格雷码的编码方式举例如下:

```

reg [3:0] state,next_state;

parameter state0=2'b00,

parameter state1=2'b01,

parameter state2=2'b11,

parameter state3=2'b10;

```

上述案例中 RTL 采用格雷码编码,综合工具采用格雷码进行实现。

# 二进制码或其它编码状态机

若 RTL 设计中状态机采用二进制码进行编码,既不是独热码又不是格雷码,在不设定编码约束的情况下,综合工具将根据编码的个数和位宽选择相应的编码进行实现。选取原则如下所示,若编码的个数大于编码的有效位宽则选用格雷码进行实现,若编码的个数小于等于编码的有效位宽则选用独热码进行实现;在有编码约束的情况下则依据约束指定的编码方式实现状态机功能。

示例 1

```

reg [5:0] state,next_state;

parameter state0= 6'b000001,

parameter state1= 6'b000011,

parameter state2= 6'b000000,

parameter state3= 6'b010101;

```

上述案例中编码个数为 4,编码的位宽为 6,其中有效位宽为 5,可见编码的个数小于编码的有效位宽,采用独热码进行实现。

示例 2

```

reg [2:0] state,next_state;

parameter state0=3'b001,

parameter state1=3'b010,

parameter state2=3'b011,

parameter state3=3'b100;

```

上述案例中编码个数为 4,编码的有效位宽为 3,可见编码的个数大于编码的有效位宽,采用格雷码进行实现。

示例3

reg [5:0] state, next\_state;

SUG550-1.2 31(54)

parameter state0= 1, parameter state1= 3, parameter state2= 6, parameter state3= 15;

上述案例中编码的个数为 4,编码采用 10 进制,有效位宽换算为二进制后是 4 位,可见编码的个数等于编码的有效位宽,采用独热码进行实现。

SUG550-1.2 32(54)

# **5** 综合约束支持

属性约束用于设置综合项目中优化选择、功能实现方式、输出网表格式等的各种属性,使综合结果更好地满足用户的设计功能和使用场景。属性设置可以写在约束文件中,也可以嵌入在源码中。

本章描述了 RTL 文件中的约束和 GowinSynthesis<sup>®</sup>约束文件 GSC (Gowin Synthesis Constraint) 约束的语法。Verilog 文件是大小写敏感的,因此指令及属性必须严格按照语法描述的进行输入。约束语句中一条属性约束须写在一行中,中间不可以有换行符等进行分隔,语句末尾需要添加分号。

## RTL 文件中的约束

RTL 文件中的约束必须在约束对象(object)的定义语句中添加,添加在定义语句结束的分号之前。语句中的约束属性值(setting\_value)如果为字符串,则 setting\_value 值前后需添加双引号,如果 setting\_value 值为数字,则 setting\_value 值前后不可以添加双引号。

#### GSC

GSC 约束分为 Instance 类型的约束、Net 类型的约束、Port 类型的约束及全局对象约束。在书写过程中为了区分不同的类型,有不同的语法形式,约束对象必须使用双引号将其括起来,attributeName(属性名称)与约束属性值不需要使用双引号或其他符号标识,之间的等号前后可以有空格,GSC约束中支持注释,注释使用"//"。具体语句语法如下:

INS "object" attributeName=setting\_value;

NET "object" attributeName=setting value;

PORT "object" attributeName=setting\_value;

GLOBAL attributeName=setting value;

约束语句开头为 INS,object 必须为 instance 名称,instance 包括 module/entity instance 及 primitive instance, instance 名称中不包含中括号,即 bus 时不要写 temp[15:0],写成 temp 即可。

约束语句开头为 NET,约束对象必须为 net 名称。

约束语句开头为 PORT,约束对象必须为 port 名称。

约束语句开头为 GLOBAL,说明后面的属性约束是全局属性约束,约束

SUG550-1.2 33(54)

5 综合约束支持 5.1 syn\_dspstyle

对象为全局。

约束中的对象名称必须与网表中的名字匹配,名字中间不可以有空格,对象名称中支持通配符,使用"/"来区分名字之间的层级关系。使用通配符时对象名前加w来区分,比如w"object"。

约束属性值(setting\_value)的设定值可能是用户直接指定的值、继承于上层结构的值,和该属性的默认值。取值的优先顺序为直接值>继承值>默认值,拥有多个继承值时,取距离指定名字最近(层级最低)的值。例如,查询 A/D/C/mult1("/"来表示模块名字之间的层级关系)的 MULT\_STYLE 属性,其有直接值为 dsp;查询 "A/D/C"的 MULT\_STYLE 属性,其没有直接值,而 MULT\_STYLE 属性可以继承,所以找到并继承"A/D"的属性值 logic;查询"A/D/C/mult1"的 MULT\_STYLE,其既有"A/D 的继承值,又有直接值,由于直接值优先级高,所以最终取直接值 DSP。

# 5.1 syn\_dspstyle

# 描述

指定乘法器以专用 DSP 硬件模块或逻辑电路的方式实现,既可以作用于具体 instance,也可以作用于全局范围。该属性可在 GSC、RTL 文件中指定。

# 语法

GSC 约束语法

INS "object" syn\_dspstyle =setting\_value;

GLOBAL syn\_dspstyle =setting\_value;

Veilog 约束语法

Verilog object /\* synthesis syn dspstyle ="setting value" \*/;

VHDL 约束语法

attribute syn\_dspstyle:string;

attribute syn\_dspstyle of object:objectType is "setting\_value";

object: 指定作用的对象,可以是 module/entity 名,module/entity instance 名或者 primitive instance 名。

## 注!

- setting\_value: 乘法器实现方式, 当前支持 dsp, logic;

- setting\_value 为 logic: 把 object 映射为逻辑电路;

- setting\_value 为 dsp: 把 object 映射为 DSP, 也是默认情况。

#### 示例

GSC 约束示例

示例 1 指定 instance 实现方式为 logic

INS 'temp" syn\_dspstyle=logic;

INS "aa0/mult/c" syn\_dspstyle=logic;

SUG550-1.2 34(54)

5 综合约束支持 5.1 syn\_dspstyle

```

示例 2 指定全局所有乘法器实现方式为 logic

GLOBAL syn_dspstyle=logic;

Verilog 约束示例

示例 1 指定 mult module 中的所有乘法器实现方式为 logic

module mult(...) /* synthesis syn_dspstyle = "logic" */;

wire [15:0] temp;

assign temp = a*b;

endmodule

示例 2 指定乘法器 temp 实现方式为 logic

module mult(...);

wire [15:0] temp/* synthesis syn_dspstyle = "logic" */;

assign temp = a*b;

. . . . . .

Endmodule

VHDL 约束示例

entity Mult is

port(

result: out signed(23 downto 0));

attribute syn_dspstyle:string;

attribute syn_dspstyle of result : signal is "logic";

end Mult;

architecture Behavior of Mult is

signal x1: signed(11 downto 0);

signal y1: signed(11 downto 0);

begin

result \leq x1 * y1;

end Behavior;

```

SUG550-1.2 35(54)

5 综合约束支持 5.2 syn\_ramstyle

# 5.2 syn\_ramstyle

# 描述

指定存储器的实现方式,既可以作用于具体对象,也可以作用于全局范 围。

该属性可在 GSC、RTL 文件中指定。

## 语法

GSC 约束语法

INS "object" syn\_ramstyle =setting\_value;

GLOBAL syn\_ramstyle =setting\_value;

Verilog 约束语法

Verilog object /\* synthesis syn ramstyle = "setting value" \*/;

VHDL 约束语法

attribute syn\_ramstyle:string;

attribute syn\_ramstyle of object : objectType is " setting\_value";

object: 指定作用的对象,可以是 module/entity 名,module/entity instance 名或者 primitive instance 名。

#### 注!

- setting\_value: 存储器的实现方式,当前支持 block\_ram,distributed\_ram,registers,rw\_check,no\_rw\_check;

- setting\_value 为 registers: 将 inferred RAM 映射为 registers (触发器和逻辑电路),而不是专用的 RAM 资源;

- setting\_value 为 block\_ram: 将 inferred RAM 映射为适当的设备专用内存,其使用 FPGA 的专用内存资源;

- setting\_value 为 distributed\_ram:将 inferred RAM 映射为适当的设备专用内存(分布式内存块);

- setting\_value 为 rw\_check/no\_rw\_check: 默认情况下 (rw\_check), 当读和写在同一地址时,不确定的外部输入会导致仿真不匹配,这时,综合工具会在推导的 RAM 周围插入 bypass 逻辑以避免这种仿真不匹配的情况。如果将该属性值设为 no\_rw\_check,则不会进行读写检查,推导出的 RAM 周围不会插入 bypass 逻辑。

#### 示例

GSC 约束示例

示例 1 指定 instance 实现方式为 B-SRAM 硬核

INS "mem" syn\_ramstyle=block\_ram;

示例 2 指定全局所有存储器实现方式为 SSRAM

GLOBAL syn\_ramstyle=distributed\_ram;

Verilog 约束示例

示例 1 指定 module 内所有的存储器实现方式为 block\_ram,并且不进行读写检查

SUG550-1.2 36(54)

5 综合约束支持 5.3 syn\_romstyle

```

module test (...) /* synthesis syn_ramstyle = "no_rw_check,block_ram"

*/;

. . . . . .

endmodule

示例 2 指定 instance 实现方式为 B-SRAM 硬核

module test (...);

reg [DATA_W - 1 : 0] mem [(2**ADDR_W) - 1 : 0] /* synthesis

syn ramstyle = "block ram" */;

. . . . . .

Endmodule

VHDL 约束示例

entity ram is

GENERIC(bits:INTEGER:=8;

words:INTEGER:=256);

PORT(.....);

end ram;

ARCHITECTURE ram of ram IS

TYPE vector_array IS ARRAY(0 TO words-1) OF

STD_LOGIC_VECTOR(bits-1 DOWNTO 0);

SIGNAL memory:vector_array;

attribute syn_ramstyle:string;

attribute syn_ramstyle of memory : signal is "distributed_ram";

BEGIN

end ram;

```

# 5.3 syn\_romstyle

# 描述

指定只读存储器的实现方式,既可以作用于具体对象,也可以作用于全 局范围。

该属性可在 GSC、RTL 文件中指定。

## 语法

GSC 约束语法

INS "object" syn\_romstyle =setting\_value;

SUG550-1.2 37(54)

5 综合约束支持 5.4 syn\_maxfan

```

GLOBAL syn_romstyle =setting_value;

Verilog 约束语法

Verilog object /* synthesis syn_romstyle = "setting value" */;

VHDL 约束语法

attribute syn_romstyle:string;

attribute syn_romstyle of object : objectType is " setting_value";

object: 指定作用的对象,可以是 module/entity 名,module/entity

instance 名或者 primitive instance 名。

注!

setting_value: 只读存储器的实现方式,当前支持 block_rom,distributed_rom,logic。

示例

GSC 约束示例

示例 1 指定 instance 实现方式为 BSRAM 硬核

INS "mem" syn_romstyle=block_rom;

示例 2 指定全局所有存储器实现方式为 SSRAM

GLOBAL syn_romstyle=distributed_rom;

Verilog 约束示例

示例 1 指定 module 内的所有存储器实现方式为 SSRAM

module rom16 test(...)/*synthesis syn romstyle="distributed rom"*/:

Endmodule

VHDL 约束示例

ENTITY rom is

end rom;

ARCHITECTURE rom OF rom IS

signal data_out :STD_LOGIC_VECTOR(bits-1 DOWNTO 0);

attribute syn_romstyle:string;

attribute syn_romstyle of data_out : signal is "logic";

END rom;

```

# 5.4 syn\_maxfan

## 描述

指定最大扇出值,既可以作用于具体对象,也可以作用于全局范围。

SUG550-1.2 38(54)

5 综合约束支持 5.4 syn\_maxfan

该属性可在 GSC、RTL 文件中指定。

## 语法

```

GSC 约束语法

INS "object" syn_maxfan=setting_value;

NET "object" syn_maxfan=setting_value;

GLOBAL syn_maxfan=setting_value;

Verilog 约束语法

Verilog object /* synthesis syn_maxfan = setting_value */;

VHDL 约束语法

attribute syn_maxfan : integer;

attribute syn_maxfan of object : objectType is setting_value;

object: 指定作用的对象,可以是 module/entity 名,module/entity

instance 名或者 primitive instance 名。

注!

setting_value: 大于 0 的整数。

示例

GSC 示例

示例 1 指定 instance 的最大扇出值为 10

INS "d" syn maxfan=10:

示例 2 指定全局的最大扇出值为 100

GLOBAL syn maxfan=100;

示例 3 指定 instance 的最大扇出值为 10

INS "aa0/mult/d" syn maxfan=10;

示例 4 指定 net 的最大扇出值为 10

NET "aa0/mult/d" syn_maxfan=10;

Verilog 示例

示例 1 指定 module 内所有 instance 的最大扇出值为 3

module test (...) /* synthesis syn_maxfan = 3*/;

. . . . . .

endmodule

示例 2 指定 instance 的最大扇出值为 3

module test (...);

reg [7:0] d /* synthesis syn_maxfan = 3*/;

```

SUG550-1.2 39(54)

5 综合约束支持 5.5 syn\_encoding

```

Endmodule

VHDL 示例

entity test is

......

end test;

architecture rtl of test is

signal d: std_logic;

attribute syn_maxfan: integer;

attribute syn_maxfan of d: signal is 5;

......

end rtl:

```

# 5.5 syn\_encoding

## 描述

指定状态机编译器的编码方式,既可以作用于具体对象,也可以作用于全局范围。

该属性只可在 RTL 文件中指定。

# 语法

```

Verilog 语法

verilog object /* synthesis syn_encoding = "setting_value" */;

VHDL 约束语法

attribute syn_encoding : string;

attribute syn_encoding of object : objectType is "setting_value";

```

注!

- object: 指定作用的对象, 只可以是 register 名;

- setting\_value: 状态机的编码方式,当前支持的编码方式有 onehot, gray。

## 示例

```

Verilog 示例

示例 1 指定状态机按照 gray 码的方式来进行编码

module test (...);

reg [2:0] ps, ns/* synthesis syn_encoding="gray" */;

.....

Endmodule

VHDL 示例

ENTITY fsm IS

```

SUG550-1.2 40(54)

5 综合约束支持 5.6 syn\_insert\_pad

. . . . . .

END fsm;

ARCHITECTURE behaviour OF fsm IS

TYPE state\_type IS (s0,s1,s2,s3);

SIGNAL present\_state, next\_state: state\_type;

attribute syn\_encoding:string;

attribute syn\_encoding of present\_state,next\_state:signal is "onehot";

**BEGIN**

. . . . . .

END behaviour;

# 5.6 syn\_insert\_pad

#### 描述

指定是否插入 I/O buffer。当属性值为 1 时,插入 I/O buffer。 该属性只可在 GSC 文件中指定。

# 语法

GSC 约束语法

PORT "object" syn\_insert\_pad=setting\_value;

#### 注!

- setting\_value: 0 或者 1。为 0 时,移除 I/O buffer;为 1 时,插入 I/O buffer。

- object: 只可以为 port,此约束只对 Input port 或 Output port 起作用,对 Inout port 不 起作用。

## 示例

GSC 示例

示例 1 指定插入 I/O buffer

PORT "out" syn\_insert\_pad=1;

示例 2 指定移除 I/O buffer

PORT "out" syn\_insert\_pad=0;

# 5.7 syn\_netlist\_hierarchy

## 描述

指定是否生成的层级结构的网表。默认值为 1 表示生成层级结构网表;设置为 0 时,则将层级结构网表进行扁平化输出。

该属性可在 GSC、RTL 文件中指定。

## 语法

GSC 约束语法

SUG550-1.2 41(54)

5.8 syn\_preserve

```

GLOBAL syn_netlist_hierarchy=setting_value;

setting_value: 0 或者 1,为 1 时,允许生成 hierarchy;设置属性值为

0,则扁平化输出层级结构的网表。

Verilog 约束语法

Verilog object /* synthesis syn_netlist_hierarchy=setting_value */;

VHDL 约束语法

attribute syn_netlist_hierarchy: integer;

attribute syn_netlist_hierarchy of object : objectType is setting_value;

注!

object: 指定作用的对象, 只能是 top module/entity。

示例

GSC 示例

GLOBAL syn_netlist_hierarchy=0;

Verilog 示例

module rp_top (...) /* synthesis syn_netlist_hierarchy=1 */;

Endmodule

VHDL 示例

entity mux4_1_top is

port(

dina: in bit;

dinb: in bit:

sel: in bit;

dout: out bit

);

attribute syn_netlist_hierarchy: integer;

attribute syn_netlist_hierarchy of mux4_1_top: entity is 0;

end mux4_1_top;

```

# 5.8 syn\_preserve

## 描述

指定寄存器或寄存器逻辑是否被优化,既可以作用于具体对象,也可以 作用于全局范围。

该属性可在 RTL 文件及 GSC 文件中指定。

SUG550-1.2 42(54)

5.8 syn\_preserve

# 语法

```

GSC 约束语法

INS "object" syn_preserve=setting_value;

GLOBAL syn_preserve=setting_value;

Verilog 约束语法

Verilog object /* synthesis syn_preserve = setting_value */;

VHDL 约束语法

attribute syn preserve : integer;

attribute syn_preserve of object : objectType is setting_value;

注!

object: 指定作用的对象,可以是 register 名, module /entity 名, module /entity instance 名。

setting_value: 0 或者 1。为 1 时保留对应寄存器;为 0 时根据需要优化对应的寄存器。

示例

GSC 示例

示例 1 指定保留 req1 不被优化掉

INS "reg1" syn preserve =1;

示例 2 指定保留设计中的所有寄存器

GLOBAL syn_ preserve =1;

Verilog 示例

示例 1 指定保留 module 中的所有寄存器

module test (...) /* synthesis syn_preserve = 1 */;

endmodule

示例 2 指定保留 reg1 不被优化掉

module test (...);

reg reg1/* synthesis syn_preserve = 1 */;

endmodule

VHDL 示例

entity syn_test is

port (.....

);

end syn_test;

architecture behave of syn_test is

```

SUG550-1.2 43(54)

5 综合约束支持 5.9 syn\_keep

```

signal reg1 : std_logic;

signal reg2 : std_logic;

attribute syn_preserve : integer;

attribute syn_preserve of reg1: signal is 1;

begin

end behave;

5.9 syn_keep

描述

指定 net 作为占位符而将其保留、不进行优化。

该属性只可在 RTL 文件中指定。

语法

Verilog 约束语法

Verilog object /* synthesis syn_keep= setting_value */;

VHDL 约束语法

attribute syn_keep: integer;

attribute syn_keep of object : objectType is 1;

注!

object: 指定作用的对象,只能是 net 名。

setting_value: 只能为 0 或者 1, 为 1 时保留该 net 不进行优化。

示例

Verilog 约束示例

示例 1 指定 mywire 不被优化掉

module test (...);

wire mywire /* synthesis syn_keep=1 */;

. . . . . .

Endmodule

VHDL 约束示例

entity mux2_1 is

port(

);

end mux2_1;

```

SUG550-1.2 44(54)

5 综合约束支持 5.10 syn\_probe

```

architecture Behavioral of mux2_1 is

signal tmp0:bit;

signal tmp1:bit;

attribute syn_keep : integer;

attribute syn_keep of tmp0 : signal is 1;

attribute syn_keep of tmp1 : signal is 1;

......

end Behavioral;

```

# 5.10 syn\_probe

## 描述

该属性通过插入探测点对设计中的内部信号进行测试和调试。被指定的探测点将以 port 的形式出现在顶层端口列表中。

该属性只可在 RTL 文件中指定。

# 语法

```

Verilog 约束语法

Verilog object /* synthesis syn_probe = setting_value */;

VHDL 约束语法

attribute syn_probe: string;

attribute syn_probe of object: objectType is " setting_value ";

```

#### 注!

- object: 指定作用的对象, 只可以是 net 名;

- setting\_value 值为 1: 插入探测点,根据 net 的名称自动得到探测 port 的名称;

- setting\_value 值为 0: 不允许探测;

- setting\_value 值为字符串:插入一个指定名字的探测点。当 setting\_value 指定的名字为 bus 时,插入的名称后会自动添加数字。

- gowinSyn 不支持 setting\_value 的值与 object 名字或者 module 的 port 名相同。

# 示例

Verilog 约束示例, probe\_tmp 被设置该属性后, probe\_tmp 将被列在顶层输出端口列表中。

```

module test (...);

.....

reg [7:0] probe_tmp /* synthesis syn_probe=1*/;

.....

endmodule

VHDL 约束示例

entity halfadd is

```

SUG550-1.2 45(54)

```

port(.....);

end halfadd:

architecture add of halfadd is

signal probe_tmp: std_logic;

attribute syn_probe: string;

attribute syn_probe of probe_tmp: signal is "probe_string";

end:

```

# 5.11 Translate\_off/Translate\_on

## 描述

translate\_off/translate\_on 必须成对出现,translate\_off 之后的语句将在 综合过程中被跳过,直到 translate\_on 出现,常用于在综合时自动屏蔽一些 语句。

该属性只可在 RTL 文件中指定。

# 语法

```

Verilog 约束语法

/* synthesis translate_off*/;

综合过程中被忽略的语句

/* synthesis translate_on*/

VHDL 约束语法

-- synthesis translate_off

综合过程中被忽略的语句

-- synthesis translate_on

示例

Verilog 约束示例

示例 1 /*synthesis translate_off*/与/*synthesis translate_on*/之间的

assign Nout =a*b 语句在综合过程中被忽略,不进行综合

module test (...);

/*synthesis translate_off*/

assign my_ignore=a*b;

/*synthesis translate on*/

Endmodule

```

SUG550-1.2 46(54) 5 综合约束支持 5.12 Full\_case

```

VHDL 约束示例

entity top is

port (

......

);

end top;

architecture rtl of top is

begin

dout <= a + b;

-- synthesis translate_off

Nout <= a * b;

-- synthesis translate_on

end rtl;

```

# 5.12 Full\_case

## 描述

full\_case 只在 Verilog 的设计中使用。当使用了 case, casex 或者 casez 语句时,添加此属性说明所有可能的值都已经给出,不需要使用多余的硬件来保留信号值。

该属性只可在 RTL 文件中指定,只支持 Verilog 语法的设计。

# 语法

```

Verilog 约束语法

verilog case /* synthesis full_case*/

```

# 示例

```

Verilog 约束示例

示例 1 指定此部分电路不再需要使用多余的硬件来保留信号值

module top(...);

......

always @(select or a or b or c or d)

begin

casez(select) /* synthesis full_case*/

4'b???1: out=a;

......

4'b1???: out=d;

endcase

```

SUG550-1.2 47(54)

end

endmodule

# 5.13 syn\_tlvds\_io/syn\_elvds\_io

# 描述

指定差分的 I/O buffer 映射的属性,既可以作用于具体对象,也可以作用于全局范围。该属性可在 GSC、RTL 文件中指定。

# 语法

```

GSC 约束语法

```

PORT "object" syn\_tlvds\_io =setting\_value;

GLOBAL syn\_tlvds\_io =setting\_value;

PORT "object" syn\_elvds\_io =setting\_value;

GLOBAL syn\_elvds\_io =setting\_value;

Verilog 约束语法

Verilog object /\* synthesis syn\_tlvds\_io = setting\_value \*/;

VHDL 约束语法

attribute syn\_tlvds\_io: integer;

attribute syn\_tlvds\_io of object: objectType is setting\_value;

#### 注!

- object: 指定作用的对象,可以是 module/entity 名, port 名;

- setting\_value: 0 或者 1。

## 示例

GSC 约束示例

示例 1 指定 buffer 实现方式为 TLVDS

PORT "io" syn tlvds io =1;

PORT "iob" syn\_tlvds\_io =1;

示例 2 指定全局所有 buffer 实现方式为 TLVDS

GLOBAL syn\_tlvds\_io =1;

Verilog 约束示例

module elvds\_iobuf(io,iob...);

inout io/\*synthesis syn\_elvds\_io=1\*/;

inout iob/\*synthesis syn\_elvds\_io=1\*/;

. . . . . .

Endmodule

VHDL 约束示例

SUG550-1.2 48(54)

5 综合约束支持 5.14 syn\_looplimit

```

entity test is

port (in1_p : in std_logic;

in1_n : in std_logic;

clk : in std_logic;

out1 : out std_logic;

out2 : out std_logic);

attribute syn_tlvds_io: integer;

attribute syn_tlvds_io of in1_p,in1_n,out1,out2: signal is 1;

end test;

architecture arch of test is

.....

end arch

```

# 5.14 syn\_looplimit

# 描述

指定设计中循环迭代限制的值,默认循环迭代次数为 2000。设计中如果循环迭代次数超过 2000,但是没有指定循环次数,综合过程中会报错。

该属性只可在 GSC 中设置。

## 语法

GSC 约束语法

GLOBAL syn\_looplimit=setting\_value

#### 注!

setting\_value: 只可以为数字,代表此设计中循环迭代次数的上限。

## 示例

GSC 约束示例

GLOBAL syn\_looplimit=3000

SUG550-1.2 49(54)

# 6 Report 用户文档

report 文档是在执行综合之后,生成的统计报告文件,文件名为 \*\_syn.rpt.html (\*为指定输出网表 vg 文件的名称),包含 Synthesis Message, Design Settings, Resource, Timing, Message, Summary 六部分,下面分别 进行介绍。

# 6.1 Synthesis Message

Synthesis Message,即综合基本信息。主要包括综合的设计文件,当前 GowinSynthesis<sup>®</sup>版本,运行时间等信息,如图 6-1 所示:

# 图 6-1 Synthesis Message

# Synthesis Messages

| Report Title                    | GowinSynthesis Report                                                        |

|---------------------------------|------------------------------------------------------------------------------|

| Design File                     | /gwsw/sw_pub/swfiles/Gowin/memory/src/ram_1.v                                |

| GowinSynthesis Constraints File |                                                                              |

| GowinSynthesis Verision         | GowinSynthesis V1.9.2Beta                                                    |

| Created Time                    | Wed Aug 14 17:26:08 2019                                                     |

| Legal Announcement              | Copyright (C)2014-2019 Gowin Semiconductor Corporation. ALL rights reserved. |

# 6.2 Design Settings

Design Settings,即设计配置信息。主要包括综合的设计文件的顶层模块,设置的语言类型,指定的芯片类型等信息,如图 6-2 所示:

#### 图 6-2 Design Settings

# **Design Settings**

| Top Level Module: | RAM_test |

|-------------------|----------|

| Design Language:  | verilog  |

| Series:           | GW2A     |

| Device:           | GW2A-55  |

| Package:          | PBGA484  |

| Speed Grade:      | 7        |

SUG550-1.2 50(54)

6 Report 用户文档 6.3 Resource

# 6.3 Resource

Resource,即资源信息。主要包括资源使用统计和芯片占用统计。

资源使用表会统计用户设计中 IOPORT, IOBUF, REG, LUT 等的数量。 资源利用率表用于预估用户设计中 CFU Logics, Register, BSRAM, DSP 等在当前器件的资源占用率,如图 6-3 所示:

## 图 6-3 Resource

#### Resource

## **Resource Usage Summary**

| IOPORT Usage: | 16 |

|---------------|----|

| IOBUF Usage:  | 16 |

| IBUF          | 12 |

| OBUF          | 4  |

| BSRAM Usage:  | 1  |

| SP            | 1  |

## **Resource Utilization Summary**

Target Device: GW2A-55-PBGA484

| CFU Logics | 0(0 LUTs, 0 ALUs) / 54720 | 0% |

|------------|---------------------------|----|

| Registers  | 0 / 41040                 | 0% |

| BSRAMs     | 1 / 140                   | 1% |

| DSP Macros | 0 / (10*2)                | 0% |

# 6.4 Timing

Timing,即时序统计。主要包括 Clock Summary,Timing Report,Performance Summary,Detail Timing Paths Informations 等信息。

Clock Summary 主要描述网表的时钟信号信息,如下图 6-4 所示,给出一个默认时钟,频率为 100MHZ,周期为 10ns,0ns 时为上升沿,5ns 时为下降沿。

Timing Report 主要描述网表文件的时序信息,包括顶层模块,限制频率,显示时序路径最大数量,默认为5条,所有时间值的单位均为纳秒。

SUG550-1.2 51(54)

6 Report 用户文档 6.4 Timing

## 图 6-4 Timing

## **Timing**

#### **Clock Summary:**

| Clock       | Туре | Frequency | Period | Rise  | Fall  | Source | Master | Object |

|-------------|------|-----------|--------|-------|-------|--------|--------|--------|

| DEFAULT_CLK | Base | 100.0 MHz | 10.000 | 0.000 | 5.000 |        |        |        |

#### **Timing Report:**

| Top View:                 | test_time |

|---------------------------|-----------|

| Requested Frequency:      | 100.0 MHz |

| Paths Requested:          | 5         |

| Constraint File(ignored): |           |

All time values displayed in nanoseconds(ns).

Performance Summary 主要统计网表文件的最大时间延迟,可以达到的时钟频率,并以此来衡量整个网表文件的时序是否达到要求。如下图 6-5 中所示。时间余量为 8.462ns,要求频率为 100MHZ,可达到时钟频率为 650MHZ,要求时钟周期为 10ns,可达到时钟周期为 1.538ns,满足时序要求,若时间余量为负数,则不满足时序要求,需要进一步查看具体时序路径。

#### 图 6-5 Performance Summary

#### **Performance Summary:**

Worst Slack in Design: 8.462

| Start Clock Slac | k Requested Frequency | Estimated Frequency | Requested Period | Estimated Period | Clock Type |

|------------------|-----------------------|---------------------|------------------|------------------|------------|

| DEFAULT_CLK 8.46 | 2 100.0 MHz           | 650.1 MHz           | 10.000           | 1.538            | Base       |

Detail Timing Paths Information 主要描述网表文件中的关键时序路径, 起始节点及相关时延信息,如图 6-6 所示。并给出详细的连接关系,时延, 扇出信息,如图 6-7 所示。

## 图 6-6 Detail Timing Paths Information

#### **Detail Timing Paths Information**

Path information for path number 1 :

| Clock Skew:                    | 0.000               |

|--------------------------------|---------------------|

| Setup Relationship:            | 10.000              |

| Slack(critical):               | 8.462               |

| Data Arrival Time:             | 2.283               |

| Data Required Time:            | 10.745              |

| Number of Logic Level:         | 0                   |

| Starting Point:                | df1                 |

| Ending Point:                  | dff2                |

| The Start Point Is Clocked By: | DEFAULT_CLK[rising] |

| The End Point Is Clocked By:   | DEFAULT_CLK[rising] |

SUG550-1.2 52(54)

6 Report 用户文档 6.5 Message

#### 图 6-7 连接关系、时延及扇出信息

| Instance/Net Name | Туре | Pin Name | Pin Dir | Delay | Arrival Time | Fanout |

|-------------------|------|----------|---------|-------|--------------|--------|

| clk_ins12         | IBUF | 1        | In      | -     | 0.000        | -      |

| clk_ins12         | IBUF | 0        | Out     | 0.982 | 0.982        | -      |

| clk_3             | Net  | -        | -       | 0.363 | -            | 4      |

| dff1_ins1         | DFF  | CLK      | In      | -     | 1.345        | -      |

| dff1_ins1         | DFF  | Q        | Out     | 0.458 | 1.803        | -      |

| b                 | Net  | -        | -       | 0.480 | -            | 1      |

| dff2_ins2         | DFF  | D        | In      | -     | 2.283        | -      |

Total Path Delay: 2.283 Logic Delay: 1.440(63.1%) Route Delay: 0.843(36.9%)

# 6.5 Message

Message,即综合输出信息。是综合过程中给出的 log 信息, log 信息包 含 Info, Warning 及 Error 三种类型的信息, Info 信息为提示信息, Warning 信息为警告信息, Error 信息为错误信息。当运行中出现 Error 信息时,综合 过程退出,不会产生输出文件。综合输出信息如图 6-8 所示。

#### 图 6-8 综合输出信息

# Message

Info (EXT0100): Run analyzation & elaboration

Info (EXT1482): Analyzing Verilog file '/share/gwsw/sw\_pub/swfiles/Gowin/fpga\_project/src/counter1.v' Info (EXT1018): Compiling module 'RAM\_test'(/gwsw/sw\_pub/swfiles/Gowin/memory/src/ram\_1.v:2)

Info (EXT0101): Current top module is "RAM\_test"

Info (CVT0001): Run conversion

Info (DIO0001): Run device independent optimization

Info (DIO0006): Register and gate optimizing before inferencing

Info (DSP0001): DSP inferencing Info (RAM0001): RAM inferencing

Info (DIO0001): Run device independent optimization

Info (DIO0007): Register and gate optimizing before mapping Info (MAP0001): Run tech-mapping

Info (DIO0001): Run device independent optimization

Info (SYN0009): Write post-map netlist to file:

/gwsw/sw\_pub/swfiles/Gowin/memory/impl/gwsynthesis/memory.vg

# 6.6 Summary

Summary 表,统计输出信息中的 warning, error, information 数量, 并给出综合的实际运行时间和 CPU 运行时间,以及综合过程中的 Memory peak 即内存占用峰值情况。如图 6-9 所示。

## 图 6-9 Summary

# Summary

| Total Errors:       | 0  |

|---------------------|----|

| Total Warnings:     | 0  |

| Total Informations: | 14 |

#### Synthesis completed successfully!

Process took 0h:0m:0s realtime, 0h:0m:0s cputime

Memory peak: 121.3MB

SUG550-1.2 53(54)

# **7** 层级资源信息文档

层级资源信息文档是在执行综合之后,生成的各模块资源统计文件,其文件名构成为\*\_syn\_resource.html(\*为指定输出网表 vg 文件的名称)。

Resource 文件会统计模块层级结构,以及各模块的资源统计信息,并按照层级结构打印。如图 7-1 所示,Resource 文件会从顶层模块到底层模块按深度优先的顺序进行打印所有模块。每行打印信息包括各模块名称、所在文件路径,以及各模块中 REG,ALU,LUT,DSP,BSRAM,SSRAM 等资源的数量。用户可通过层级资源信息文档具体查看各模块层级结构的详细资源信息。

## 图 7-1 Hierarchy Module Resource

#### **Hierarchy Module Resource**

| MODULE NAME                                                                          | REG NUMBER | ALU NUMBER | LUT NUMBER | DSP NUMBER | BSRAM NUMBER | SSRAM NUMBER |

|--------------------------------------------------------------------------------------|------------|------------|------------|------------|--------------|--------------|

| nflash_test_top (/share/gwsw/sw_pub/swfiles/Gowin/nflash_test/nflash_test_top.v)     | 2          | -          | -          | -          | -            | -            |

| pll_inst (/share/gwsw/sw_pub/swfiles/Gowin/nflash_test/nflash_test_top.v)            | -          | -          | -          | -          | -            | -            |

| flash_data_cmd_inst (/share/gwsw/sw_pub/swfiles/Gowin/nflash_test/nflash_test_top.v) | 36         | -          | 85         | -          | -            | -            |

| mixBF (/share/gwsw/sw_pub/swfiles/Gowin/nflash_test/flash_data_cmd.v)                | -          | -          | 1          | -          | -            | -            |

| nfcm_top_inst (/share/gwsw/sw_pub/swfiles/Gowin/nflash_test/nflash_test_top.v)       | 32         | -          | 80         | -          | -            |              |

| dp_2k_d8 (/share/gwsw/sw_pub/swfiles/Gowin/nflash_test/nfcm_top.v)                   | -          | -          | -          | -          | 1            | -            |

| addr_counter (/share/gwsw/sw_pub/swfiles/Gowin/nflash_test/nfcm_top.v)               | 12         | -          | 22         | -          | -            | -            |

| tim_fsm (/share/gwsw/sw_pub/swfiles/Gowin/nflash_test/nfcm_top.v)                    | 9          | -          | 67         | -          | -            | -            |

| main_fsm (/share/gwsw/sw_pub/swfiles/Gowin/nflash_test/nfcm_top.v)                   | 8          | -          | 173        | -          | -            | -            |

| ecc_gen (/share/gwsw/sw_pub/swfiles/Gowin/nflash_test/nfcm_top.v)                    | 7          | -          | 3          | -          |              | -            |

| ecc_err_loc (/share/gwsw/sw_pub/swfiles/Gowin/nflash_test/nfcm_top.v)                | 8          | -          | 6          | -          | -            | -            |

SUG550-1.2 54(54)