## Gowin Design Timing Constraints **User Guide**

SUG940-1.7E, 02/02/2024

#### Copyright © 2024 Guangdong Gowin Semiconductor Corporation. All Rights Reserved.

**GOWIN** and LittleBee are trademarks of Guangdong Gowin Semiconductor Corporation and are registered in China, the U.S. Patent and Trademark Office, and other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders. No part of this document may be reproduced or transmitted in any form or by any denotes, electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of GOWINSEMI.

#### Disclaimer

GOWINSEMI assumes no liability and provides no warranty (either expressed or implied) and is not responsible for any damage incurred to your hardware, software, data, or property resulting from usage of the materials or intellectual property except as outlined in the GOWINSEMI Terms and Conditions of Sale. GOWINSEMI may make changes to this document at any time without prior notice. Anyone relying on this documentation should contact GOWINSEMI for the current documentation and errata.

## **Revision History**

| Date            | Version | Description                                                                                       |

|-----------------|---------|---------------------------------------------------------------------------------------------------|

| 06/09/2020      | 1.0E    | Initial version published.                                                                        |

| 09/01/2020 1.1E |         | Automotive grade added in operating condition;                                                    |

| 09/01/2020      | 1.10    | • The link between base clock and generated clock added.                                          |

| 06/16/2021      | 1.2E    | <ul> <li>The descriptions of wildcards added.</li> </ul>                                          |

| 00,10,2021      | 1.20    | Some figures updated.                                                                             |

|                 |         | <ul> <li>Software version updated.</li> </ul>                                                     |

| 11/02/2021      | 1.3E    | <ul> <li>Some figures and corresponding descriptions updated.</li> </ul>                          |

|                 |         | Appendix A Timing Constraints Syntax Specification updated.                                       |

| 05/20/2022      | 1.3.1E  | Some language descriptions updated.                                                               |

|                 |         | <ul> <li>-Add option added in Create Clock.</li> </ul>                                            |

| 07/28/2022      | 1.4E    | • The description of temperature and voltage of delay data model updated.                         |

| 01/20/2022      |         | <ul> <li>The descriptions of tUnc and tSu added.</li> </ul>                                       |

|                 |         | • The function of wildcard character cross-hierarchy matching added.                              |

| 12/13/2022      | 1.4.1E  | The description of Add delay in 4.7.2 I/O Delay Constraints updated.                              |

|                 | 1.4.2E  | <ul> <li>The descriptions of set_input_delay and set_output_delay in 4.7.2 I/O</li> </ul>         |

| 03/31/2023      |         | Delay Constraints updated.                                                                        |

|                 |         | • The description of 5.1.4 Total Negative Slack Summary updated.                                  |

| 04/20/2023      | 1.4.3E  | Figure 4-8 New Constraint, Figure 4-9 Open Timing Constraint, and the related descriptions added. |

|                 |         | The descriptions of exception constraints updated.                                                |

| 05/25/2023      | 1.5E    | • The descriptions of the virtual clock DEFAULT_CLK updated.                                      |

| 00/40/0000      |         | <ul> <li>set_operation_conditions modified to set_operating_conditions.</li> </ul>                |

| 08/18/2023      | 1.5.1E  | • The constraint descriptions of reporting max. clock frequency updated.                          |

|                 |         | • Descriptions of conversion between clock period and frequency removed.                          |

| 11/30/2023      | 1.6E    | <ul> <li>Process window screenshot and related description removed.</li> </ul>                    |

|                 |         | <ul> <li>Descriptions of A.2.2 set_output_delay updated.</li> </ul>                               |

| 02/02/2024      | 1.7E    | derive_clocks constraint added.                                                                   |

## Contents

| Contentsi                                   |

|---------------------------------------------|

| List of Figuresiv                           |

| List of Tablesvi                            |

| 1 About This Guide1                         |

| 1.1 Purpose                                 |

| 1.2 Related Documents1                      |

| 1.3 Terminology and Abbreviations1          |

| 1.4 Support and Feedback2                   |

| 2 Introduction                              |

| 3 STA Overview                              |

| 3.1 Overview                                |

| 3.2 Basic Model4                            |

| 3.3 Terms                                   |

| 3.4 Path5                                   |

| 3.5 Common Timing Checks6                   |

| 3.5.1 Setup Time and Hold Time Check6       |

| 3.5.2 Recovery Time and Removal Time Check6 |

| 3.5.3 MPW Check                             |

| 4 Timing Constraints Editor7                |

| 4.1 Overview                                |

| 4.2 Start Timing Constraints Editor7        |

| 4.3 Create/Open/Add Constraints File7       |

| 4.3.1 Create Constraints File7              |

| 4.3.2 Open Constraints File9                |

| 4.3.3 Add Constraints File10                |

| 4.4 Timing Constraints Editor Interface     |

| 4.5 Open Timing Constraints Window          |

| 4.6 Edit SDC File                           |

| 4.7 Create Timing Constraints14             |

|    | 4.7.1 Clock Constraints                           | . 14 |

|----|---------------------------------------------------|------|

|    | 4.7.2 I/O Delay Constraints                       | . 23 |

|    | 4.7.3 Timing Exceptions Constraints               | . 24 |

|    | 4.7.4 Operating Conditions Constraints            | . 28 |

|    | 4.7.5 Reports                                     | . 29 |

|    | 4.7.6 Other Constraints                           | . 37 |

|    | 4.7.7 Save                                        | . 38 |

|    | 4.8 Priority of Timing Constraints                | . 39 |

| 5  | Timing Report                                     | 40   |

|    | 5.1 Timing Summaries                              | . 40 |

|    | 5.1.1 STA Tool Run Summary                        | . 41 |

|    | 5.1.2 Clock Summary                               | . 42 |

|    | 5.1.3 Max Frequency Summary                       | . 42 |

|    | 5.1.4 Total Negative Slack Summary                | . 43 |

|    | 5.2 Timing Details                                | . 43 |

|    | 5.2.1 Path Slacks Table                           | . 43 |

|    | 5.2.2 Minimum Pulse Width Table                   | . 44 |

|    | 5.2.3 Timing Report By Analysis Type              | . 45 |

|    | 5.2.4 Minimum Pulse Width Report                  | . 50 |

|    | 5.2.5 High Fanout Nets Report                     | . 51 |

|    | 5.2.6 Route Congestions Report                    | . 51 |

|    | 5.2.7 Timing Exceptions Report                    | . 52 |

|    | 5.2.8 Timing Constraints Report                   | . 55 |

| Ap | opendix A Timing Constraints Syntax Specification | 56   |

|    | A.1 Clock Constraints                             | . 56 |

|    | A.1.1 create_clock                                | . 56 |

|    | A.1.2 create_generated_clock                      | . 58 |

|    | A.1.3 set_clock_latency                           | . 60 |

|    | A.1.4 set_clock_uncertainty                       | . 61 |

|    | A.1.5 set_clock_groups                            | . 63 |

|    | A.2 I/O Delay Constraints                         | . 63 |

|    | A.2.1 set_input_delay                             | . 63 |

|    | A.2.2 set_output_delay                            | . 64 |

|    | A.3 Timing Path Constraints                       | . 66 |

|    | A.3.1 set_max_delay/ set_min_delay                | . 66 |

|    | A.3.2 set_false_path                              | . 68 |

|    | A.3.3 set_multicycle_path                         | . 69 |

| A.4 Operating Conditions Constraints | 71 |

|--------------------------------------|----|

| A.5 Timing Report Constraints        | 72 |

| A.5.1 report_timing                  | 72 |

| A.5.2 report_high_fanout_nets        | 73 |

| A.5.3 report_route_congestion7       | 74 |

| A.5.4 report_min_pulse_width7        | 75 |

| A.5.5 report_max_frequency7          | 76 |

| A.5.6 report_exceptions              | 76 |

| A.6 Other Constraints                | 77 |

| A.6.1 derive_clocks                  | 77 |

## **List of Figures**

| Figure 3-1 Basic Model Diagram                            | . 4  |

|-----------------------------------------------------------|------|

| Figure 3-2 Four Types of Timing Paths                     | . 5  |

| Figure 4-1 New Dialog Box                                 | . 8  |

| Figure 4-2 New Timing Constraints File                    | . 8  |

| Figure 4-3 Open Timing Constraints File                   | . 9  |

| Figure 4-4 Add Constraints File                           | . 10 |

| Figure 4-5 Timing Constraint Editor Interface             | . 11 |

| Figure 4-6 Netlist Tree View                              | . 11 |

| Figure 4-7 Constraints Editing Window                     | . 12 |

| Figure 4-8 New Constraint                                 | . 12 |

| Figure 4-9 Open Timing Constraint                         | . 13 |

| Figure 4-10 Open Timing Constraints Window via Menu Bar   | . 13 |

| Figure 4-11 Right-click to Open Timing Constraints Window | . 13 |

| Figure 4-12 Edit SDC File                                 | . 14 |

| Figure 4-13 Create Clock                                  | . 15 |

| Figure 4-14 Select Objects                                | . 16 |

| Figure 4-15 Add Clock                                     | . 16 |

| Figure 4-16 Clock List                                    | . 17 |

| Figure 4-17 Right-click Menu for the Clock                | . 17 |

| Figure 4-18 Create Generated Clock Constraints            | . 18 |

| Figure 4-19 Select Create Generated Clock                 | . 19 |

| Figure 4-20 Set Clock Latency                             | . 20 |

| Figure 4-21 Set Clock Uncertainty                         | . 21 |

| Figure 4-22 Set Clock Groups                              | . 22 |

| Figure 4-23 Create I/O Delay Constraints                  | . 24 |

| Figure 4-24 Create False Path Constraints                 | . 25 |

| Figure 4-25 Create Max/Min Delay Constraints              | . 26 |

| Figure 4-26 Create Multicycle Path Constraints            | . 28 |

| Figure 4-27 Create Operating Conditions Constraints       | . 29 |

| Figure 4-28 Create Report Timing                          | . 30 |

|                                                           |      |

| Figure 4-29 Report Timing Dialog Box           | 31 |

|------------------------------------------------|----|

| Figure 4-30 Create Report High Fanout Nets     | 32 |

| Figure 4-31 Report High Fanout Nets Dialog Box | 32 |

| Figure 4-32 Report Route Congestion Interface  | 33 |

| Figure 4-33 Report Route Congestion Dialog Box | 33 |

| Figure 4-34 Create Report Min Pulse Width      | 34 |

| Figure 4-35 Report Min Pulse Width Dialog Box  | 35 |

| Figure 4-36 Create Report Max Frequency        | 35 |

| Figure 4-37 Report Max Frequency Dialog Box    | 36 |

| Figure 4-38 Create Report Exception            | 36 |

| Figure 4-39 Report Exception Dialog Box        | 37 |

| Figure 4-40 Create Derive Clocks               | 37 |

| Figure 4-41 Select Create Derive Clocks        | 38 |

| Figure 4-42 Derive Clocks List                 | 38 |

| Figure 5-1 Static Timing Analysis Report       | 40 |

| Figure 5-2 Timing Summaries                    | 41 |

| Figure 5-3 Path & Endpoints                    | 42 |

| Figure 5-4 Path Slacks Table                   | 44 |

| Figure 5-5 Minimum Pulse Width Table           | 45 |

| Figure 5-6 Path Summary                        | 46 |

| Figure 5-7 Data Arrival Path                   | 47 |

| Figure 5-8 Data Required Path                  | 47 |

| Figure 5-9 Path Statistics                     | 48 |

| Figure 5-10 Hold Analysis Report               | 48 |

| Figure 5-11 Recovery Analysis Report           | 49 |

| Figure 5-12 Removal Analysis Report            | 50 |

| Figure 5-13 Minimum Pulse Width                | 51 |

| Figure 5-14 High Fanout Nets Report            | 51 |

| Figure 5-15 Route Congestions Report           | 52 |

| Figure 5-16 Test Case                          | 52 |

| Figure 5-17 Timing Exceptions Constraints      | 52 |

| Figure 5-18 Timing Exceptions Report           | 53 |

| Figure 5-19 report_exception Statement         | 54 |

| Figure 5-20 report_exception Report            | 54 |

| Figure 5-21 Timing Constraints Report          | 55 |

## List of Tables

| Table 1-1 Terminology and Abbreviations         1 |

|---------------------------------------------------|

|---------------------------------------------------|

# **1** About This Guide

## 1.1 Purpose

This manual describes the timing constraints, including timing constraints editor usage, syntax definition and static timing analysis report (hereinafter referred to as timing report). It aims to help you realize timing constraints and how to read Static Timing Analysis (STA) reports.

## **1.2 Related Documents**

The latest user guides are available on GOWINSEMI Website: <u>www.gowinsemi.com</u> .You can find the related document <u>SUG918, Gowin</u> <u>Software Quick Start Guide</u>.

## **1.3 Terminology and Abbreviations**

Table 1-1 shows the abbreviations and terminology that are used in this manual.

#### **Table 1-1 Terminology and Abbreviations**

| Terminology and Abbreviations | Meaning                    |

|-------------------------------|----------------------------|

| GUI                           | Graphical User Interface   |

| MPW                           | Minimum Pulse Width        |

| OSC                           | Oscillator                 |

| PnR                           | Placement and Route        |

| REG                           | Register                   |

| SDC                           | Synopsys Design Constraint |

| STA                           | Static Timing Analysis     |

## **1.4 Support and Feedback**

Gowin Semiconductor provides customers with comprehensive technical support. If you have any questions, comments, or suggestions, please feel free to contact us directly using the information provided below.

Website: www.gowinsemi.com

E-mail: support@gowinsemi.com

# **2** Introduction

This manual includes three parts: STA, Timing Constraint Editor and Timing Report.

STA introduces the basic concepts, which is intended to help you understand the basic principles of timing analysis, learn timing constraints editor usage and read timing reports.

The timing constraints editor is a GUI tool that can create and modify SDC file, and a timing report is generated according to the timing constraints after Place and Route.

#### Function

- Supports clock constraints, such as base clock, generated clock constraints, source delay and uncertainty constraints and group constraints

- Supports the input and output delay constraints of data port

- Supports exception constraints, such as multi-cycle, maximum and minimum path delay constraints, and false path constraints

- Supports the report constraints, such as the max. frequency of the module and route congestion of grid

- Provides efficient netlist lookup and expression matching

- The GUI is flattened, simple and clear

#### Feature

- Strictly follows the W3C XHTML 1.0 specification

- Can be opened with an external browser

- Can be printed in TXT format

- Supports navigation bar and quick positioning

- Reports all constraints generated by timing constraints editor

- Easy to read with clear hierarchy

# $3_{\rm STA \, Overview}$

## 3.1 Overview

STA comprehensively analyzes the timing model in netlist, calculates the timing delay and determines whether it meets the requirements. The designer needs to provide constraint incentives, and Gowin Software completes the analysis automatically. Compared with the traditional analysis method, it features short verification time and high coverage.

The basic models, terms and concepts involved in STA are described below.

## 3.2 Basic Model

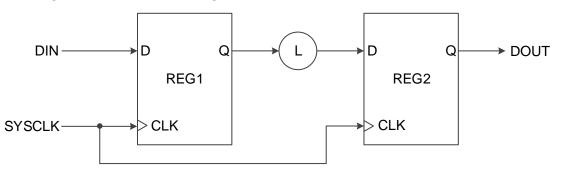

STA is a model analysis that starts from and ends with the timing component. The basic model diagram is shown in Figure 3-1. The REG1 triggers data from D to Q at the active edge. The data arrives at REG2 via logic circuit. Then the REG2 captures the data transmitting from REG1 at the active edge. STA is employed to verify whether REG2 can capture the data from the REG1 correctly.

Figure 3-1 Basic Model Diagram

The active edge of REG1 is called launch edge, and the active edge of REG2 is called latch edge.

## 3.3 Terms

The basic timing units involved in the timing model are as follows:

- Cells: Basic logic such as LUT, DFF, MUX, etc.

- Pins: I/O port of cells

- Ports: I/O ports of top-level module

- Nets: net

## 3.4 Path

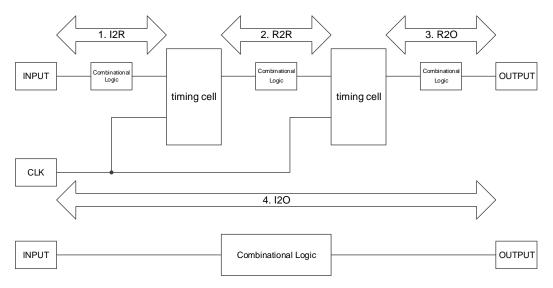

STA usually analyzes four types of paths and classifies them according to different starts and ends, as shown in Figure 3-2.

- I2R: From input to timing cell

- R2R: From timing cell to timing cell

- R2O: From timing cell to output

- I2O: From input to output.

Figure 3-2 Four Types of Timing Paths

Gowin Software calculates the data arrival time and data required time of each path.

The data arrival time refers to the time from the start to the end of the data path. The data required time refers to the time from the clock start to the end in the timing path. When calculating data arrival time, clock path has a clock skew which refers to the time difference of the clock arriving at the clock port of different timing components.

## 3.5 Common Timing Checks

STA usually check the following three types of timing and provides suggestions on PnR to better meet your requirements for timing.

## 3.5.1 Setup Time and Hold Time Check

- Setup time: The shortest time for data stability before the active edge. If the time is not met, the clock cannot capture data.

- Hold time: The shortest time for data stability after clock effective edge, if the time is not met, the clock cannot capture data.

### 3.5.2 Recovery Time and Removal Time Check

- Recovery time: Before active edge, the shortest stability time for removing asynchronous set/reset signal. If the time is not met, the flip flop may not operate.

- Removal time: After active edge, the shortest stability time for removing asynchronous set/reset signal, if the time is not met, the flip flop may not operate.

### 3.5.3 MPW Check

MPW: Min. width of high and low level recognized by flip flop, such as DFF. The clock will not be recognized if the width is lower than MPW.

# **4** Timing Constraints Editor

## 4.1 Overview

Gowin Timing Constraints Editor supports timing commands, including clock, input/output, path constraints, and clock report. You can add timing constraints via GUI. For a simple example, see <u>SUG918, Gowin Software</u> <u>Quick Start Guide</u>.

## 4.2 Start Timing Constraints Editor

You can use the Timing Constraints Editor alone or start it after synthesis.

Click "Tools > Timing Constraints Editor" to start. After running Synthesize in Process window, double-click "Process > Timing Constraints Editor" to start the timing constraints editor. The netlist file and the timing constraints file in the project are automatically loaded into the timing constraint editor, or created automatically if there is no timing constraint file in the project.

## 4.3 Create/Open/Add Constraints File

### 4.3.1 Create Constraints File

The steps of creating constraint files are as follows.

- 1. Click "File > New" and "New" dialog box pops up.

- 2. Select "Timing Constraints File", as shown in Figure 4-1.

#### Note!

You can also create constraints file in the following ways.

- Click the "New" icon in the toolbar.

- Use shortcut "Ctrl+N".

Figure 4-1 New Dialog Box

| 🐝 New                             | ?    | ×  |

|-----------------------------------|------|----|

|                                   |      |    |

| ✓ Projects                        |      |    |

| FPGA Design Project               |      |    |

| ✓ Files                           |      |    |

| 📑 Verilog File                    |      |    |

| 📑 VHDL File                       |      |    |

|                                   |      |    |

| 📑 Timing Constraints File         |      |    |

| 📑 GowinSynthesis Constraints File |      |    |

| 📑 User Flash Initialization File  |      |    |

| GAO Config File                   |      |    |

| GPA Config File                   |      |    |

| 📑 Memory Initialization File      |      |    |

| Create a Timing Constraints file. |      |    |

|                                   |      |    |

|                                   |      |    |

|                                   |      |    |

| OK                                | Cano | el |

3. Click "OK" and "New Timing Constraints File" pops up, as shown in Figure 4-2.

Figure 4-2 New Timing Constraints File

| 🐝 New T    | iming Constraints File | ?     | ×   |

|------------|------------------------|-------|-----|

| Name:      | Enter a name           | .sdc  | •   |

| Create in: | E:\gowinProj\bitTest   | Brows | e   |

|            | Add to current project |       |     |

|            | OK                     | Can   | cel |

- 4. Type the file name and select a path, then click "OK", and the created constraints file is automatically loaded into the project.

- Name: The new file name with .sdc extension; and the name is recommended to use identifiers with engineering-related meaning,

beginning with letters or underscores.

- Create in: Select the path by clicking "Browse" and it is stored in src folder in project by default.

- Add to current project: Add the constraints file to the project automatically.

#### 4.3.2 Open Constraints File

The steps are as follows.

- 1. On IDE interface, click "File > Open".

- 2. "Open File" dialog box pops up, as shown in Figure 4-3.

#### Note!

You can also open timing constraints file in the following ways:

- Click "Open" icon in the toolbar;

- Use shortcut "Ctrl + O".

#### Figure 4-3 Open Timing Constraints File

| 🐳 Open File         |                                |                   |              |             |           | >      |

|---------------------|--------------------------------|-------------------|--------------|-------------|-----------|--------|

| ← → × ↑ 📙 « ge      | owinProj > fpga_project_4 > si | rc ~ Ö            | Search src   |             |           | Q      |

| Organize 🔻 New fold | ler                            |                   |              |             |           | ?      |

| 3D Objects ^        | Name                           | Date modified     | Туре         | Size        |           |        |

| Desktop             | gowin_clkdiv                   | 6/3/2020 6:11 PM  | File folder  |             |           |        |

| Documents           | 📔 fpga_project_4.sdc           | 6/4/2020 10:58 AM | SDC File     |             | 1 KB      |        |

| 🕂 Downloads         |                                |                   |              |             |           |        |

| 👌 Music             |                                |                   |              |             |           |        |

| Pictures            |                                |                   |              |             |           |        |

| Videos              |                                |                   |              |             |           |        |

| 🏪 Local Disk (C:)   |                                |                   |              |             |           |        |

| 👝 Local Disk (D:)   |                                |                   |              |             |           |        |

| 👝 Local Disk (E:)   |                                |                   |              |             |           |        |

| 👝 Local Disk (F:)   |                                |                   |              |             |           |        |

| 👝 Local Disk (G:)   |                                |                   |              |             |           |        |

| 💣 Network           |                                |                   |              |             |           |        |

| Ŷ                   |                                |                   |              |             |           |        |

| File <u>r</u>       | ame: fpga_project_4.sdc        | ~                 | GOWIN Tim    | ing Constra | aint File | $\sim$ |

|                     |                                |                   | <u>O</u> pen |             | Cancel    |        |

3. Select and open the file with.sdc extension.

#### Note!

The file open operation does not automatically load the file into the project.

## 4.3.3 Add Constraints File

The steps are as follows.

- 1. Right-click and select "Add Files" in Design window.

- 2. "Select Files" dialog box pops up, and select the file with .sdc extension, as shown in Figure 4-4.

- 3. Click "Open" to add one or more selected files to the project.

#### Note!

Only one file is valid when multiple files added.

#### Figure 4-4 Add Constraints File

| 🐳 Select Files                               |                             |                            |                  |               |             |            | ×      |

|----------------------------------------------|-----------------------------|----------------------------|------------------|---------------|-------------|------------|--------|

| $\leftrightarrow$ $\rightarrow$ $\checkmark$ | <ul> <li>This PC</li> </ul> | > Desktop > net_port > src | ~                | ල් Search src |             |            | 9      |

| Organize 🔻 Ne                                | w folder                    |                            |                  |               |             |            | ?      |

| 🖈 Quick access                               | ^ N                         | ame ^                      | Date modified    | Туре          | Size        |            |        |

| Vulce access                                 |                             | 🖌 demo.sdc                 | 2021/10/11 15:51 | SDC File      |             | 1 KB       |        |

| 2021-08                                      |                             |                            |                  |               |             |            |        |

| 19801                                        |                             |                            |                  |               |             |            |        |

| 🔥 temp                                       |                             |                            |                  |               |             |            |        |

| 💻 This PC                                    |                             |                            |                  |               |             |            |        |

| 🧊 3D Objects                                 |                             |                            |                  |               |             |            |        |

| 📃 Desktop                                    |                             |                            |                  |               |             |            |        |

| Documents                                    |                             |                            |                  |               |             |            |        |

| 👆 Downloads                                  |                             |                            |                  |               |             |            |        |

| 👌 Music                                      |                             |                            |                  |               |             |            |        |

| Pictures                                     | ~                           |                            |                  |               |             |            |        |

|                                              | File name:                  | demo.sdc                   |                  | ✓ GOWIN Tim   | ing Constra | iints File | $\sim$ |

|                                              |                             |                            |                  | Open          |             | Cancel     |        |

## 4.4 Timing Constraints Editor Interface

The editor interface is shown in Figure 4-5.

| 👾 Gowin Timing Constraints Editor - E:, | /8bit c | ounter/src/8bit counter.sdc |            |      |        |           | _    |      | ×    |

|-----------------------------------------|---------|-----------------------------|------------|------|--------|-----------|------|------|------|

| File Constraints Reports View He        | -       |                             |            |      |        |           |      |      |      |

|                                         | -ip     |                             |            |      |        |           |      |      |      |

|                                         | đΧ      | Timing Constraints          | Clock Name | Туре | Period | Frequency | Rise | Fall |      |

|                                         |         | <ul> <li>Clocks</li> </ul>  |            |      |        |           |      |      |      |

| iiii 😻                                  | Q       | Clock Latency               | base       | Base | 10ns   | 100MHz    | 0    | 5    |      |

| ✓ Se counter1                           |         | Clock Uncertainty           |            |      |        |           |      |      |      |

| > 📒 Ports (22)                          |         | Clock Group                 |            |      |        |           |      |      |      |

| > 🚞 Nets (60)                           |         | I/O Delay                   |            |      |        |           |      |      |      |

| > 🚞 Primitives (50)                     |         | ✓ Path                      |            |      |        |           |      |      |      |

|                                         |         | False Path                  |            |      |        |           |      |      |      |

|                                         |         | Max/Min Delay               |            |      |        |           |      |      |      |

|                                         |         | Multicycle Path             |            |      |        |           |      |      |      |

|                                         |         | ✓ Report                    |            |      |        |           |      |      |      |

|                                         |         | Report Timing               |            |      |        |           |      |      |      |

|                                         |         | Report High Fanout Nets     |            |      |        |           |      |      |      |

|                                         |         | Report Route Congestion     |            |      |        |           |      |      |      |

|                                         |         | Report Min Pulse Width      |            |      |        |           |      |      |      |

|                                         |         | Report Max Frequency        |            |      |        |           |      |      |      |

|                                         |         | Report Exception            |            |      |        |           |      |      |      |

|                                         |         | Set Operating Conditions    |            |      |        |           |      |      |      |

|                                         |         | ✓ Others                    |            |      |        |           |      |      |      |

|                                         |         | Create Derive Clocks        | <          |      |        |           |      |      |      |

| Console                                 |         |                             |            |      |        |           |      |      | đΧ   |

|                                         |         |                             |            |      |        |           |      |      | _ // |

|                                         |         |                             |            |      |        |           |      |      |      |

|                                         |         |                             |            |      |        |           |      |      |      |

|                                         |         |                             |            |      |        |           |      |      |      |

|                                         |         |                             |            |      |        |           |      |      |      |

|                                         |         |                             |            |      |        |           |      |      |      |

|                                         |         |                             |            |      |        |           |      |      |      |

**Figure 4-5 Timing Constraint Editor Interface**

The Netlist Tree view is as shown in Figure 4-6.

**Figure 4-6 Netlist Tree View**

The Netlist Tree includes Top Module, I/O Ports, Nets, and Primitives.

"100 ": Hierarchy display

The constraints editing area is as shown in Figure 4-7. The left is the timing constraints type and the right is the editing area. Click a constraints

type, and the constraints editing list will be displayed in editing area.

**Figure 4-7 Constraints Editing Window**

| Timing Constraints       | Clock Name | Туре | Period | Frequency | Rise | Fall |   |

|--------------------------|------------|------|--------|-----------|------|------|---|

| ✓ Clocks                 | base       | Base | 10ns   | 100MHz    | 0    | 5    |   |

| Clock Latency            |            |      |        |           | _    | _    |   |

| Clock Uncertainty        |            |      |        |           |      |      |   |

| Clock Group              |            |      |        |           |      |      |   |

| I/O Delay                |            |      |        |           |      |      |   |

| ✓ Path                   |            |      |        |           |      |      |   |

| False Path               |            |      |        |           |      |      |   |

| Max/Min Delay            |            |      |        |           |      |      |   |

| Multicycle Path          |            |      |        |           |      |      |   |

| ✓ Report                 |            |      |        |           |      |      |   |

| Report Timing            |            |      |        |           |      |      |   |

| Report High Fanout Nets  |            |      |        |           |      |      |   |

| Report Route Congestion  |            |      |        |           |      |      |   |

| Report Min Pulse Width   |            |      |        |           |      |      |   |

| Report Max Frequency     |            |      |        |           |      |      |   |

| Report Exception         |            |      |        |           |      |      |   |

| Set Operating Conditions |            |      |        |           |      |      |   |

| ✓ Others                 |            |      |        |           |      |      |   |

| Create Derive Clocks     | <          | _    |        |           |      |      | > |

" " to open "New Constraint" dialog box, you can configure "Input Netlist File" and "Device", as shown in Figure 4-8.

Figure 4-8 New Constraint

| 🐝 New Constraint    |    | ?      | ×  |

|---------------------|----|--------|----|

| Input Netlist File: |    | Brows  | e  |

| Device:             |    | Select | t  |

|                     | OK | Cano   | el |

Click " to open "Open Timing Constraint" dialog box, you can configure "Input Netlist File", "Constraint File", and "Device", as shown in Figure 4-9.

#### Figure 4-9 Open Timing Constraint

| 🐳 Open Timing Constraint |    | ?     | ×  |

|--------------------------|----|-------|----|

| Input Netlist File:      |    | Brows | e  |

| Constraint File:         |    | Brows | e  |

| Device:                  |    | Selec | t  |

|                          | OK | Cano  | el |

## 4.5 Open Timing Constraints Window

There are two ways to open.

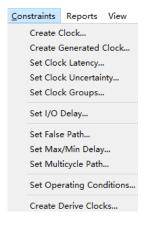

1. Click "Constraints" in menu. Select timing constraints command to open the window, as shown in Figure 4-10.

Figure 4-10 Open Timing Constraints Window via Menu Bar

2. Right click to select different timing constraints commands, as shown in Figure 4-11.

#### Figure 4-11 Right-click to Open Timing Constraints Window

| Timing Constraints       | Clock Name | Туре | Period | Frequency       | Rise     | Fall |

|--------------------------|------------|------|--------|-----------------|----------|------|

| Y Clocks                 | base       | Base | 10ns   | 100МЦ-          |          | 5    |

| Clock Latency            |            |      |        | Remove          |          |      |

| Clock Uncertainty        |            |      |        | Set Clock Laten |          |      |

| Clock Group              |            |      |        |                 | · ·      |      |

| I/O Delay                |            |      |        | Set Clock Uncer | rtainty  |      |

| ✓ Path                   |            |      |        | Set I/O Delay   |          |      |

| False Path               |            |      |        | Set Clock Grou  | ps       |      |

| Max/Min Delay            |            |      |        | Create Clock    |          |      |

| Multicycle Path          |            |      |        | Create Generat  | ed Clock |      |

| ✓ Report                 |            |      | _      |                 |          |      |

| Report Timing            |            |      |        |                 |          |      |

| Report High Fanout Nets  |            |      |        |                 |          |      |

| Report Route Congestion  |            |      |        |                 |          |      |

| Report Min Pulse Width   |            |      |        |                 |          |      |

| Report Max Frequency     |            |      |        |                 |          |      |

| Report Exception         |            |      |        |                 |          |      |

| Set Operating Conditions |            |      |        |                 |          |      |

| ✓ Others                 |            |      |        |                 |          |      |

| Create Derive Clocks     |            |      |        |                 |          |      |

|                          | <          |      |        |                 |          |      |

## 4.6 Edit SDC File

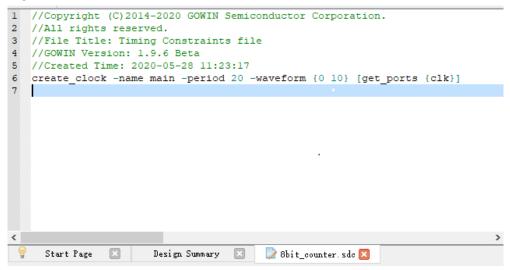

Gowin Software supports to read SDC file and you can manually modify the SDC file in the timing constraints editor, as shown in Figure 4-12.

The parsing of SDC files supports wildcard; currently two wildcard characters "\*" and "?" are supported. "\*" matches zero or multiple characters, while "?" matches a single character.

SDC files support single line and multi-line comments. Single line comments use "//" or "#", and multi-line comments use "/\* \*/".

#### Figure 4-12 Edit SDC File

## 4.7 Create Timing Constraints

This section introduces how to create timing constraints using editor. The created timing constraints will be written to the SDC file in the project. You can see <u>Appendix A</u> for details.

#### 4.7.1 Clock Constraints

#### **Create Clock**

- You can configure parameters, such as name, period, frequency, rising edge, falling edge, etc.

- Gowin Software can create multiple clocks which form multiple clock domains, and support clock domain crossing analysis.

Create\_clock can create a base clock for user design.

You can add clock constraints in the following two ways.

1. Add Clock constraint via Constraints

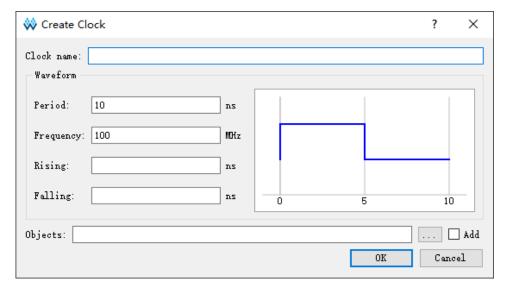

a) Select "Constraints > Create Clock... ", and the "Create Clock" dialog box pops up, as shown in Figure 4-13.

Figure 4-13 Create Clock

b) Configure "Clock Name", "Waveform", and "Objects".

- Clock Name: Supports identifiers beginning with letters or underscores.

- Period: Floating point greater than 0, accurate to three decimal places, unit in ns, and 10 by default.

- Frequency: Floating point greater than 0, accurate to three decimal places, unit in MHz, and 100 by default.

- Rising: Floating point greater than 0, accurate to three decimal places, unit in ns.

- Falling: Floating point greater than 0, accurate to three decimal places, unit in ns.

- Objects: Specifies the target; click ", to select the object.

- Add: Checks it when adding multiple clocks to the same source.

- c) Click " and " Select Objects" pops up, as shown in Figure 4-14.

| 🐝 Select Ob  | jects               |              |          |          | ?     | ×    |

|--------------|---------------------|--------------|----------|----------|-------|------|

| Collection:  | get_ports 🔻 Filter: | *            |          |          | 🔎 Se: | arch |

| -Matches & S | Gelected            |              |          |          |       |      |

| O matches    | found               |              | 0 select | ed names |       |      |

|              |                     | ><br>>><br>< |          |          |       |      |

|              |                     |              |          | OK       | Canc  | el   |

Figure 4-14 Select Objects

- d) As shown in Figure 4-14, "Collection" specifies the object type. "Filter" is a filter. After clicking "Search", the objects are displayed on the left, and the selected will be displayed on the right. ">" adds the selected from the left list to the right list. "> >" adds all the selected from the left list to the right list. "> " adds all the selected from the left list to the right list. "<" removes the selected in the right list. "< <" removes all the selected in the right list.</p>

- e) Click "OK" to add Objects.

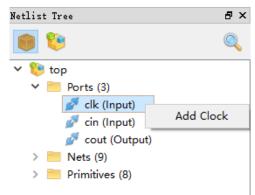

- 2. Add clock constraints via Netlist Tree.

- a) Select I/O Port or Net in Netlist Tree.

- b) Right-click and select "Add Clock" to add a clock, as shown in Figure 4-15.

Figure 4-15 Add Clock

After finishing, the constraints will be added in clock list, as shown in Figure 4-16.

Figure 4-16 Clock List

| 10ns 10 |       | Rise       | Fall         | Divide by       | Multiply by         | Duty cycle              | Phase                       | Offset                          |

|---------|-------|------------|--------------|-----------------|---------------------|-------------------------|-----------------------------|---------------------------------|

| 10ns 10 | 00MHz | 0          | 5            | N/A             | N/A                 | N/A                     | N/A                         | N/A                             |

| 20ns 5  | 50MHz | 0          | 10           | N/A             | N/A                 |                         | N/A                         |                                 |

|         | 20ns  | 20ns 50MHz | 20ns 50MHz 0 | 20ns 50MHz 0 10 | 20ns 50MHz 0 10 N/A | 20ns 50MHz 0 10 N/A N/A | 20ns 50MHz 0 10 N/A N/A N/A | 20ns 50MHz 0 10 N/A N/A N/A N/A |

You can perform the following operations.

- Double-click the constraints to edit.

- Right-click and select "Remove" to remove the clock.

- Right-click to set Clock Latency, Clock Uncertainty, or I/O Delay, as shown in Figure 4-17.

#### Figure 4-17 Right-click Menu for the Clock

| Clock Name | Туре | Period                                                     | Frequency          | Rise | Fall | Divide by | Multiply by | Duty cyc |

|------------|------|------------------------------------------------------------|--------------------|------|------|-----------|-------------|----------|

| clk1       | Base | 10ns                                                       | 100MHz             | 0    | 5    | N/A       | N/A         | N/A      |

| clk2       | Base | 20pc 50MHz<br>Remove                                       |                    | 0    | 10   | N/A       | N/A         | N/A      |

|            |      | Set Clock Li<br>Set Clock U<br>Set I/O Dela<br>Set Clock G | Incertainty<br>ay  |      |      |           |             |          |

|            |      | Create Cloc<br>Create Gen                                  | :k<br>erated Clock |      |      |           |             |          |

#### Note!

- When a constraint is inconsistent with the PLL configuration, you should take the one created by Create Clock as the standard. A prompt will pop up in PnR.

- Create Clock does not support virtual clock.

#### **Create Generated Clock**

- Create generated clock according to the base clock;

- You can create generated clock based on the frequency division, frequency multiplication, phase and duty cycle of the base clock.

The generated clock must be based on the base clock and you can create at any node in the user design. They are usually applied to the output ports of PLL, CLKDIV and other hard cores. If you use PLL in the design, after the base clock is created, the generated clock with Objects as PLL. CLKOUT and Source as the base clock can be created. The generated clock is automatically linked to the base clock, and the generated clock is automatically corrected to adapt to the base clock when

the attributes of the base clock change.

You can create the generated clock in the following two ways:

- 1. Create via Constraints

- a) Select "Create Generated Clock" and "Create Generated Clock" pops up, as shown in Figure 4-18.

- Clock Name: Supports identifiers beginning with letters or underscores.

- Source: The source of generated clock; click ", to select one.

- Master Clock: The clock acting on Source; click " " to select one.

Figure 4-18 Create Generated Clock Constraints

| 关 Create Gen  | erated Clock |         |       |                | ? ×    |

|---------------|--------------|---------|-------|----------------|--------|

| Clock Name:   |              |         |       |                |        |

| Source:       |              |         |       |                |        |

| Master Clock: |              |         |       |                | ~      |

| Relationship  |              |         |       |                |        |

| Based on      | frequency    |         |       |                |        |

| Divide by     |              | Phase:  |       |                |        |

| Multiply      | by:          | Offset: |       |                |        |

| Duty cycl     | e:           |         |       |                |        |

| 🔘 Based on    | waveform     |         |       |                |        |

| Edge list     | :            |         |       |                |        |

| Edge shif     | t list:      | ns      | ns    | ns             |        |

| 🗌 Invert wa   | veform       |         | 🗌 Add |                |        |

|               |              |         |       |                |        |

| Objects:      |              |         |       |                |        |

|               |              |         |       |                |        |

|               |              |         |       |                |        |

|               |              |         |       |                |        |

|               |              |         |       |                |        |

|               |              |         |       |                |        |

|               |              |         |       |                |        |

| 0             | 5            | 10      | 0     | 5              | 10     |

| 2             | Source clock |         | 0     | enerated clock |        |

|               |              |         |       | OK             | Cancel |

- b) You can automatically add the clock associated with Source to "Master Clock" by clicking "..." on the right side of "Source"; when Master Clock has multiple clocks, only one of them is supported.

- c) In "Relationship to source" pane, you can configure frequency division/multiplication, offset, duty cycle and phase in "Based on frequency"; and you can also adjust edge in "Based on waveform".

- Divide by: Division, positive integer.

- Phase: Floating point accurate to three decimal places, with negative values indicating left shift and positive values indicating right shift.

- Multiply by: Multiplication, positive integer.

- Offset: Floating point accurate to three decimal places, with negative values indicating left shift and positive values indicating right shift.

- Duty cycle: Floating point accurate to three decimal places; value not greater than 100.

- Edge list: Positive integer increased sequentially.

- Edge shift list: Floating point accurate to three decimal places.

- d) You can invert clocks by clicking "Invert waveform" and add clocks by clicking "Add".

- e) In "Objects", click "....." and "Select Objects" pops up to select the object.

#### Note!

- If there is no clock in Source, Master Clock has no option, and you need to select Source again.

- When a constraint is inconsistent with the PLL configuration, you should take the one created by Create Generated Clock as the standard. A prompt will pop up in PnR.

- 2. Create generated clock from clocks list. Right-click and select "Create Generated Clock" to create generated clock, as shown in Figure 4-19.

#### Figure 4-19 Select Create Generated Clock

The new constraints will be added.

You can perform the following operations.

- Double-click the constraints to edit.

- Select the clock and right-click to select "Remove" to remove the clock.

#### Set Clock Latency

- It is used to set the latency before clock signal reaching device port. You can configure the max./min. latency respectively for rising /falling edges.

- Clock latency includes two types: network latency and source latency.

- Network latency is internal clock path delay.

- Source latency is external clock path delay.

- Gowin Software will calculate clock network latency automatically, so you only need to set source latency.

The latency of the clock signal from the clock source (external crystal oscillator) to the FPGA clock port is called the source latency, which is not automatically known by Gowin Software. The default value is 0ns. If you know the source latency 2ns, the Delay Value can be configured as of 2ns, and Gowin Software will add 2ns value automatically in timing analysis. The results can be found in Tcl of the Setup and Hold reports.

You can create clock latency constraints in the following two ways.

- 1. Select "Set Clock Latency" in "Constraints" menu, and Set Clock Latency dialog box pops up, as shown in Figure 4-20.

- Early and Late: Indicates whether the setting is minimum or maximum latency. Late is used for Setup analysis and Early is used for Hold analysis. Both is used for Setup and Early analysis.

- Rise and Fall are valid for rising edge and falling edge; Both indicates Rise and Fall both are valid.

- Objects: Specifies the clock input port or clock; select one by clicking ".....".

Figure 4-20 Set Clock Latency

| 关 Set Clock Late | ency   |      | ?      | × |

|------------------|--------|------|--------|---|

| Latency type     |        |      |        |   |

| O Early C        | ) Late | Soth |        |   |

| O Rise O         | ) Fall | Soth |        |   |

| Delay value:     |        | ns   |        |   |

| Objects:         |        |      |        |   |

| Clocks:          |        |      |        |   |

|                  |        | OK   | Cance. | 1 |

Create Clock Latency constraints in clocks list. Select a clock in clock list; right-click and select Set Clock Latency; this clock will be automatically selected in Objects.

Set Clock Uncertainty

• Set Clock Uncertainty is used to set clock uncertainty or offset to

analyze clock transmission.

- It can set uncertainty for setup and hold, or clock rising edge and falling edge.

- You can inform Gowin Software of clock jitter, pessimistic, etc. via the constraints to affect timing.

An ideal clock signal does not generate uncertainty. However, the clock uncertainty usually exists, and Gowin Software will calculate the uncertainties by default. You can also provide a more reasonable uncertainties according to the actual hardware environment to Gowin Software for analysis. Assuming that the device works in a strong magnetic environment and the uncertain value is 0.2ns, then Uncertainty can be set as 0.2ns. The results can be found in tUnc of the Setup and Hold reports.

The steps to create clock uncertainty are as follows.

- 1. In "Constraints", select "Set Clock Uncertainty" and "Set Clock Uncertainty" pops up, as shown in Figure 4-21.

- From clock: Specifies the start clock, selected by clicking " ~ " on the right.

- To clock: Specifies the end clock, selected by clicking " ~ " on the right.

- Uncertainty: Floating point accurate to three decimal places, unit in ns.

- Analysis type: Indicates the type of analysis.

Figure 4-21 Set Clock Uncertainty

| 关 Set Clock Uncertainty | ? ×           |

|-------------------------|---------------|

| From clock:  To clock:  | ~             |

| Uncertainty:ns          | Analysis type |

|                         | OK Cancel     |

- 2. Select in From type and To type on the left, select clocks on the right.

- 3. Click "OK" to add uncertainty.

#### Set Clock Group

- It used to specify the relationship between different clocks.

- Gowin Software provides the relationship between the group members

by default, and there is no correlation between groups.

• Gowin Software defaults to the fact that all clocks in the deisgn belong to a group and are related.

The constraint is usually used for mutual exclusive or asynchronous clocks. For example, there are CLK1 and CLK2 with different frequencies in the design, and only one clock is valid at the same time via a multiple-selection.

It is recommended that you specify the relationship between clocks and create clock group constraints for asynchronous or mutually exclusive clocks.

You can create clock group in the following ways.

- 1. In "Constraints", select "Set Clock Groups" and "Set Clock Groups" dialog box pops up, as shown in Figure 4-22.

- Group: Specifies the clock, at least one clock, selected by clicking

"...." on the right.

- Add: Add a group.

- Set Mutex Clocks: Sets multiple groups at one time.

- Exclusive: Indicates clocks are exclusive. For example, Clock0 and Clock1 pass through a MUX2 and outputs Clock3 acting on a timing model, and Clock3 can only take Clock0 and Clock1 at the same time; then you can check this option.

- Asynchronous: Indicates that clock asynchronization is not related, and the clock has different clock sources. For example, a timing model is transmitted and sampled by Clock0 and Clock1, which can be from different external ports.

Figure 4-22 Set Clock Groups

| 🐳 Set Clock Groups         | ?     | ×  |

|----------------------------|-------|----|

| Group:                     |       |    |

| Group:                     |       |    |

| Group:                     |       | ×  |

|                            | 🕂 📥   | d  |

| • Exclusive O Asynchronous |       |    |

| OK                         | Cance | .l |

3. Click "OK" to save.

#### Note!

The options "Exclusive" and "Asynchronous" achieve the same result.

## 4.7.2 I/O Delay Constraints

#### set\_input\_delay

Set the delay value of data input, and you analyze the relationship between data arrival and clock arrival; users need to set a reasonable input delay value, and Gowin Software will analyze the slack based on the given delay value.

#### Note!

The input delay type in the timing report is "tln".

#### set\_output\_delay

Set the delay value of data output, and you analyze the relationship between data output and clock output; users need to set a reasonable output delay value, and Gowin Software will analyze the slack based on the given delay value.

#### Note!

The output delay type in the timing report is "tOut".

You can create I/O delay constraints as follows.

- 1. In "Constraints" menu, select "Set I/O Delay" and "Set I/O Delay" dialog box pops up, as shown in Figure 4-23.

- Clock name: Indicates the clock associated with I/O; the clock must exist, and click " " to select it.

- Options: Configure delay type, maximum and minimum delay, clock edge, etc.

- Input delay/Output delay: Specifies the input/output delay, and they are exclusive.

- Minimum/Maximum: Specifies the minimum or maximum delay value of I/O; both indicate that both delay values are the same.

- Rise/Fall: Indicates that rising or falling edge is valid; both indicate that they are both valid at the same time.

- Delay value: Used to set the delay value for I/O, a positive or negative floating point accurate to three decimal places. When it is a negative number, it indicates an advance arrival, and when it is a positive number, it indicates a delayed arrival, measured in ns.

- Objects: Specifies the input and output ports, and click "....." on to

select one.

- Add delay: Used to add a delay value to the same port; when there are multiple delay values on the same port, Gowin Software will select the largest one for Setup analysis and the smallest one for Hold analysis; if this option is not specified, the same constraint on the same port will be overwritten.

- Use falling clock edge: If checked, the falling edge of the associated clock is related; the default is rising edge related.

- Source Latency include: If checked, it indicates that the delay value set includes the delay value of the clock; if not checked, Gowin Software will count in the delay value of the clock.

Figure 4-23 Create I/O Delay Constraints

| 🗱 Set I/O Delay                      |                          | ?    | $\times$ |

|--------------------------------------|--------------------------|------|----------|

| Clock name:<br>Options               |                          |      | ~        |

| ◉ Input delay ) Output delay         |                          |      |          |

| 🔿 Minimum 🔿 Maximum 💿 Both           |                          |      |          |

| 🔿 Rise 🔿 Fall 🖲 Both                 |                          |      |          |

| Add delay<br>Source latency included | 🗌 Use falling clock edge |      |          |

| Delay value:<br>Objects:             |                          |      |          |

|                                      | ОК                       | Cano | el       |

2. Click "OK" to save the constraints.

## 4.7.3 Timing Exceptions Constraints

Timing exceptions allow users to modify the default static timing analysis rules for a specific path. The timing exception constraint commands includes four types: set\_false\_path, set\_multicycle\_path, set\_max\_delay, and set\_min\_delay.

#### Set False Path

Gowin Software will analyze all timing paths. Set False Path specifies the paths in the design that do not need to be analyzed. It is recommended that users use this statement to specify a path that does not need to be analyzed.

There are usually two types of timing paths that do not require analysis.

- The timing circuit unrelated to operating, such as the test circuit.

- The path across the asynchronous clock domain. Assuming that there are register A and register B, A outputs data to B, and A and B are respectively driven by asynchronous clocks CLK1 and CLK2. Then From can be configured as CLK1 and To as CLK2, and the path from CLK1 launch to CLK2 latch will not be analyzed.

You can create False Path constraints as follows:

- 1. Select "Constraints > Set False Path", then "Set False Path" pops up, as shown in Figure 4-24.

- Analysis type: Checks Setup or Hold; Both indicate both are checked.

- From: Indicates the start of the path.

- To: Indicates the end of the path.

- Through: Indicates the pins or nets through the path.

#### Note!

From, To and Through can be used individually or together with each other.

| 关 Set False Path |                       | ?  | ×    |

|------------------|-----------------------|----|------|

| From:            |                       |    |      |

| Through:         |                       |    |      |

| To:              |                       |    |      |

| Analysis type:   | ○ Setup ○ Hold ④ Both |    |      |

|                  | ОК                    | Ca | ncel |

2. Click "....." to select objects, as shown in Figure 4-14. Click "OK" to save.

#### Set Max/Min Delay

Specify the maximum and minimum delay values on a path.

It is usually used in pin-to-pin delay analysis. If the input port A is output to port B after combinational logic, Gowin software does not analyze and report the path from port A to port B by default. You can use this constraint to specify a delay value from port A to port B. Gowin Software automatically calculates, analyzes and reports the path specified by you. The maximum delay is reported in Setup, and the minimum delay is reported in Hold.

You can create Max/Min Delay constraints as follows:

- 1. Select "Constraints > Set Max/Min Delay", then "Set Max/Min Delay" pops up, as shown in Figure 4-25.

- From: Indicates the start of the path; click "....." to select one.

- To: Indicates the end of the path; click ", to select one.

- Through: Indicates the pins or nets through the path; click "...." to select one.

- Delay value: Sets delay value; Floating point accurate to three decimal places.

- Delay value is the user-specified delay value, a floating point accurate to three decimal places, measured in ns.

#### Note!

From, To and Through can be used individually or together with each other.

Figure 4-25 Create Max/Min Delay Constraints

| 🐝 Set Max/Min Delay |        | ?  | ×      |

|---------------------|--------|----|--------|

| Delay type<br>Max   | () Min |    |        |

| From:               |        |    |        |

| Through:            |        |    |        |

| To:                 |        |    |        |

| Delay value:        |        |    | ns     |

|                     |        | OK | Cancel |

Select type (Max or Min) in Delay Type and select Objects in From/To. Click "OK" to save.

#### Set MultiCycle Path

By default, Gowin Software performs single-cycle clock analysis, that is, the check of setup time is on the active clock edge of the next clock cycle at the edge of the source clock, but this method does not apply to certain timing paths. Logic design circuit is the most typical example. More than one clock cycle data shall be needed to stabilize if a logic circuit calculates more complex or longer path.

If the data on the timing Path\_A in the design needs two cycles to stabilize, and Gowin Software defaults to the one cycle analysis. You need to set Value to 2, and Gowin Software can analyze according to the value. The results can be found in the Setup and Hold reports.

#### Note!

- Setting the multicycle path command will affect the setup time and the hold time. If the -setup or -hold option is not specified, Gowin Software defaults to -setup. If -setup value is set, hold value will not be affected.

- Gowin Software provides the function to automatically repair Hold by default. If you specify a hold value, Gowin Software will prioritize user setting.

You can create multicycle path constraints as follows:

- 1. Select "Constraints > Set Multicycle Path", then "Set Multicycle Path" pops up, as shown in Figure 4-26.

- Reference clock: Indicates whether the reference clock is launch or latch clock.

- Analysis type: Specifies constraints on Setup or Hold check.

- From: Indicates the start of the path; click "," to select one.

- Through: Indicates the pins or nets through the path; click "...." to select one.

- To: Indicates the end of the path; click ", to select one.

- Value: Specifies the number of multi-cycle periods, positive or negative integer; negative means advance, and positive means delay.

#### Note!

From, To and Through can be used individually or together with each other.

| 💸 Set Multicycle Path | ? ×                   |

|-----------------------|-----------------------|

| From:                 |                       |

| Through:              |                       |

| To:                   |                       |

| Analysis type         | Reference clock       |

| ● Setup ○ Hold        | ○ Start(launch clock) |

| Value:                |                       |

|                       | OK Cancel             |

2. Click "OK" to save the constraints.

# 4.7.4 Operating Conditions Constraints

The delay model used in timing constraints analysis can specify the speed level, model type and so on. Gowin Software uses Slow Model for Setup analysis and Fast Model for Hold analysis by default.

You can also customize the timing model. For example, in the case of hot and unstable power supply, the slow delay model can be specified. You can check the delay model in STA Tool Run Summary.

Select "Constraints > Set Operating Conditions", then "Set Operating Conditions" dialog box pops up, as shown in Figure 4-27.

- Grade: Commercial, industrial and automotive.

- Model: Slow and fast. Slow applies to high temperature and low voltage, and fast applies to low temperature and high voltage.

- Hold and Setup: Indicates hold time and setup time valid.

- Max function is the same as Setup, and Min function is the same as Hold.

- Max-Min is equivalent to selecting both Max and Min.

#### Figure 4-27 Create Operating Conditions Constraints

| W Set Opera | ting Conditions               |       |          | ?         | Х  |

|-------------|-------------------------------|-------|----------|-----------|----|

|             | ommercial () In<br>low () Fa: |       | tomotive |           |    |

| 🗌 Hold      | 🗌 Setup                       | 🗌 Max | 🔲 Min    | 🗌 Max-Min |    |

| Speed: 6 韋  |                               |       |          | OK Canc   | el |

#### Note!

- When the grade and speed set do not match the chip part number, the actual constraint shall prevail.

- If the grade and speed of the actual constraints do not support the current project, Gowin Software will report a warning message.

- The engineering sample (ES) uses the slowest speed to analyze the timing sequence by default, and you can set the speed of engineering sample as required.

# 4.7.5 Reports

### **Report Timing**

According to the set parameters, Gowin Software can provide reports with more details.

For example, Gowin Software reports 25 Setup analysis paths by default. When you need to view the analysis of 35 worst Setup paths, enter 35 in "Max Paths", as shown in Figure 4-29. The results can be found in the Setup and Hold reports.

The steps are as follows:

Select "Timing Constraints > Report Timing" and right-click to select "Create Report", as shown in Figure 4-28.

| I                        |               |            |          |      |         |    |   |

|--------------------------|---------------|------------|----------|------|---------|----|---|

| Timing Constraints       | Analysis type | From Clock | To Clock | From | Through | То |   |

| ✓ Clocks                 |               |            |          |      |         |    |   |

| Clock Latency            | Create R      |            |          |      |         |    |   |

| Clock Uncertainty        | Creaters      | lepon      |          |      |         |    |   |

| Clock Group              |               |            |          |      |         |    |   |

| I/O Delay                |               |            |          |      |         |    |   |

| ✓ Path                   |               |            |          |      |         |    |   |

| False Path               |               |            |          |      |         |    |   |

| Max/Min Delay            |               |            |          |      |         |    |   |

| Multicycle Path          |               |            |          |      |         |    |   |

| ✓ Report                 |               |            |          |      |         |    |   |

| Report Timing            |               |            |          |      |         |    |   |

| Report High Fanout Nets  |               |            |          |      |         |    |   |

| Report Route Congestion  |               |            |          |      |         |    |   |

| Report Min Pulse Width   |               |            |          |      |         |    |   |

| Report Max Frequency     |               |            |          |      |         |    |   |

| Report Exception         |               |            |          |      |         |    |   |

| Set Operating Conditions |               |            |          |      |         |    |   |

| ✓ Others                 |               |            |          |      |         |    |   |

| Create Derive Clocks     |               |            |          |      |         |    |   |

|                          |               |            |          |      |         |    |   |

|                          |               |            |          |      |         |    |   |

|                          |               |            |          |      |         |    |   |

|                          |               |            |          |      |         |    |   |

|                          | <             |            |          |      |         |    | > |

Figure 4-28 Create Report Timing

- 2. Select "Create Report" and Figure 4-29 pops up.

- Path: Specifies the max. paths, the max. common paths, the max./min. logic level, positive integers

- Clocks: Specifies the associated clock of a path. From/To Clock indicates the transmitted clock and sample clock respectively; click

" " on the right to select one.

- Objects: Specifies the start and end objects of the analysis; click

" " on the right to select one.

- Analysis Type: Specifies Setup, Hold, Recovery and Removal.

- Module Instance: Specifies the instance name; click " " on the right to select one.

| 🐳 Report Timing                        |        |                  |           | ?   | ×   |

|----------------------------------------|--------|------------------|-----------|-----|-----|

| Clocks<br>From clock: ▼<br>To clock: ▼ |        |                  |           |     | ~   |

| Objects From: Through: To:             |        |                  |           |     |     |

| Analysis Type<br>Setup                 | ⊖ Hold | O Recovery       | 🔿 Removal |     |     |

| Path                                   |        | _                |           |     |     |

| Max Paths:                             |        | Min Logic Level: |           |     |     |

| Max Common Paths:                      |        | Max Logic Level: |           |     |     |

| Module Instance:                       |        |                  |           |     |     |

|                                        |        | I                | OK        | Can | cel |

**Figure 4-29 Report Timing Dialog Box**

## 3. Click "OK" to save.

#### **Report High Fanout Nets**

It reports the number of fans for Net, 10 of the largest by default.

If you need to view the net between 5 and 7, you can specify Min Fanout as 5 and Max Fanout as 7. The results can be viewed in High Fanout Nets Report.

The steps are as follows:

- 1. Select "Timing Constraints > Report High Fanout Nets".

- 2. Right-click to select "Create Report", and Create Report dialog box pops up, as shown in Figure 4-30.

| Timing Constraints       | Max Net Number | Max Fanout Number | Min Fanout Number | Report Clock Net | Report Set/Reset Net |

|--------------------------|----------------|-------------------|-------------------|------------------|----------------------|

| ✓ Clocks                 |                |                   |                   |                  |                      |

| Clock Latency            |                |                   |                   |                  |                      |

| Clock Uncertainty        | C 1 D          |                   |                   |                  |                      |

| Clock Group              | Create Re      | port              |                   |                  |                      |

| I/O Delay                |                |                   |                   |                  |                      |

| ✓ Path                   |                |                   |                   |                  |                      |

| False Path               |                |                   |                   |                  |                      |

| Max/Min Delay            |                |                   |                   |                  |                      |

| Multicycle Path          |                |                   |                   |                  |                      |

| ✓ Report                 |                |                   |                   |                  |                      |

| Report Timing            |                |                   |                   |                  |                      |

| Report High Fanout Nets  |                |                   |                   |                  |                      |

| Report Route Congestion  |                |                   |                   |                  |                      |

| Report Min Pulse Width   |                |                   |                   |                  |                      |

| Report Max Frequency     |                |                   |                   |                  |                      |

| Report Exception         |                |                   |                   |                  |                      |

| Set Operating Conditions |                |                   |                   |                  |                      |

| ✓ Others                 |                |                   |                   |                  |                      |

| Create Derive Clocks     |                |                   |                   |                  |                      |