# GW2AN-18X & 9X 器件 编程配置手册

UG702-1.1.2, 2023-04-13

版权所有 © 2023 广东高云半导体科技股份有限公司

**GOWIN高云**、Gowin、晨熙、高云均为广东高云半导体科技股份有限公司注册商标，本手册中提到的其他任何商标，其所有权利属其拥有者所有。未经本公司书面许可，任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部，并不得以任何形式传播。

## 免责声明

本文档并未授予任何知识产权的许可，并未以明示或暗示，或以禁止发言或其它方式授予任何知识产权许可。除高云半导体在其产品的销售条款和条件中声明的责任之外，高云半导体概不承担任何法律或非法律责任。高云半导体对高云半导体产品的销售和 / 或使用不作任何明示或暗示的担保，包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等，均不作担保。高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任，高云半导体保留修改文档中任何内容的权利，恕不另行通知。高云半导体不承诺对这些文档进行适时的更新。

## 版本信息

| 日期         | 版本    | 说明                                                                                                                                                                                |

|------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2021/09/10 | 1.0   | 初始版本。                                                                                                                                                                             |

| 2022/03/04 | 1.0.1 | 更新配置管脚的默认状态。                                                                                                                                                                      |

| 2022/07/28 | 1.0.2 | 增加 I <sup>2</sup> C 配置模式的说明。                                                                                                                                                      |

| 2022/09/06 | 1.1   | <ul style="list-style-type: none"><li>● 更新 5.8 I<sup>2</sup>C 配置模式。</li><li>● 增加 6.5 背景烧录 (Background Programming)。</li></ul>                                                     |

| 2022/12/08 | 1.1.1 | <ul style="list-style-type: none"><li>● 更新 CLKHOLD_N 管脚的说明。</li><li>● 新增图 5-35 CPU 配置模式时序图。</li><li>● 新增表 5-14 CPU 配置模式时序参数。</li></ul>                                            |

| 2023/04/13 | 1.1.2 | <ul style="list-style-type: none"><li>● 更新图 5-34 CPU 模式配置流程示意图。</li><li>● 更新图 5-35 CPU 配置模式时序图。</li><li>● 更新表 5-14 CPU 配置模式时序参数。</li><li>● 新增使用 QSSPI 模式编程 Flash 的相关描述。</li></ul> |

# 目录

|                                     |           |

|-------------------------------------|-----------|

| 目录 .....                            | i         |

| 图目录 .....                           |           |

| 表目录 .....                           |           |

| <b>1 关于本手册 .....</b>                | <b>1</b>  |

| 1.1 手册内容 .....                      | 1         |

| 1.2 相关文档 .....                      | 1         |

| 1.3 术语、缩略语 .....                    | 2         |

| 1.4 技术支持与反馈 .....                   | 3         |

| <b>2 名词解释 .....</b>                 | <b>4</b>  |

| <b>3 配置模式 .....</b>                 | <b>6</b>  |

| <b>4 配置管脚介绍 .....</b>               | <b>8</b>  |

| 4.1 配置管脚列表及复用选项 .....               | 8         |

| 4.1.1 配置管脚列表 .....                  | 8         |

| 4.1.2 配置管脚复用 .....                  | 9         |

| 4.2 配置管脚功能及应用 .....                 | 11        |

| <b>5 配置模式介绍 .....</b>               | <b>14</b> |

| 5.1 配置须知 .....                      | 14        |

| 5.2 AUTO BOOT 配置 .....              | 17        |

| 5.3 JTAG 配置 .....                   | 18        |

| 5.3.1 JTAG 配置模式管脚 .....             | 18        |

| 5.3.2 JTAG 配置模式连接示意图 .....          | 19        |

| 5.3.3 JTAG 配置模式时序图 .....            | 20        |

| 5.3.4 JTAG 相关配置流程 .....             | 20        |

| 5.4 SSPI 配置模式 .....                 | 37        |

| 5.4.1 SSPI 配置模式管脚 .....             | 37        |

| 5.4.2 SSPI 配置模式时序图 .....            | 39        |

| 5.4.3 SSPI 配置指令 .....               | 40        |

| 5.4.4 SSPI Configure SRAM 流程图 ..... | 43        |

| 5.4.5 SSPI 配置模式连接示意图 .....          | 44        |

---

|                                         |           |

|-----------------------------------------|-----------|

| 5.4.6 SSPI 模式下的多 FPGA 连线示意图 .....       | 45        |

| 5.5 QSSPI 配置模式 .....                    | 46        |

| 5.6 CPU 配置模式.....                       | 51        |

| 5.6.1 配置时序 .....                        | 52        |

| 5.7 SERIAL 配置模式 .....                   | 53        |

| 5.8 I <sup>2</sup> C 配置模式 .....         | 55        |

| 5.8.1 配置指令 .....                        | 57        |

| 5.8.2 I <sup>2</sup> C 配置 SRAM 流程 ..... | 59        |

| 5.8.3 I <sup>2</sup> C 配置 Flash 流程..... | 59        |

| <b>6 比特流文件配置.....</b>                   | <b>63</b> |

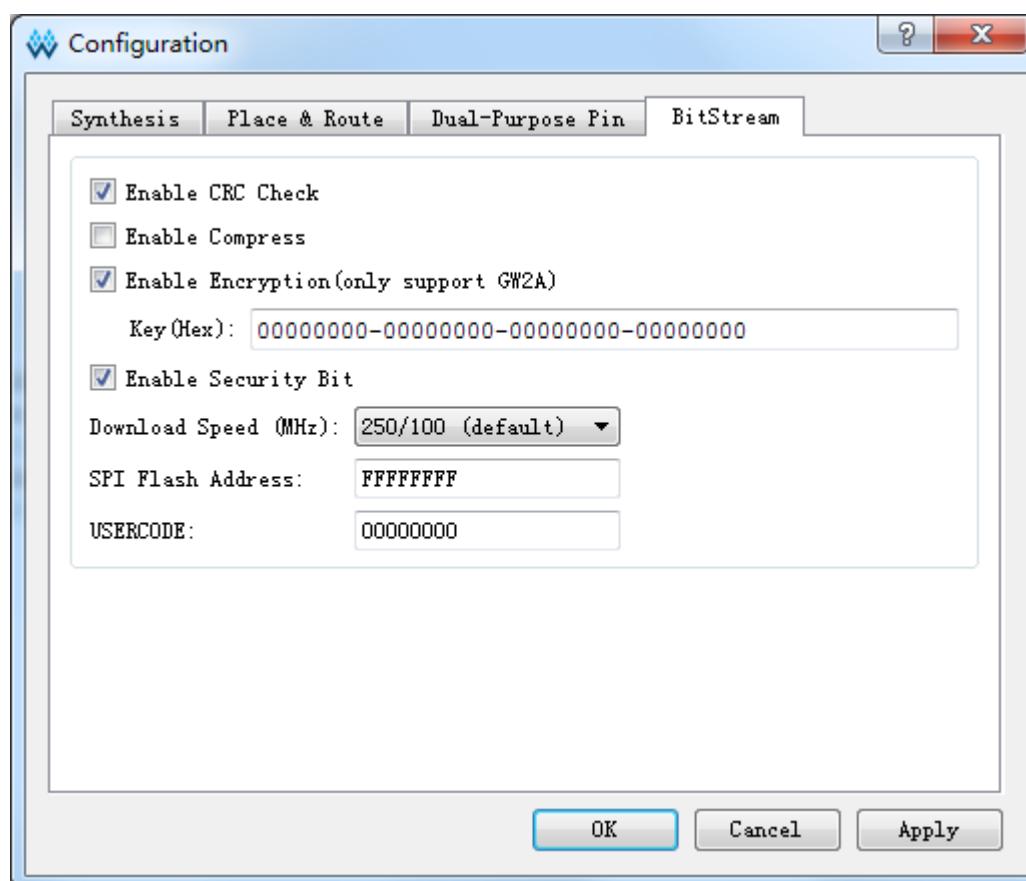

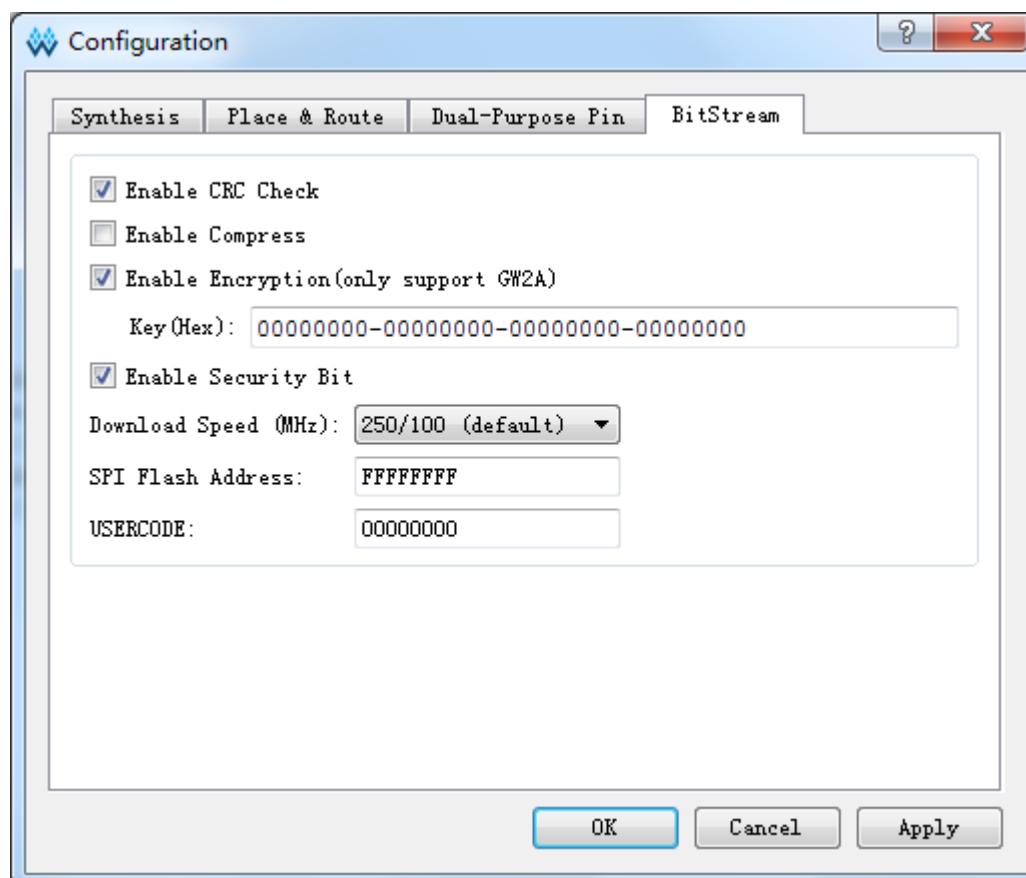

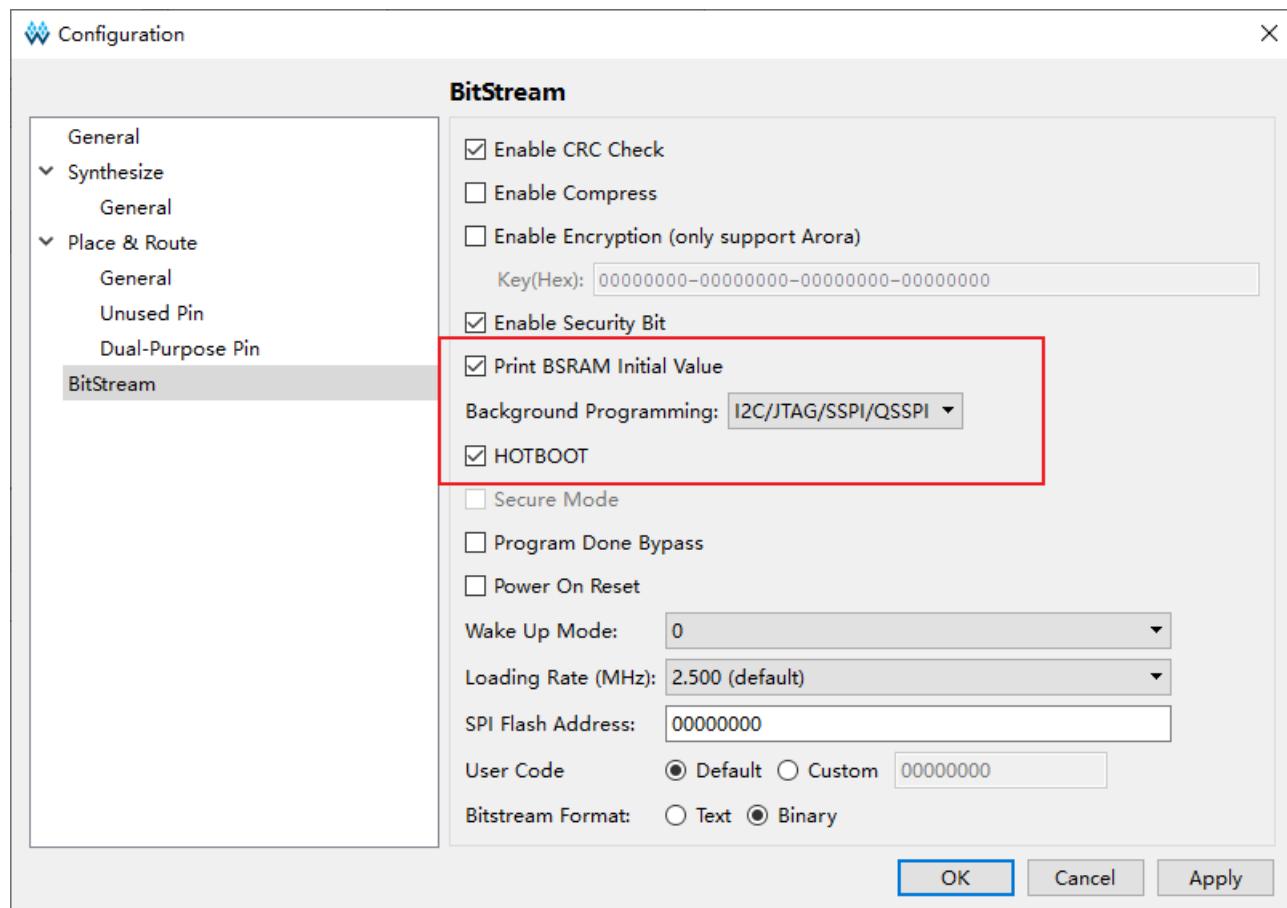

| 6.1 配置选项设置 .....                        | 63        |

| 6.2 配置数据加密 .....                        | 64        |

| 6.2.1 定义.....                           | 64        |

| 6.2.2 输入加密密钥 .....                      | 65        |

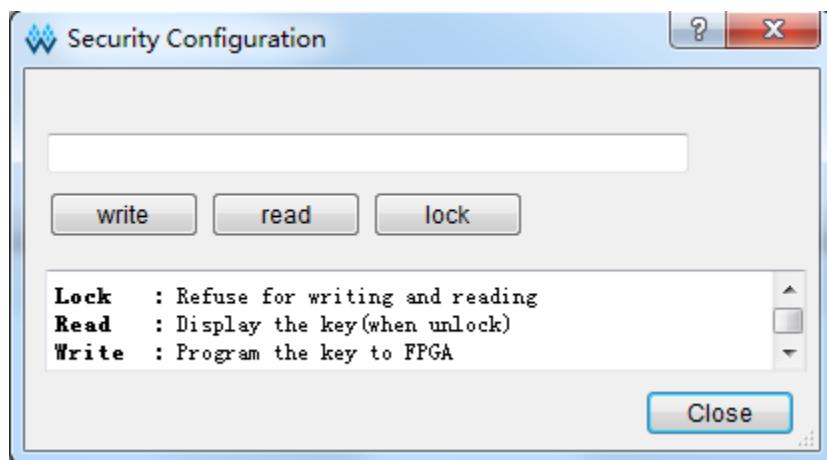

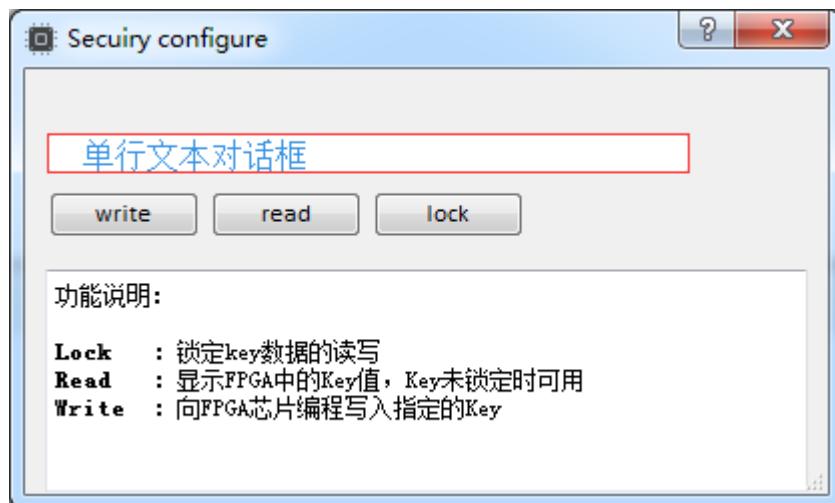

| 6.2.3 输入解密密钥 .....                      | 65        |

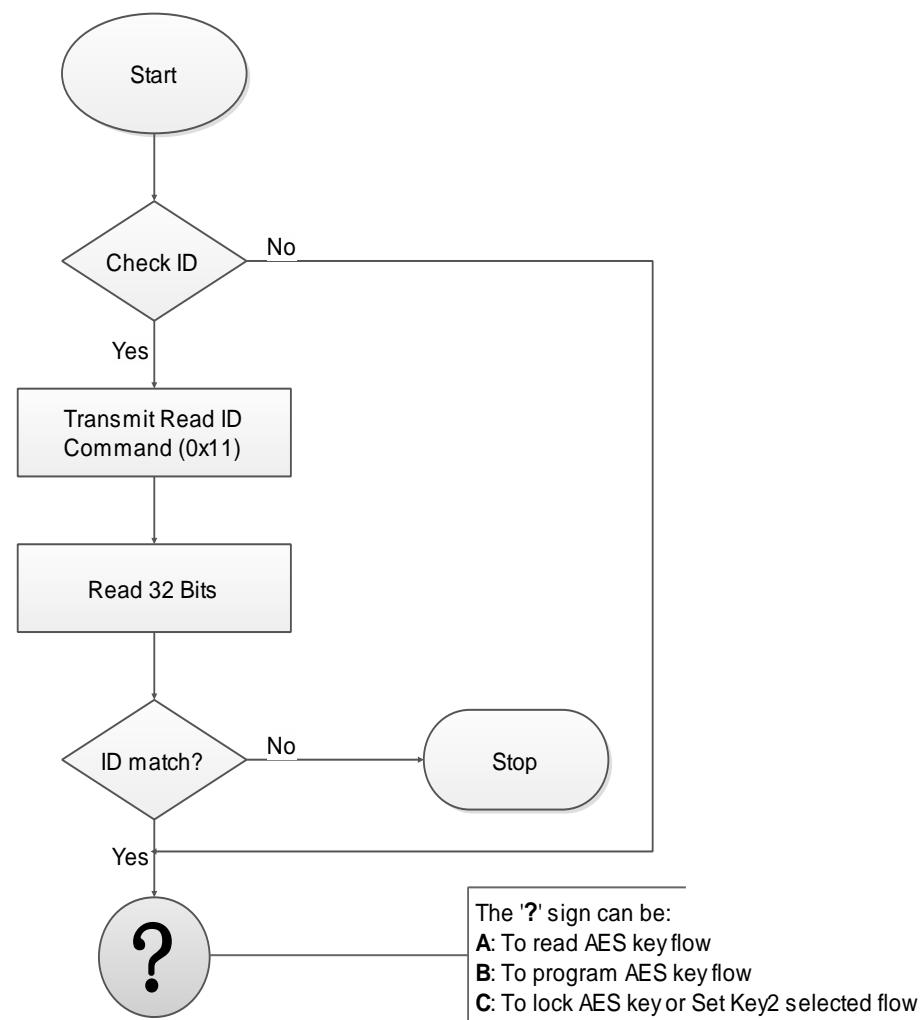

| 6.2.4 AES 密钥编程操作 .....                  | 66        |

| 6.2.5 AES 密钥编程流程 .....                  | 68        |

| 6.3 配置文件大小 .....                        | 71        |

| 6.4 配置文件加载时长.....                       | 73        |

| 6.5 背景烧录（Background Programming） .....  | 74        |

| <b>7 安全性考虑.....</b>                     | <b>75</b> |

| <b>8 边界扫描操作 .....</b>                   | <b>77</b> |

# 图目录

|                                                   |    |

|---------------------------------------------------|----|

| 图 4-1 配置管脚复用设置.....                               | 11 |

| 图 5-1 固定管脚推荐接法.....                               | 16 |

| 图 5-2 重新上电时序图 .....                               | 16 |

| 图 5-3 触发时序图 .....                                 | 17 |

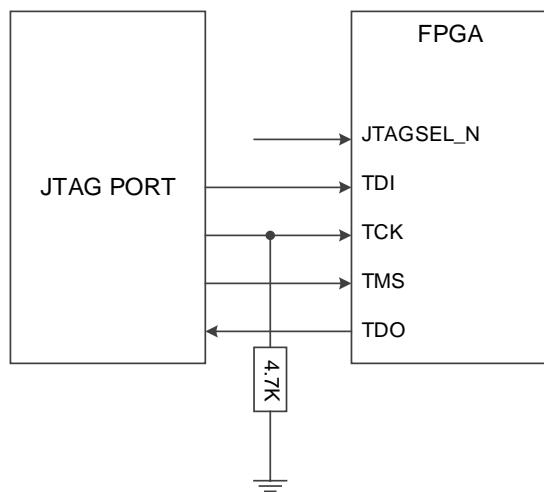

| 图 5-4 JTAG 配置模式连接示意图 .....                        | 19 |

| 图 5-5 JTAG 菊花链配置模式连接示意图 .....                     | 19 |

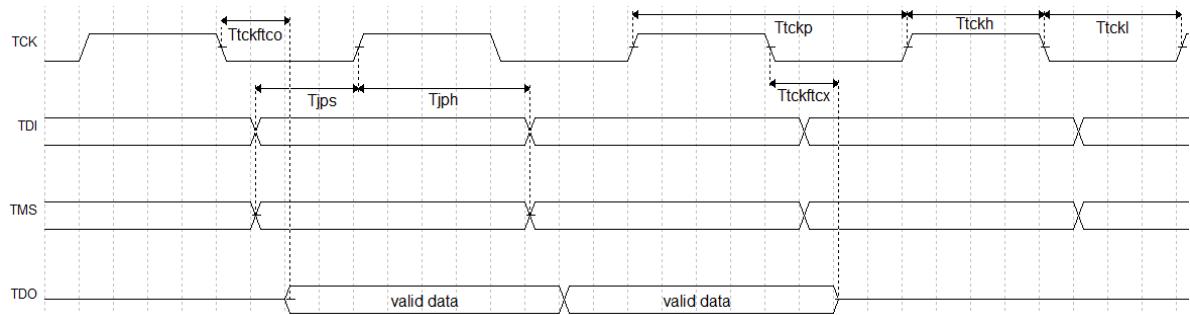

| 图 5-6 JTAG 配置模式时序图 .....                          | 20 |

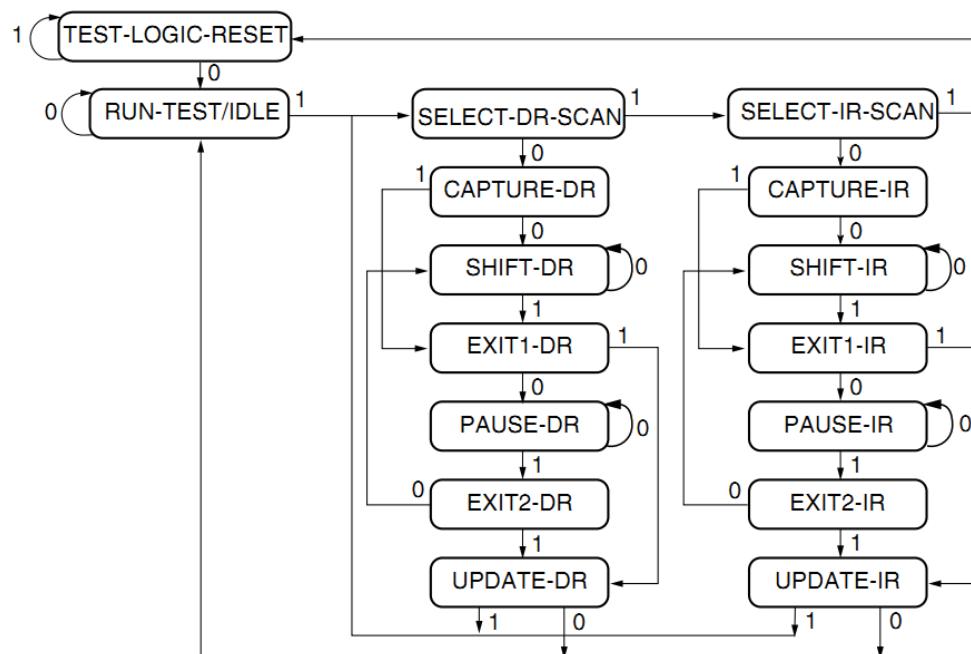

| 图 5-7 TAP 状态机.....                                | 21 |

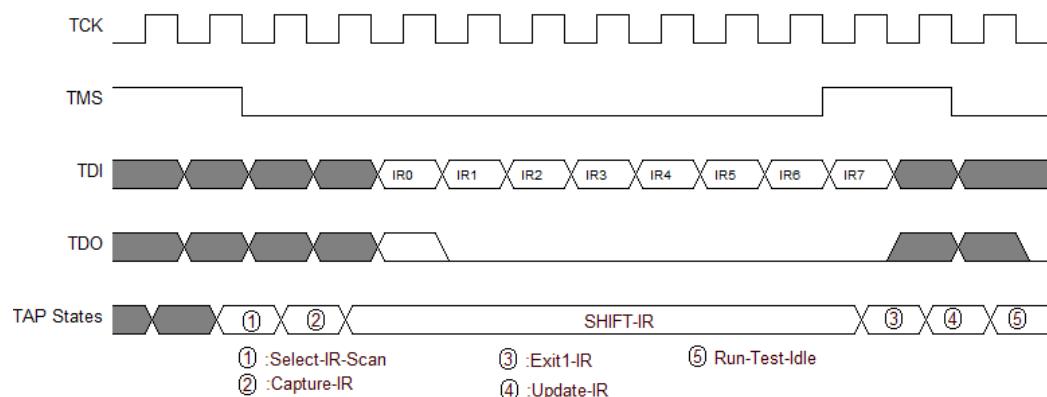

| 图 5-8 指令寄存器访问时序 .....                             | 22 |

| 图 5-9 数据寄存器访问时序 .....                             | 22 |

| 图 5-10 读取 ID Code 状态机流程图 .....                    | 24 |

| 图 5-11 读取 ID Code 指令-0x11 访问时序 .....              | 24 |

| 图 5-12 读取 ID Code(0x0000581B)数据寄存器访问时序.....       | 24 |

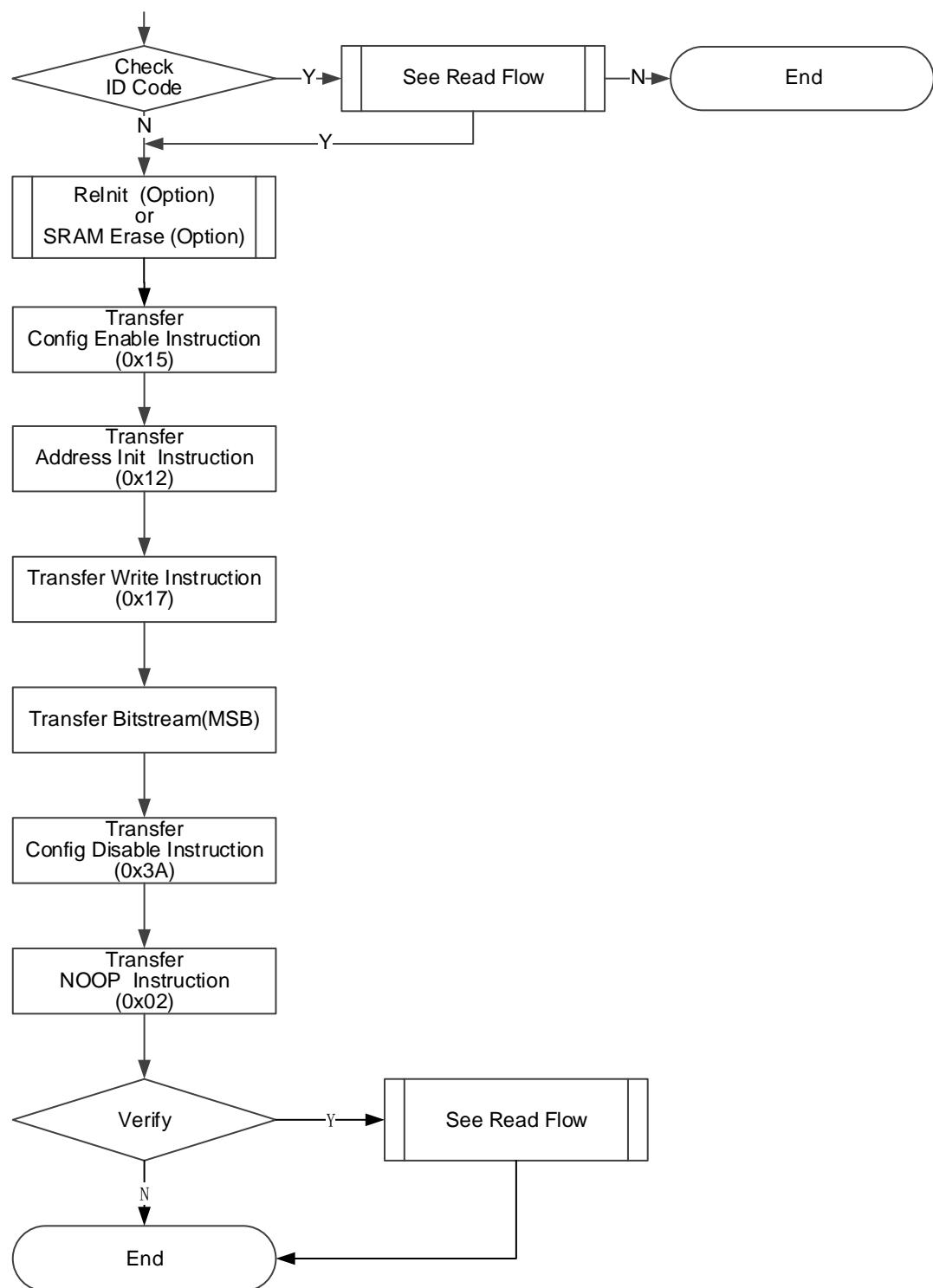

| 图 5-13 配置 SRAM 流程.....                            | 26 |

| 图 5-14 读取 SRAM 的流程 .....                          | 28 |

| 图 5-15 采用 Boundary Scan 模式编程 SPI Flash 流程示意图..... | 35 |

| 图 5-16 菊花链连接示意图.....                              | 37 |

| 图 5-17 SSPI 配置模式时序图 .....                         | 39 |

| 图 5-18 读取 ID Code 时序示意图 .....                     | 40 |

| 图 5-19 Write Enable (0x15) 时序示意图.....             | 41 |

| 图 5-20 Write Disable (0x3A00) 时序示意图 .....         | 41 |

| 图 5-21 Write Data (0x3B) 时序示意图.....               | 42 |

| 图 5-22 SSPI 配置模式连接示意图.....                        | 44 |

| 图 5-23 SSPI 编程外部 Flash 连接示意图 .....                | 44 |

| 图 5-24 SSPI 配置 Flash 流程图.....                     | 45 |

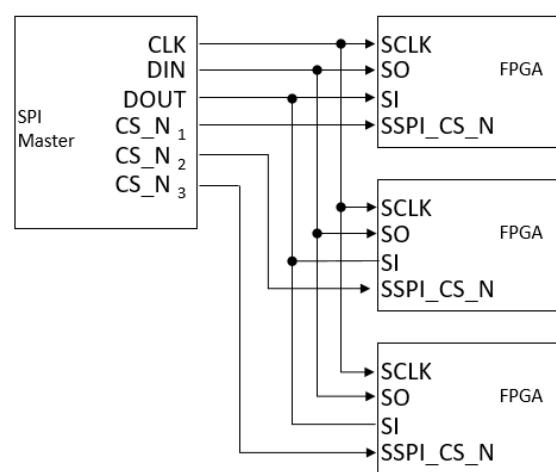

| 图 5-25 多 FPGA 连线示意图 1 .....                       | 45 |

| 图 5-26 多 FPGA 连线示意图 2 .....                       | 46 |

| 图 5-27 QSSPI Write Data (0x6B) 时序图 .....          | 47 |

| 图 5-28 QSSPI 配置 SRAM 流程图 .....                    | 48 |

---

|                                              |    |

|----------------------------------------------|----|

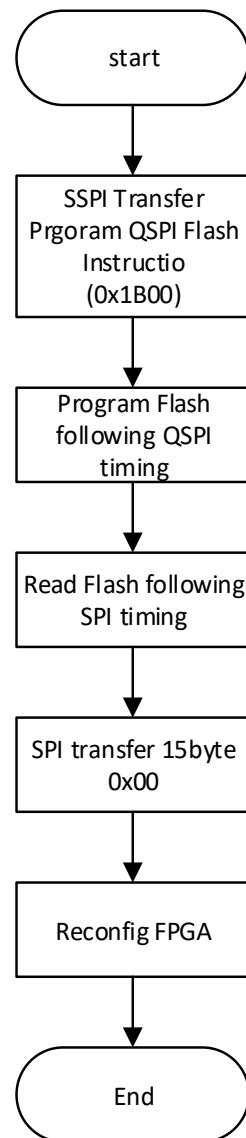

| 图 5-29 QSSPI 编程 Flash 流程图 .....              | 49 |

| 图 5-30 QSSPI write instruction 时序图 .....     | 50 |

| 图 5-31 QSSPI write data 时序图 .....            | 50 |

| 图 5-32 QSSPI page program 时序图 .....          | 50 |

| 图 5-33 CPU 配置模式连接示意图 .....                   | 51 |

| 图 5-34 CPU 模式配置流程示意图 .....                   | 52 |

| 图 5-35 CPU 配置模式时序图 .....                     | 52 |

| 图 5-36 SERIAL 配置模式连接示意图 .....                | 54 |

| 图 5-37 SERIAL 配置模式时序图 .....                  | 54 |

| 图 5-38 I <sup>2</sup> C 配置模式连接示意图 .....      | 55 |

| 图 5-39 I <sup>2</sup> C 配置模式时序图 .....        | 56 |

| 图 5-40 Reinit 时序图 .....                      | 58 |

| 图 5-41 配置 SRAM 时序图 .....                     | 58 |

| 图 5-42 配置 Flash 时序图 .....                    | 58 |

| 图 5-43 Reboot 时序图 .....                      | 58 |

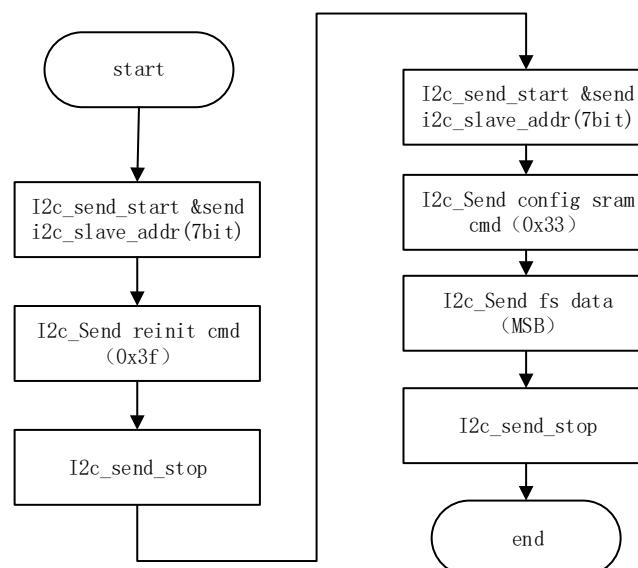

| 图 5-44 I <sup>2</sup> C 配置 SRAM 的流程图 .....   | 59 |

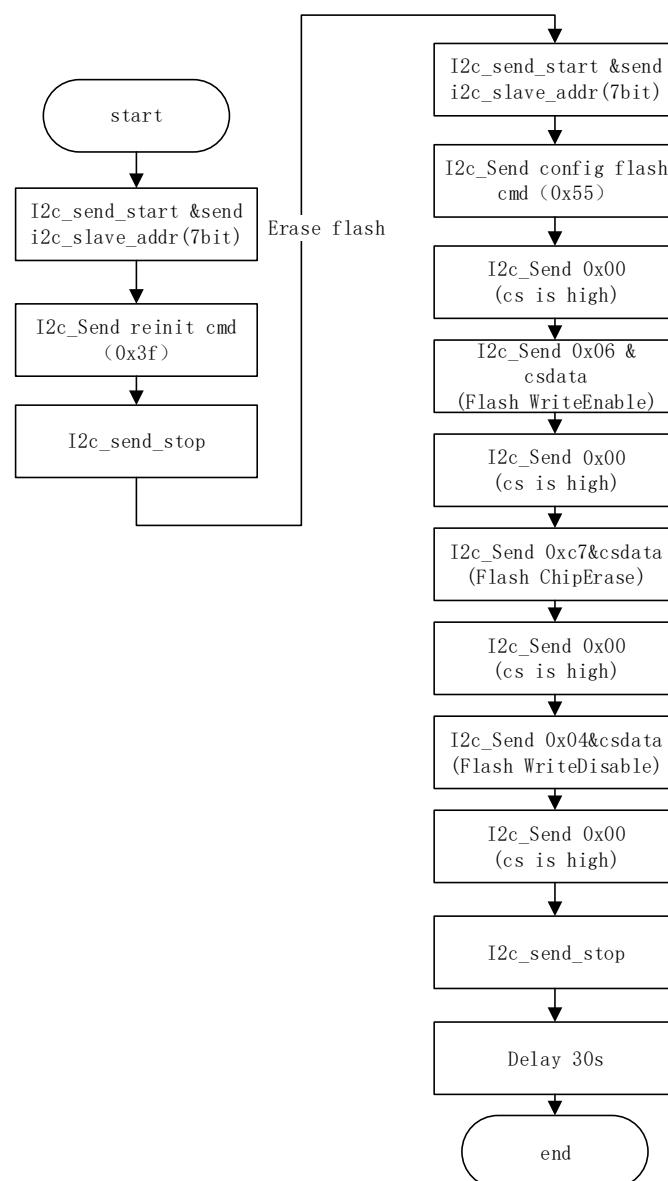

| 图 5-45 I <sup>2</sup> C 擦除 Flash 的流程图 .....  | 60 |

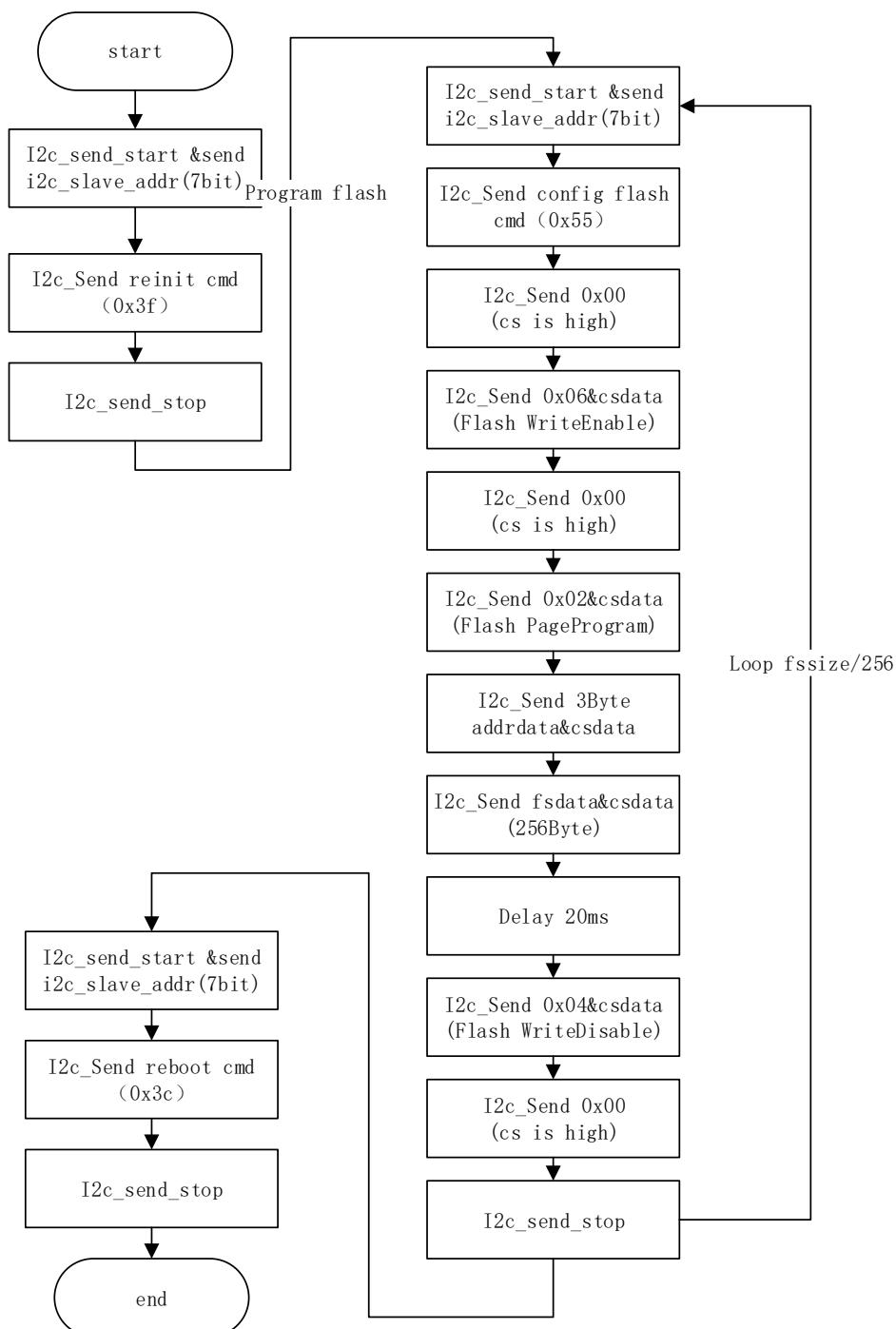

| 图 5-46 I <sup>2</sup> C 配置 Flash 的流程图： ..... | 62 |

| 图 6-1 配置选项 .....                             | 64 |

| 图 6-2 加密密钥设置方法 .....                         | 65 |

| 图 6-3 解密密钥设置方法 .....                         | 66 |

| 图 6-4 AES 编程对话框 .....                        | 66 |

| 图 6-5 Prepare .....                          | 68 |

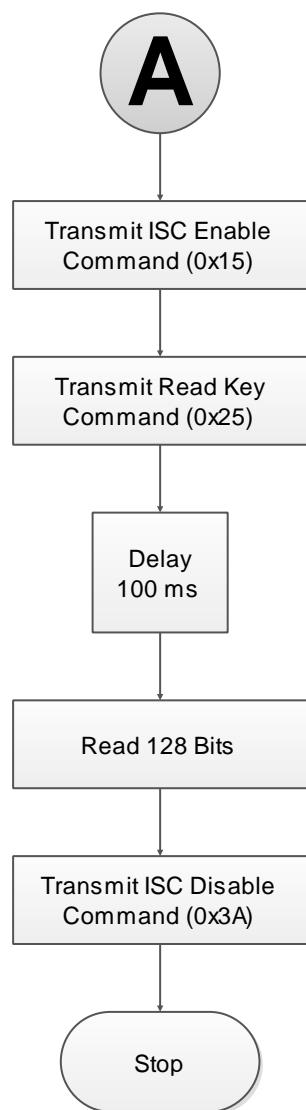

| 图 6-6 Read AES Key Flow .....                | 69 |

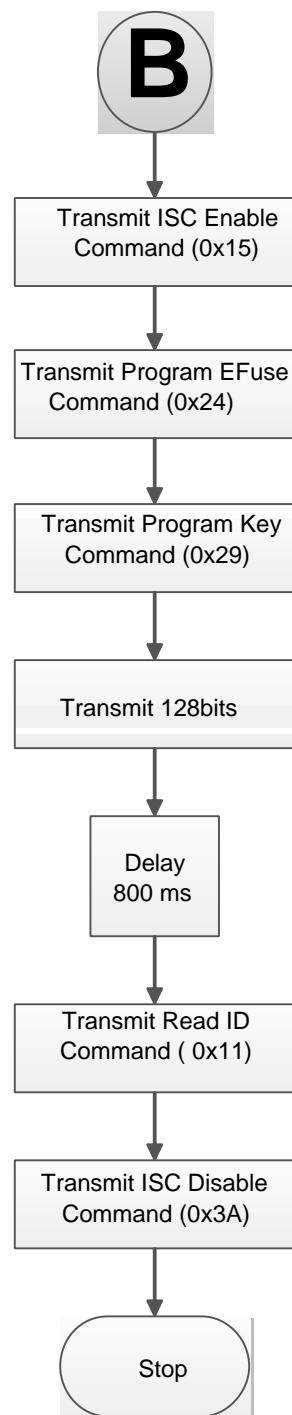

| 图 6-7 Program AES Key Flow .....             | 70 |

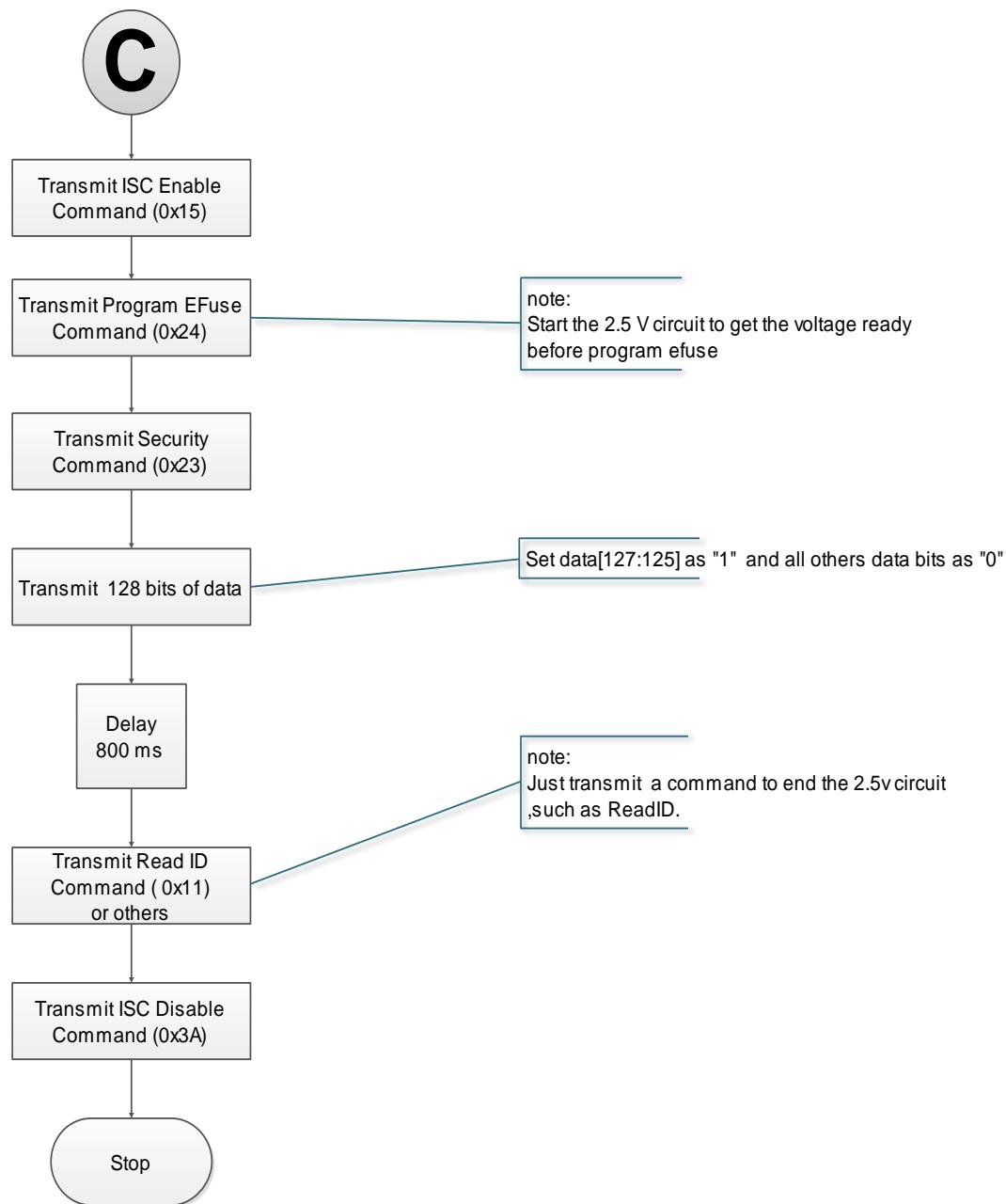

| 图 6-8 Lock AES Key Flow .....                | 71 |

| 图 6-9 比特流格式生成 .....                          | 72 |

| 图 6-10 Background Programming 选项 .....       | 74 |

| 图 8-1 边界扫描操作示意图 .....                        | 78 |

# 表目录

|                                                               |    |

|---------------------------------------------------------------|----|

| 表 1-1 术语、缩略语 .....                                            | 2  |

| 表 2-1 名词解释 .....                                              | 4  |

| 表 3-1 配置模式 .....                                              | 6  |

| 表 4-1 配置管脚列表 .....                                            | 8  |

| 表 4-2 配置管脚复用选项 .....                                          | 9  |

| 表 4-3 管脚功能 .....                                              | 11 |

| 表 5-1 高云半导体 FPGA GW2AN-18X/9X 产品重新上电和 RECONFIG_N 触发时序参数 ..... | 17 |

| 表 5-2 JTAG 配置模式管脚定义 .....                                     | 18 |

| 表 5-3 JTAG 配置模式时序参数 .....                                     | 20 |

| 表 5-4 Gowin 部分 FPGA 产品 ID CODE .....                          | 23 |

| 表 5-5 发送指令过程中 TDI 和 TMS 的值变化 .....                            | 23 |

| 表 5-6 器件 SRAM 地址数量和地址长度 .....                                 | 27 |

| 表 5-7 管脚状态 .....                                              | 35 |

| 表 5-8 Status Register 与配置加载相关的条目 .....                        | 36 |

| 表 5-9 SSPI 配置模式管脚 .....                                       | 37 |

| 表 5-10 SSPI 配置模式时序参数 .....                                    | 39 |

| 表 5-11 配置指令 .....                                             | 40 |

| 表 5-12 QSSPI 配置模式管脚 .....                                     | 46 |

| 表 5-13 CPU 配置模式管脚 .....                                       | 51 |

| 表 5-14 CPU 配置模式时序参数 .....                                     | 53 |

| 表 5-15 SERIAL 配置模式管脚定义 .....                                  | 53 |

| 表 5-16 SERIAL 配置模式时序参数 .....                                  | 54 |

| 表 5-17 I <sup>2</sup> C 配置模式管脚定义 .....                        | 55 |

| 表 5-18 I <sup>2</sup> C 配置模式时序参数 .....                        | 56 |

| 表 5-19 I <sup>2</sup> C 配置模式频率及地址 .....                       | 57 |

| 表 5-20 I <sup>2</sup> C 配置指令 .....                            | 57 |

| 表 6-1 高云半导体 FPGA GW2AN-18X/9X 产品配置文件大小（最大情况） .....            | 72 |

| 表 6-2 Autoboot 模式数据流文件加载时长 .....                              | 73 |

# 1 关于本手册

## 1.1 手册内容

本手册主要介绍高云半导体晨熙<sup>®</sup>(Arora)家族 FPGA 产品中的 GW2AN-18X/9X 系列在编程配置方面的通用特性及功能，旨在帮助用户更好地使用 Gowin FPGA 产品。

## 1.2 相关文档

通过登录高云半导体网站 [www.gowinsemi.com.cn](http://www.gowinsemi.com.cn) 可以下载、查看以下相关文档：

- [DS971, GW2AN-18X & 9X 器件数据手册](#)

- [UG973, GW2AN-18X & 9X 器件封装与管脚手册](#)

- [UG972, GW2AN-18X 器件 Pinout 手册](#)

- [UG978, GW2AN-9X 器件 Pinout 手册](#)

## 1.3 术语、缩略语

表 1-1 中列出了本手册中出现的相关术语、缩略语及相关释义。

**表 1-1 术语、缩略语**

| 术语、缩略语                     | 全称                                                | 描述                                                              |

|----------------------------|---------------------------------------------------|-----------------------------------------------------------------|

| Background Programming     | Embedded Flash Background Programming             | 是指在不影响FPGA当前运行的功能和I/O状态下，对内置Flash的数据流文件进行更新。                    |

| Bitstream                  | Bitstream Data                                    | 配置FPGA SRAM的数据                                                  |

| Bscan                      | Boundary Scan                                     | 边界扫描测试技术                                                        |

| Configuration              | Configuration                                     | 配置FPGA SRAM区域的过程                                                |

| Configuration Data         | Configuration Data                                | 配置FPGA SRAM的数据                                                  |

| Configuration Mode         | Configuration Mode                                | 配置模式，决定 Configuration Data 源                                    |

| CPU                        | Central Processing Unit                           | 中央处理器                                                           |

| CRC                        | Cyclic Redundancy Check                           | 循环冗余校验                                                          |

| Edit Mode                  | Edit Mode                                         | FPGA 处于 Configuration 或 Programming 所在模式                        |

| EFlash/EmbFlash            | Embedded Flash                                    | FPGA 内置 Flash 存储器                                               |

| FPGA                       | Field Programmable Gate Array                     | 现场可编程门阵列                                                        |

| FS file                    | Fuses file                                        | 包含配置数据的 ASCII 文件                                                |

| GPIO                       | Gowin Programmable I/O                            | Gowin 可编程通用管脚                                                   |

| I2C (I <sup>2</sup> C、IIC) | Inter-Integrated Circuits                         | 集成电路总线                                                          |

| ID                         | Identification                                    | 身份标识号                                                           |

| IEEE                       | Institute of Electrical and Electronics Engineers | 电气和电子工程师协会                                                      |

| Internal Flash             | Internal Flash                                    | 同 Embedded Flash                                                |

| JTAG                       | Joint Test Action Group                           | 联合测试行动组                                                         |

| LSB                        | Least Significant Bit                             | 最低有效位（优先）                                                       |

| LUT                        | Look-up Table                                     | 查找表                                                             |

| MSB                        | Most Significant Bit                              | 最高有效位（优先）                                                       |

| MSPI                       | Master Serial Peripheral Interface                | 主串行外设接口                                                         |

| Programming                | Programming                                       | 将 Configuration Data 烧录到 Embedded Flash 或 External Flash 存储器的过程 |

| SCL                        | Serial Clock                                      | I2C 上的时钟线                                                       |

| SDA                        | Serial Data                                       | I2C 上的数据线                                                       |

| Security Bit               | Security Bit                                      | 安全位（使 SRAM 回读永为高电平）                                             |

| SPI                        | Serial Peripheral Interface                       | 串行外设接口                                                          |

| SRAM                       | Static Random Access Memory                       | 静态随机存储器                                                         |

| 术语、缩略语    | 全称                                | 描述                                                 |

|-----------|-----------------------------------|----------------------------------------------------|

| SSPI      | Slave Serial Peripheral Interface | 从串行外设接口                                            |

| TAP       | Test Access Port                  | 测试访问口                                              |

| User Mode | User Mode                         | FPGA 在 Configuration 或 Programming 完成后，并且逻辑功能执行的模式 |

## 1.4 技术支持与反馈

高云半导体提供全方位技术支持，在使用过程中如有任何疑问或建议，可直接与公司联系：

网址: [www.gowinsemi.com.cn](http://www.gowinsemi.com.cn)

E-mail: [support@gowinsemi.com](mailto:support@gowinsemi.com)

Tel: +86 755 8262 0391

# 2 名词解释

本章主要介绍高云半导体 **FPGA** 产品编程配置过程中常用的一些名词及含义，帮助用户熟悉高云半导体 **FPGA** 产品编程配置相关的概念。

**表 2-1 名词解释**

| 名词                       | 释义                                                                                                                                                                                 |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 编程（Program）              | 将 <b>Gowin</b> 云源软件生成的比特流数据写入到 <b>FPGA</b> 内置 <b>Flash</b> 或者与 <b>FPGA</b> 相连的外部 <b>SPI Flash</b> 的过程。                                                                             |

| 配置（Configure）            | 将 <b>Gowin</b> 云源软件生成的比特流数据通过外部接口或内置 <b>Flash</b> 加载到 <b>FPGA</b> 的 <b>SRAM</b> 存储区的过程。                                                                                            |

| <b>GowinCONFIG</b>       | 除通用的 <b>JTAG</b> 配置模式外，高云半导体 <b>FPGA</b> 产品支持的其他配置方式，包括自启动配置，双启动配置， <b>MSPI</b> 配置， <b>SSPI</b> 配置， <b>SERIAL</b> 配置， <b>CPU</b> 配置。每款器件支持的 <b>GowinCONFIG</b> 配置模式多少取决于器件型号和封装类型。 |

| <b>MODE[1:0]</b>         | 与 <b>GowinCONFIG</b> 相关的 2 个 <b>MODE</b> 管脚的值的表示方法。                                                                                                                                |

| 自启动配置（AUTO BOOT）         | <b>FPGA</b> 从内置 <b>Flash</b> 读取比特流数据进行配置的过程。只有非易失器件支持此模式。                                                                                                                          |

| <b>MSPI</b> 配置           | <b>FPGA</b> 作为主器件（ <b>master</b> ），通过 <b>SPI</b> 接口主动从外部 <b>Flash</b> 读取比特流数据进行配置的过程。                                                                                              |

| <b>SSPI</b> 配置           | <b>FPGA</b> 作为从器件（ <b>slave</b> ），外部主机（ <b>master</b> ）通过 <b>SPI</b> 接口写入比特流数据进行配置的过程。                                                                                             |

| <b>QSSPI</b> 配置          | <b>FPGA</b> 作为从器件（ <b>slave</b> ），外部主机（ <b>master</b> ）通过 <b>QSPI</b> 接口写入比特流数据进行配置的过程。                                                                                            |

| <b>SERIAL</b> 配置         | <b>FPGA</b> 作为从器件（ <b>slave</b> ），外部主机（ <b>master</b> ）通过串行接口写入比特流数据进行配置的过程。                                                                                                       |

| <b>CPU</b> 配置            | <b>FPGA</b> 作为从器件（ <b>slave</b> ），外部主机（ <b>master</b> ）通过并行接口（数据位宽 8-bit）写入比特流数据进行配置的过程。                                                                                           |

| <b>I<sup>2</sup>C</b> 配置 | <b>FPGA</b> 作为从器件（ <b>slave</b> ），外部主机（ <b>master</b> ）通过 <b>I<sup>2</sup>C</b> 接口写入比特流数据进行配置的过程。                                                                                  |

| 多重配置（MULTI BOOT）         | <b>MSPI</b> 配置模式的衍生概念，是指 <b>FPGA</b> 从外部 <b>Flash</b> 的不同地址读取比特流数据进行配置的过程。用户在前一个比特流数                                                                                               |

| 名词                | 释义                                                                                                                                           |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|                   | 据中写入后一次配置的比特流数据的加载地址，在器件不掉电的情况下通过触发 <b>RECONFIG_N</b> 切换数据流文件完成配置。支持 <b>MSPI</b> 配置模式的 <b>FPGA</b> 产品均支持此模式。                                 |

| 远程升级              | 用户的一种应用场景，即在 <b>FPGA</b> 启动工作后，若有升级需求，先通过远程操作将比特流数据写入到外部 <b>Flash</b> 中，通过触发 <b>RECONFIG_N</b> 或重新上电使 <b>FPGA</b> 读取外部 <b>Flash</b> 完成配置的过程。 |

| 菊花链               | <b>FPGA</b> 器件以串行的方式依次连接起来的一种方式，可以从链首按照连接顺序依次对器件进行配置，只有相邻的器件之间才能传输数据。                                                                        |

| 用户模式（User Mode）   | <b>FPGA</b> 完成一次配置操作后，将控制权移交给用户的行为。配置管脚复用为普通 I/O 的设置仅在用户模式下生效。                                                                               |

| 编辑模式（Edit Mode）   | 可以对 <b>FPGA</b> 进行编程或配置操作的模式。<br>编辑模式下所有的配置管脚无法作为普通 I/O 使用，所有的普通管脚输出为高阻态（透明传输除外）。                                                            |

| ID CODE           | 高云半导体 <b>FPGA</b> 器件的身份标识，每一个系列的器件具有独立的编号。                                                                                                   |

| USER CODE         | 用户为自己所使用的 <b>FPGA</b> 器件进行的身份标识，可以通过 <b>Gowin</b> 编程软件写入到器件中，最高可支持 32-bit。                                                                   |

| 安全位（Security Bit） | 高云半导体为保护 <b>FPGA</b> 产品配置数据运行时的安全性所做的特殊设计。用户将设置了安全位的比特流数据写入器件 <b>SRAM</b> 后，任何人都将无法进行数据回读操作。云源软件默认为所有 <b>FPGA</b> 产品的比特流数据设置了安全位。            |

| 加密（Encryption）    | 晨熙®( <b>Arora</b> )家族 <b>FPGA</b> 产品支持的特性，加密的比特流数据写入 <b>FPGA</b> 后，器件自行与事先存储的密钥匹配，匹配成功后进行解密并唤醒器件；匹配失败后器件无法工作。                                |

# 3 配置模式

晨熙<sup>®</sup>(Arora)家族 FPGA 产品除了支持业界通用的 JTAG 配置模式外，还支持高云半导体特有的 GowinCONFIG 配置模式。每款器件支持的 GowinCONFIG 配置模式的多少取决于不同型号和封装形式。器件支持比特流数据加密和安全位设置功能，为用户设计提供了安全性保障。晨熙<sup>®</sup>(Arora)家族 FPGA 产品支持比特流数据的解压缩功能，用户可以将比特流数据进行压缩以节约存储空间。

高云半导体 FPGA GW2AN-18X/9X 产品内置 16M-bit Serial Flash (With Quad SPI) 存储器，支持最大 100MHz Quad SPI 模式配置，支持 Fixed-Address GOLDEN-IMAGE 模式。

GW2AN-18X/9X FPGA 产品支持的配置模式如表 3-1 所示。

**表 3-1 配置模式**

| 配置模式        | MODE[1:0] <sup>[1]</sup> |                   | 相关说明                                                                                        |

|-------------|--------------------------|-------------------|---------------------------------------------------------------------------------------------|

| JTAG        | XX <sup>[2]</sup>        |                   | 外部 Host 通过 JTAG 接口对 FPGA 产品进行配置。最高频率 62.5MHz。                                               |

| GowinCONFIG | MSPI                     | 00                | FPGA 作为 Master，通过 SPI 协议从内置 Flash 读取配置数据进行配置。最高支持 100MHz。                                   |

|             | Autoboot                 | 01                | FPGA 作为 Master，通过 QSPI 协议从内置 Flash 读取配置数据进行配置。支持 GOLDEN IMAGE。最高支持 100MHz。                  |

|             | SSPI                     | 0X <sup>[3]</sup> | 在 Autoboot 或 MSPI 完成后自动支持。外部 Host 通过 SPI 协议对 FPGA 产品进行配置。最高支持 100MHz。                       |

|             | QSSPI                    |                   | 在 Autoboot 或 MSPI 完成后自动支持。外部 Host 通过 QSPI 协议对 FPGA 产品进行配置。最高支持 100MHz。                      |

|             | I <sup>2</sup> C         |                   | 在 Autoboot 或 MSPI 完成后自动支持。外部 Host 通过 I <sup>2</sup> C 协议对 FPGA 产品进行配置。支持频率范围 100KHz~555KHz。 |

| 配置模式 |                       | MODE[1:0] <sup>[1]</sup> | 相关说明                             |

|------|-----------------------|--------------------------|----------------------------------|

|      | SERIAL <sup>[4]</sup> | 10                       | 外部 Host 通过 DIN 接口对 FPGA 产品进行配置。  |

|      | CPU <sup>[4]</sup>    | 11                       | 外部 Host 通过 DBUS 接口对 FPGA 产品进行配置。 |

**注！**

- [1]对于一些 MODE 管脚没有全部封装出来的器件，未封装出来的 MODE 值请参考对应封装的 pinout 手册；

- [2]JTAG 配置模式与 MODE[1:0]输入值无关；

- [3]SSPI 配置模式与 MODE[0]输入值无关；

- [4]CPU 配置模式的 SCLK、WE\_N 和 CLKHOLD\_N 管脚与 SERIAL 配置模式共用，CPU 配置模式的数据总线管脚与 MSPI 和 SSPI 配置模式的管脚共用。

**注！**

关于配置管脚列表、配置管脚复用及配置管脚功能及应用信息请参考 **4 配置管脚介绍**。

# 4 配置管脚介绍

高云半导体 **FPGA** 产品配置模式多样，包括通用型的 **JTAG** 配置、主动配置、被动配置、串行配置和并行配置等，可以满足用户不同外设环境下的各种需求。编程配置相关的管脚既能够完成配置功能，又可以设置为普通的 I/O，用户可根据实际使用情况进行选择。用户也可以根据配置管脚的功能对其进行灵活控制，满足一些特殊需求。

## 4.1 配置管脚列表及复用选项

### 4.1.1 配置管脚列表

高云半导体 **FPGA** 产品所有与配置相关的管脚如表 4-1 所示，表中也标注了每种配置模式使用到的管脚及芯片封装过程中的管脚共用情况。

**表 4-1 配置管脚列表**

| 管脚名称          | I/O 类型 | JTAG | GowinCONFIG |                  |      |       |        |     |

|---------------|--------|------|-------------|------------------|------|-------|--------|-----|

|               |        |      | AUTO BOOT   | I <sup>2</sup> C | SSPI | QSSPI | SERIAL | CPU |

| RECONFIG_N    | I      | √    | √           | √                | √    | √     | √      | √   |

| JTAGSEL_N     | I      | √    |             |                  |      |       |        |     |

| TDO           | O      | √    |             |                  |      |       |        |     |

| TMS           | I      | √    |             |                  |      |       |        |     |

| TCK           | I      | √    |             |                  |      |       |        |     |

| TDI           | I      | √    |             |                  |      |       |        |     |

| READY         | I/O    | √    | √           | √                | √    | √     | √      | √   |

| DONE          | I/O    | √    | √           | √                | √    | √     | √      | √   |

| MODE[1:0]     | I      |      | √           | √                | √    | √     | √      | √   |

| SCLK          | I      |      |             |                  | √    | √     | √      | √   |

| CLKHOLD_N/DIN | I      |      |             |                  | √    | √     | √      | √   |

| WE_N/DOUT     | O      |      |             |                  |      | √     | √      | √   |

| D7            | I/O    |      |             |                  |      |       |        | √   |

| 管脚名称         | I/O 类型 | JTAG | GowinCONFIG |                  |      |       |        |     |

|--------------|--------|------|-------------|------------------|------|-------|--------|-----|

|              |        |      | AUTO BOOT   | I <sup>2</sup> C | SSPI | QSSPI | SERIAL | CPU |

| D6           | I/O    |      |             |                  |      |       |        | √   |

| D5           | I/O    |      |             |                  |      |       |        | √   |

| D4           | I/O    |      |             |                  |      |       |        | √   |

| FASTRD_N/D3  | I/O    |      |             |                  |      |       |        | √   |

| SI/D2        | I/O    |      |             | √                | √    |       |        | √   |

| SO/D1        | I/O    |      |             | √                | √    |       |        | √   |

| SSPI_CS_N/D0 | I/O    |      |             | √                | √    |       |        | √   |

| SCL          | I      |      | √           |                  |      |       |        |     |

| SDA          | I/O    |      | √           |                  |      |       |        |     |

注!

- 不同型号和封装的器件支持的配置模式不同，详细信息请参考 3 配置模式；

- 关于不同配置模式下各管脚的定义请参考 5 配置模式介绍。

## 4.1.2 配置管脚复用

为最大化地提高 I/O 的利用率，高云半导体的 FPGA 产品支持将配置管脚设置为普通 I/O 使用。所有系列的 FPGA 上电后未进行任何配置操作之前，与配置相关的管脚均默认作为配置管脚使用。配置成功后，器件进入用户模式，按照用户选择的复用选项重新分配管脚的功能。

注!

用户设置管脚复用选项时，需确保管脚的外部初始连接状态不影响器件的配置过程。对于影响配置的连接，需要先进行隔离处理，等待 FPGA 进入用户模式后再进行修改。

配置管脚复用选项如表 4-2 所示。

表 4-2 配置管脚复用选项

| 设置名称                  | 设置选项      | 说明                                                                                                                                                                     |

|-----------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG PORT             | 默认状态      | TMS, TCK, TDI, TDO 作为专用配置管脚，JTAGSEL_N 作为 GPIO。                                                                                                                         |

|                       | 设置为普通 I/O | JTAGSEL_N 作为专用配置管脚：<br><ul style="list-style-type: none"> <li>● JTAGSEL_N=0, TMS,TCK,TDI,TDO 作为配置管脚；</li> <li>● JTAGSEL_N=1, TMS,TCK,TDI,TDO 在配置结束后作为 GPIO。</li> </ul> |

| I <sup>2</sup> C PORT | 默认状态      | SCL,SDA 作为专用配置管脚。                                                                                                                                                      |

|                       | 设置为普通 I/O | SCL,SDA 在配置结束后作为 GPIO。                                                                                                                                                 |

| SSPI PORT             | 默认状态      | SCLK, CLKHOLD_N, SSPI_CS_N, SI 和 SO 作为专用配置管脚。                                                                                                                          |

|                       | 设置为普通 I/O | SCLK, CLKHOLD_N, SSPI_CS_N, SI 和 SO 在配置结束后作为 GPIO。                                                                                                                     |

| QSSPI PORT            | 默认状态      | SCLK, CLKHOLD_N, SSPI_CS_N, SI 和 SO 作为专用配置管脚。                                                                                                                          |

| 设置名称       | 设置选项      | 说明                                                           |

|------------|-----------|--------------------------------------------------------------|

|            |           | SO、QSSPI_WPN 作为专用配置管脚。                                       |

|            | 设置为普通 I/O | SCLK, CLKHOLD_N, SSPI_CS_N, SI 和 SO、QSSPI_WPN 在配置结束后作为 GPIO。 |

| RECONFIG_N | 默认状态      | 专用配置管脚。                                                      |

|            | 设置为普通 I/O | 配置结束后作为 GPIO。                                                |

| READY      | 默认状态      | 专用配置管脚。                                                      |

|            | 设置为普通 I/O | 配置结束后作为 GPIO。                                                |

| DONE       | 默认状态      | 专用配置管脚。                                                      |

|            | 设置为普通 I/O | 配置结束后作为 GPIO。                                                |

### 注!

- [1]对于 JTAGSEL\_N 未封装出来的器件，在调试 JTAG 管脚复用的案例时，建议用户在 FPGA 上电前确保当前 MODE 值不会使 FPGA 进行配置操作，以避免其他比特流数据影响配置过程。用户上电后手动进行 JTAG 配置后，器件进入用户模式，JTAG 管脚变为 GPIO。

- [2]SERIAL 和 CPU 配置模式的管脚由于与其他配置模式共用，无法单独设置为 GPIO，但是当这些管脚工作在非共用配置模式时可以设置为 GPIO。

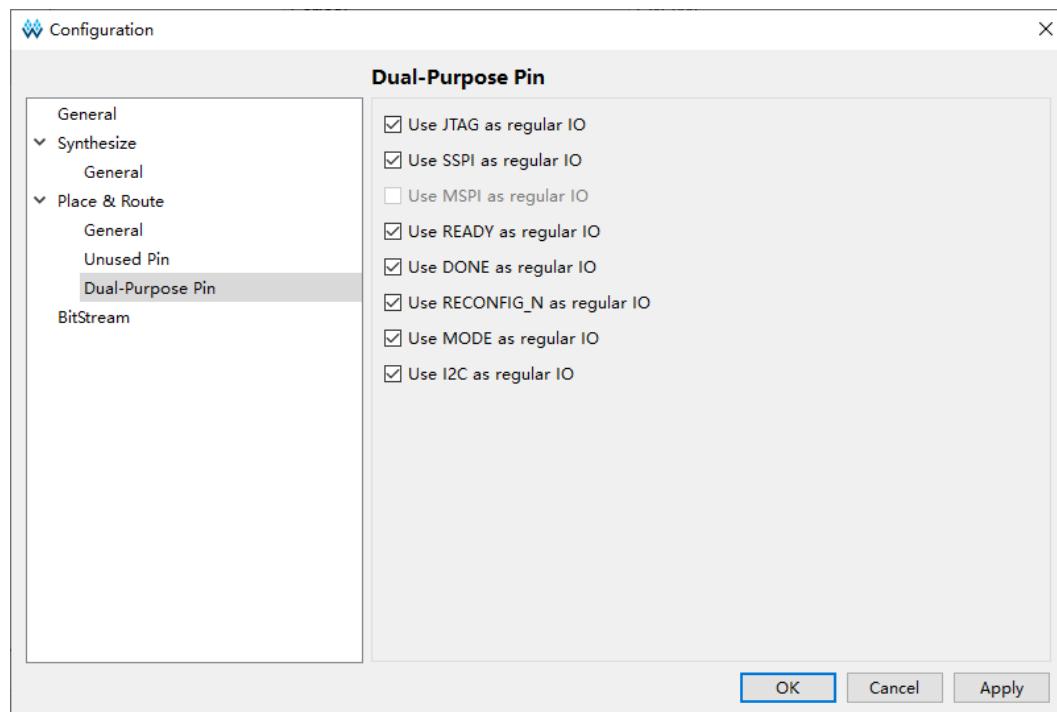

## 配置管脚复用

通过 Gowin 云源软件配置管脚复用：

1. 打开 Gowin 云源软件中相应的工程；

2. 在菜单栏中选择“Project>Configuration>Dual-Purpose Pin”，如图 4-1 所示；

3. 勾选对应选项设置配置管脚的复用情况。

图 4-1 配置管脚复用设置

## 4.2 配置管脚功能及应用

**RECONFIG\_N**、**READY** 和 **DONE** 管脚是每种模式都会用到的管脚。其他配置管脚可根据具体应用设置为配置专用管脚或普通管脚。

表 4-3 管脚功能

| 管脚名称              | 功能描述                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>RECONFIG_N</b> | 作为配置管脚时，类型为输入，具有内部弱上拉。低电平有效，相当于 <b>FPGA</b> 编程配置的复位功能， <b>RECONFIG_N</b> 拉低时 <b>FPGA</b> 无法进行任何方式的配置操作。 <b>FPGA</b> 上电过程中务必保持高电平，上电稳定 <b>1ms</b> 之后可以释放。<br>作为配置管脚时，需要一个脉冲宽度不少于 <b>25ns</b> 的低电平启动 <b>GowinCONFIG</b> 配置模式，使器件按照 <b>MODE</b> 设置值重新加载比特流数据。用户也可以通过编写逻辑控制此管脚，从而按照自身需求触发器件进行重新配置；作为 <b>GPIO</b> 时，只能用作 <b>output</b> 类型。为保障配置过程顺利进行，用户复用 <b>RECONFIG_N</b> 管脚时需将其初始值置为高电平。                                                                           |

| <b>READY</b>      | <b>inout</b> 类型管脚。高电平有效，只有 <b>READY</b> 拉高时 <b>FPGA</b> 才能进行配置操作， <b>READY</b> 信号拉低后采用器件上电或触发 <b>RECONFIG_N</b> 的方式恢复状态。<br>作为配置管脚时，若为 <b>output</b> 类型，可以指示 <b>FPGA</b> 当前能否进行配置：当器件具备配置条件时， <b>READY</b> 信号为高电平；若配置失败，则 <b>READY</b> 信号变为低电平。若为 <b>input</b> 类型，用户可通过自身逻辑或在器件外部人为拉低 <b>READY</b> 信号以延迟配置过程。<br>作为 <b>GPIO</b> 时，可用作 <b>input</b> 或 <b>output</b> 类型。 <b>READY</b> 用作 <b>input</b> 类型的 <b>GPIO</b> 时需保证配置开始前其初始值为 <b>1</b> ，否则 <b>FPGA</b> 无法进行配 |

| 管脚名称             | 功能描述                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>DONE</b>      | <p>置。</p> <p><b>inout</b> 类型管脚。FPGA 配置成功的标志信号，配置成功后 <b>DONE</b> 信号拉高。<br/>作为配置管脚时，若为 <b>output</b> 类型，可以指示 FPGA 当前配置过程是否成功：当配置成功时，<b>DONE</b> 信号为高电平，器件进入工作状态；配置过程未完成或配置失败时，<b>DONE</b> 信号保持低电平状态。若为 <b>input</b> 类型，用户可通过自身逻辑或在器件外部人为拉低 <b>DONE</b> 信号以延迟其进入用户模式。<b>RECONFIG_N</b> 或 <b>READY</b> 保持低电平状态时，<b>DONE</b> 信号也会保持在低电平状态。使用 JTAG 电路配置 SRAM 的过程中，<b>DONE</b> 信号的值没有参考意义。</p> <p>作为 GPIO 时，可用作 <b>input</b> 或 <b>output</b> 类型。<b>DONE</b> 用作 <b>input</b> 类型的 <b>GPIO</b> 时需保证配置开始前其初始值为 <b>1</b>，否则配置结束后 <b>FPGA</b> 无法进入用户模式。</p> |

| <b>MODE</b>      | <p><b>GowinCONFIG</b> 配置模式选择信号。作为配置管脚时，类型为输入，内部弱下拉，最多可达 <b>2-bit</b> 位宽。FPGA 上电或低电平脉冲触发 <b>RECONFIG_N</b> 时，器件根据 <b>MODE</b> 值进入相应的 <b>GowinCONFIG</b> 状态，高云半导体每个系列的 <b>FPGA</b> 产品 <b>MODE</b> 值对应的配置模式略有不同。由于每个封装类型的管脚数目不同，有些器件的 <b>MODE</b> 管脚未完全封装出来，未封装出来的 <b>MODE</b> 值请参考对应的 <b>pinout</b> 手册，具体请参考相应器件的 <b>PINOUT</b> 手册。</p> <p><b>MODE</b> 管脚作为 <b>GPIO</b> 时，可用作 <b>input</b> 或 <b>output</b> 类型。<br/>需要注意的是，当 <b>MODE</b> 值改变时，需要重新上电或低电平触发 <b>RECONFIG_N</b> 才能生效。</p>                                                            |

| <b>JTAGSEL_N</b> | <p>作为配置管脚时，类型为输入，内部弱下拉。如果在云源软件中设置了 JTAG 管脚复用为 <b>GPIO</b>，则器件上电后进行一次成功的配置后 JTAG 管脚变为 <b>GPIO</b>，JTAG 配置功能失效，用户可通过拉低 <b>JTAGSEL_N</b> 进行恢复；如果用户未设置 JTAG 管脚复用，则 JTAG 配置功能一直可用。作为 <b>GPIO</b> 时，可用作 <b>input</b> 或 <b>output</b> 类型。<br/><b>注！</b><br/><b>JTAGSEL_N</b> 管脚与 JTAG 配置的 4 个管脚（<b>TCK</b>、<b>TMS</b>、<b>TDI</b>、<b>TDO</b>）设置为 <b>GPIO</b> 时存在互斥关系：<b>JTAGSEL_N</b> 设置为 <b>GPIO</b> 时，JTAG 管脚只能作为配置管脚；JTAG 管脚设置为 <b>GPIO</b> 时，<b>JTAGSEL_N</b> 只能作为配置管脚。</p>                                                                        |

| <b>TCK</b>       | <p>作为配置管脚时，类型为输入。<br/>JTAG 配置模式的串行时钟输入管脚。作为 <b>GPIO</b> 时，可用作 <b>input</b> 或 <b>output</b> 类型。</p>                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <b>TMS</b>       | <p>作为配置管脚时，类型为输入，内部弱上拉。<br/>JTAG 配置模式的串行模式输入管脚。作为 <b>GPIO</b> 时，可用作 <b>input</b> 或 <b>output</b> 类型。</p>                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>TDI</b>       | <p>作为配置管脚时，类型为输入，内部弱上拉。<br/>JTAG 配置模式的串行数据输入管脚。作为 <b>GPIO</b> 时，可用作 <b>input</b> 或 <b>output</b> 类型。</p>                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>TDO</b>       | <p>作为配置管脚时，类型为输出。<br/>JTAG 配置模式的串行数据输出管脚。作为 <b>GPIO</b> 时，可用作 <b>input</b> 或</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 管脚名称             | 功能描述                                                                                                                                                                                                                                                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | <b>output</b> 类型。                                                                                                                                                                                                                                   |

| <b>SCLK</b>      | 作为配置管脚时，类型为输入。<br><b>SSPI、SERIAL 和 CPU</b> 配置模式的时钟输入管脚。作为 GPIO 时，可用作 <b>input</b> 或 <b>output</b> 类型。                                                                                                                                               |

| <b>CLKHOLD_N</b> | 作为配置管脚时，类型为输入，内部弱下拉。<br><b>SSPI</b> 和 <b>CPU</b> 配置模式的时钟锁定管脚：在 <b>SSPI</b> 模式下，高电平有效；在 <b>CPU</b> 模式下，低电平有效。作为 GPIO 时，可用作 <b>input</b> 或 <b>output</b> 类型。                                                                                          |

| <b>SSPI_CS_N</b> | 作为配置管脚时，类型为输入，内部弱上拉。 <b>SSPI</b> 配置模式的片选信号，低电平有效。作为 GPIO 时，可用作 <b>input</b> 或 <b>output</b> 类型。                                                                                                                                                     |

| <b>SI</b>        | 作为配置管脚时，类型为输入。 <b>SSPI</b> 配置模式的串行数据输入管脚。作为 GPIO 时，可用作 <b>input</b> 或 <b>output</b> 类型。                                                                                                                                                             |

| <b>SO</b>        | 作为配置管脚时，类型为输出。 <b>SSPI</b> 配置模式的串行数据输出管脚。作为 GPIO 时，可用作 <b>input</b> 或 <b>output</b> 类型。                                                                                                                                                             |

| <b>QSSPI_WPN</b> | 作为配置管脚时，类型为输出。 <b>QSSPI</b> 配置模式的串行数据输出管脚。作为 GPIO 时，可用作 <b>input</b> 或 <b>output</b> 类型。                                                                                                                                                            |

| <b>FASTRD_N</b>  | 作为配置管脚时，类型为输入。<br><b>MSPI</b> 配置模式读取 <b>SPI Flash</b> 速度选择信号：当 <b>FASTRD_N</b> 为高电平时为普通读取模式（指令 <b>0x03</b> ）；当 <b>FASTRD_N</b> 为低电平时为高速读取模式，各个厂家的 <b>Flash</b> 高速读取操作指令不同，具体请参考相应 <b>Flash</b> 的数据手册。作为 GPIO 时，可用作 <b>input</b> 或 <b>output</b> 类型。 |

| <b>WE_N</b>      | 作为配置管脚时，类型为输入。<br><b>CPU</b> 配置模式的读写使能信号选择管脚：当 <b>WE_N</b> 为高电平时表示读操作；当 <b>WE_N</b> 为低电平时表示写操作。作为 GPIO 时，可用作 <b>input</b> 或 <b>output</b> 类型。                                                                                                       |

| <b>D0~D7</b>     | <b>inout</b> 类型管脚。<br><b>CPU</b> 配置模式的数据输入输出管脚，8-bit 位宽。根据 <b>WE_N</b> 的值确定 <b>D0~D7</b> 的输入输出方向。作为 GPIO 时，可用作 <b>input</b> 或 <b>output</b> 类型。                                                                                                     |

| <b>DIN</b>       | 作为配置管脚时，类型为输入，内部弱下拉。<br><b>SERIAL</b> 配置模式的串行数据输入管脚。作为 GPIO 时，可用作 <b>input</b> 或 <b>output</b> 类型。                                                                                                                                                  |

| <b>DOUT</b>      | 作为配置管脚时，类型为输出。<br><b>SERIAL</b> 配置模式的串行数据输出管脚，只在 <b>FPGA</b> 级联时用作后一个器件的输入。作为 GPIO 时，可用作 <b>input</b> 或 <b>output</b> 类型。                                                                                                                           |

| <b>SCL</b>       | 作为配置管脚时，类型为 <b>input</b> 。作为 GPIO 时，只可作 <b>input</b> 类型。                                                                                                                                                                                            |

| <b>SDA</b>       | 作为配置管脚时，类型为 <b>in/out</b> 。作为 GPIO 时，可用作 <b>input</b> 或 <b>output</b> 类型。                                                                                                                                                                           |

# 5 配置模式介绍

高云半导体 **FPGA GW2AN-18X/9X** 产品属于内置 Flash 的非易失器件。基于 **SRAM** 工艺的器件掉电后器件内部的配置数据丢失，每次上电后需重新配置；内置 **Flash** 的非易失器件掉电后数据仍然存储在芯片内部，重新上电时可以通过自启动配置或双启动配置的方式由器件自动进行重新配置。

高云半导体 **FPGA** 产品封装类型丰富，每一种封装的器件支持的配置模式与封装出来的配置管脚数目有关：所有器件均支持通用的 JTAG 配置；每种配置模式的 **MODE** 值有所差异。

## 5.1 配置须知

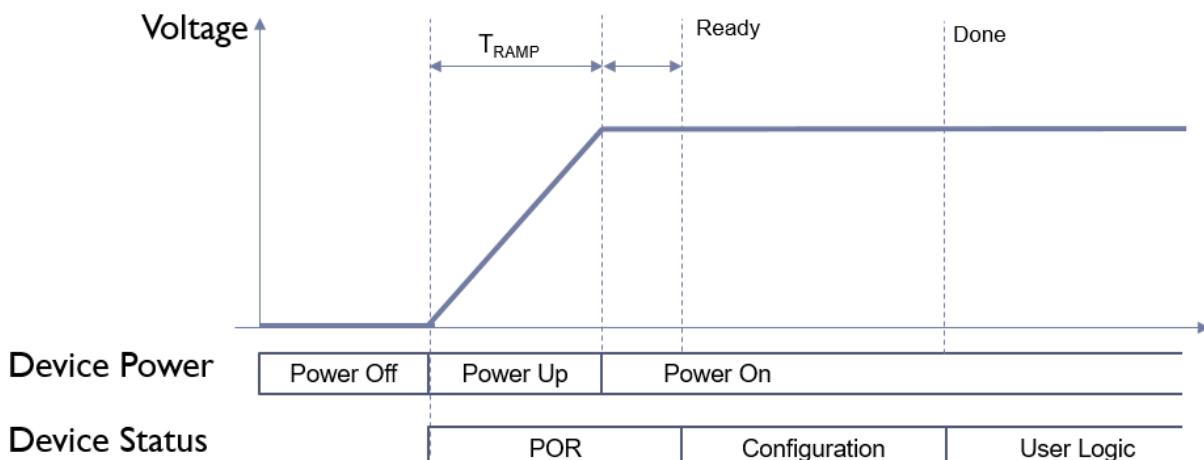

### 上电及配置流程

当 **FPGA** 的 **VCC**、**VCCIO**、**VCCX** 供电电压满足最小供电幅值时，**FPGA** 进入启动流程：电压稳定且 **RECONFIG\_N** 未被外部电路拉低>**FPGA** 内部电路拉低 **READY** 和 **DONE** 管脚>**FPGA** 初始化>**READY** 拉高并采样 **MODE** 值>根据配置模式读取配置数据并校验>**FPGA** 唤醒>**DONE** 拉高>进入用户模式。

**FPGA** 启动过程中需要保持供电稳定，**FPGA** 上电稳定后的 1ms 之内以及 **FPGA** 初始化过程中 **RECONFIG\_N** 管脚不允许出现低电平，用户可选择将 **RECONFIG\_N** 管脚悬空或外部上拉。**FPGA** 唤醒前所有普通 I/O 输出高阻态。

高云半导体 **FPGA GW2AN-18X/9X** 产品按照配置数据的存储和指令的作用位置分为对 **SRAM** 的操作和对内置 **Flash** 的操作。

### SRAM 操作

对 **SRAM** 的操作包括读取器件 **ID CODE** 和 **USER CODE**，读取器件状态寄存器信息以及 **SRAM** 配置。器件 **ID** 验证是配置操作的前提，只有 **ID** 验证成功的器件才能进行配置；**USER CODE** 是为方便用户对 **ID CODE** 相同的多个器件加以区分进行的编号标识；器件的状态寄存器记录着 **FPGA** 配置前后的状态信息，用户可据此分析器件状态，状态寄存器的含义请参考表 5-8。

SRAM 配置操作时需要注意，只有未设置安全位的比特流数据支持验证功能。设置了安全位的数据任何用户无法进行回读验证。

### 内置 Flash 操作

对内置 Flash 的操作包括擦除、编程和验证操作。可通过 JTAG、SSPI、QSSPI、I<sup>2</sup>C 等接口操作内置 Flash，JTAG 时钟速率不大于 65MHz，SSPI、QSSPI 时钟速率不大于 100MHz，I<sup>2</sup>C 时钟速率 100KHz~555KHz。

所有接口模式都支持透明传输的特性，即器件支持在不影响现有工作状态下编程内置 Flash 的操作，编程过程中器件可以按照原有的配置正常工作，编程完成后，低电平触发 RECONFIG\_N 或发送 RECONFIG 指令即可完成在线升级。此特性适合应用于在线时间长但又需要不定期升级的场所。

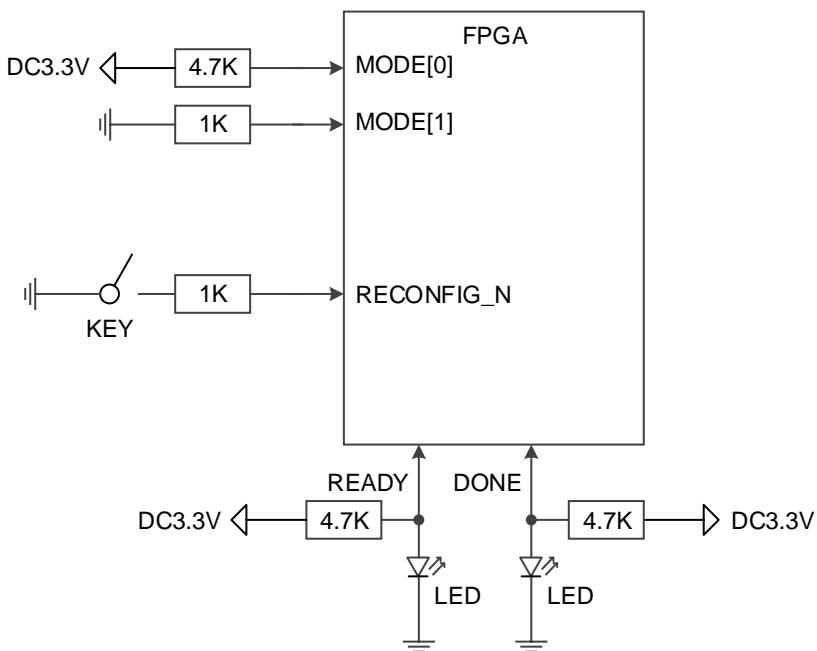

### 配置管脚复用

用户在使用不同配置模式时，需要根据配置管脚的作用，确保 FPGA 工作在已选择的配置模式下。用户端管脚数目不足时，可以通过其他连接方式灵活处理这些管脚，只保留数据传输相关的管脚即可。**MODE[1:0]** 用来选择 GowinCONFIG 的编程配置模式，用户不需要改变模式时可以使用上拉或下拉的方式将其固定在特定的模式，上拉电阻推荐 4.7K，下拉电阻推荐 1K。

注！

RECONFIG\_N、READY 和 DONE 管脚与每种配置模式相关，无论用户是否将它们设置为 GPIO，都需要保证在配置操作完成前它们的初始值或管脚连接状态满足编程配置条件。

### 固定管脚推荐接法

用户进行电路原理图设计时，推荐接法如图 5-1 所示。

图 5-1 固定管脚推荐接法

注！

- 用户需要改变 MODE 值时可增加拨码开关；部分器件 MODE 管脚未完全封装出来，未封装的 MODE 管脚请查阅 [UG972, GW2AN-18X 器件 Pinout 手册](#) 及 [UG978, GW2AN-9X 器件 Pinout 手册](#)；

- JTAG 配置过程中 READY 和 DONE 信号的值没有参考意义；

- RECONFIG\_N、READY 和 DONE 未封装出来的管脚已内部处理，不影响配置功能。

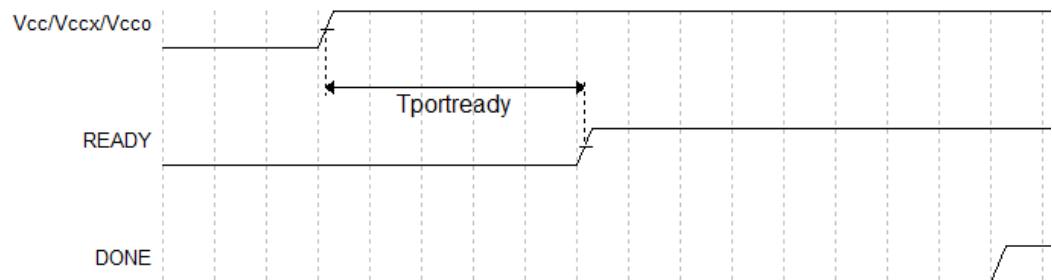

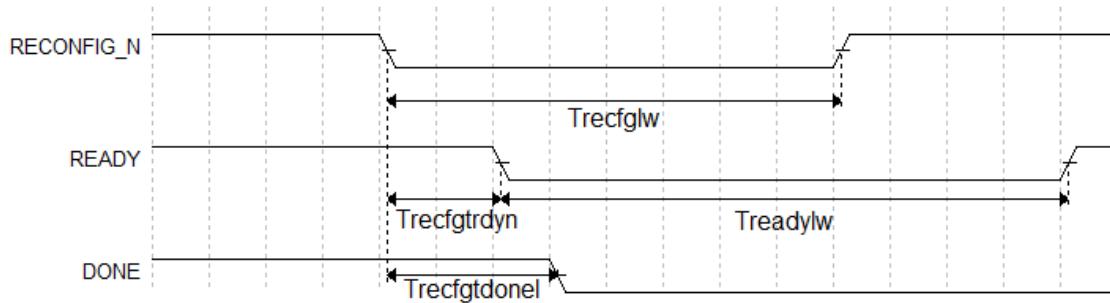

### 重新上电及低电平脉冲触发 RECONFIG\_N 时序图

重新上电和低电平脉冲触发 RECONFIG\_N 的时序图如图 5-2 和图 5-3 所示。

图 5-2 重新上电时序图

图 5-3 触发时序图

晨熙®(Arora)家族 FPGA 产品相关的时序参数如表 5-1 所示。

表 5-1 高云半导体 FPGA GW2AN-18X/9X 产品重新上电和 RECONFIG\_N 触发时序参数

| 参数名称                    | 参数含义                                                                                                                                 | 最小值  | 最大值  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|------|

| T <sub>portready</sub>  | 满足上电条件到 READY 的上升沿的时延 (Time from application of V <sub>cc</sub> , V <sub>ccx</sub> and V <sub>cco</sub> to the rising edge of READY) | -    | 23ms |

| T <sub>recfglw</sub>    | RECONFIG_N 低电平脉冲宽度 (RECONFIG_N low pulse width)                                                                                      | 25ns | -    |

| T <sub>recfgtrdyn</sub> | RECONFIG_N 下降沿到 READY 变低电平的时延 (Time from RECONFIG_N falling edge to READY low)                                                       | -    | 70ns |

| T <sub>readylw</sub>    | READY 低电平脉冲宽度 (READY low pulse width)                                                                                                | TBD  | -    |

| T <sub>cfgtdonel</sub>  | RECONFIG_N 下降沿到 DONE 变低电平的时延 (Time from RECONFIG_N falling edge to DONE low)                                                         | -    | 80ns |

## 5.2 AUTO BOOT 配置

AUTO BOOT 配置模式，是高云半导体针对非易失 FPGA 产品的瞬时接通特性推出的一种配置模式。自启动模式下，芯片上电后无需连接外部配置接口，FPGA 即可自行以默认 100MHz 的频率从内置 Flash 的地址 0x000000，以 Quad SPI 协议读取比特流数据完成配置。GW2AN-18X/9X 系列 FPGA 支持两次自启动配置，即上电后自启动配置失败时，器件可以自动从 0x100000 地址进行第二次配置操作。导致配置失败的因素包括 ID 验证错误，CRC 校验错误、指令错误、超时错误等。

用户使用自启动模式时，首先需要将配置数据编程到 FPGA 的内置 Flash 中，当系统重新上电或低电平脉冲触发 RECONFIG\_N 管脚时，芯片会自动读取比特流数据完成配置过程。内置 Flash 的瞬时接通特性为配置过程节约了下载时间，提高了工作效率。

AUTOBOOT 模式需要将 MODE[1:0]设置为“01”，若配置失败，器件依旧可以使用 JTAG、I<sup>2</sup>C、SSPI、QSSPI 等协议配置 SRAM 或 Flash。

## 5.3 JTAG 配置

高云半导体 FPGA 产品的 JTAG 配置模式符合 IEEE1532 标准和 IEEE1149.1 边界扫描标准。

JTAG 配置模式是将比特流数据写入到高云半导体 FPGA 产品的 SRAM 中，掉电后配置数据丢失。高云半导体所有封装的 FPGA 产品均支持 JTAG 配置模式。

### 5.3.1 JTAG 配置模式管脚

JTAG 配置模式的相关管脚如表 5-2 所示。

表 5-2 JTAG 配置模式管脚定义

| 管脚名称             | I/O 类型   | 说明                             |

|------------------|----------|--------------------------------|

| JTAGSEL_N        | I, 内部弱下拉 | 将 JTAG 管脚从 GPIO 恢复为配置管脚, 低电平有效 |

| TCK <sup>1</sup> | I, 内部弱下拉 | JTAG 串行时钟输入                    |

| TMS              | I, 内部弱上拉 | JTAG 串行模式输入                    |

| TDI              | I, 内部弱上拉 | JTAG 串行数据输入                    |

| TDO              | O, 内部弱上拉 | JTAG 串行数据输出                    |

注!

[1] TCK 需在 PCB 上连接 4.7K 下拉电阻。

### 5.3.2 JTAG 配置模式连接示意图

JTAG 配置模式器件连接关系如图 5-4 所示。

图 5-4 JTAG 配置模式连接示意图

注!

JTAG 配置模式时钟频率不能高于 65MHz。

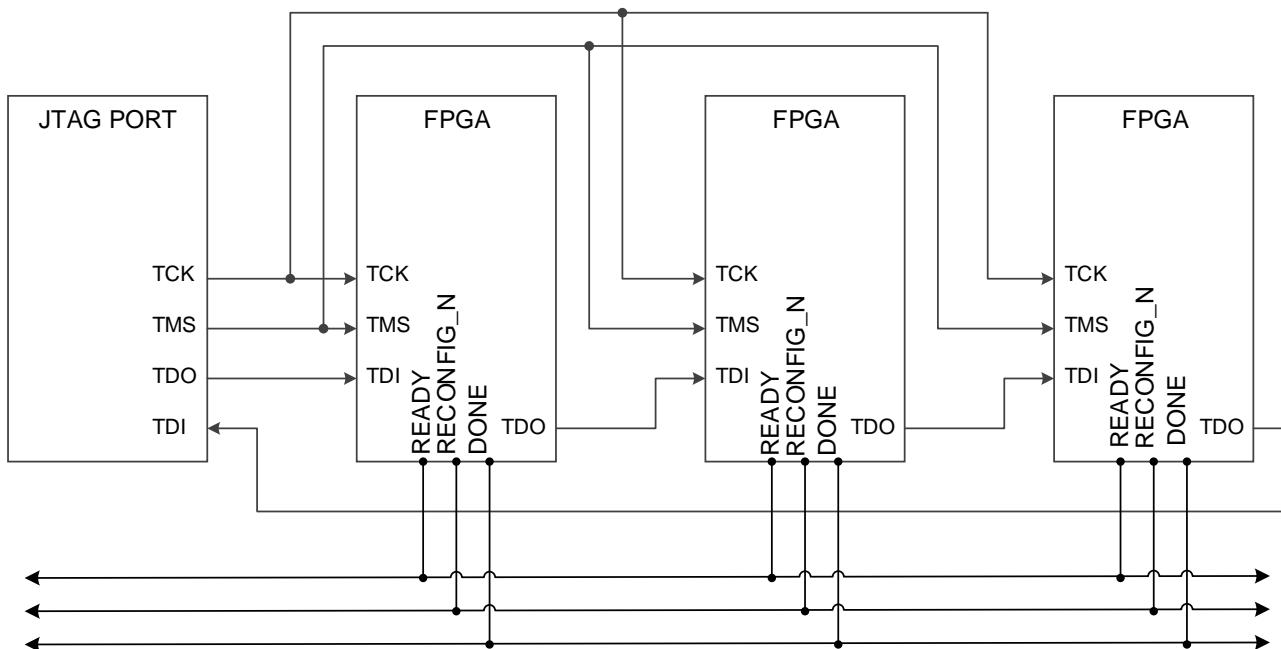

高云半导体 FPGA 产品支持 JTAG 菊花链操作，即，把一个 FPGA 的 TDO 管脚连接到下一个 FPGA 的 TDI 管脚，Gowin 编程软件会自动识别连接在一起的 FPGA 器件，依次进行配置。菊花链配置的连接示意图如图 5-5 所示。注意，高云半导体 FPGA GW2AN-18X/9X 产品不支持配置菊花链上的 FPGA 内置 Flash。

图 5-5 JTAG 菊花链配置模式连接示意图

注!

DONE、RECONFIG\_N 及 READY 信号视情况决定是否连接。

### 5.3.3 JTAG 配置模式时序图

JTAG 配置模式的时序图如图 5-6 所示。

图 5-6 JTAG 配置模式时序图

图中各个参数的含义如表 5-3 所示。

表 5-3 JTAG 配置模式时序参数

| 参数名称          | 参数含义                                                          | 最小值  | 最大值  |

|---------------|---------------------------------------------------------------|------|------|

| $T_{tckftco}$ | TCK 下降沿到输出数据时延 (Time from TCK falling edge to output)         | -    | 10ns |

| $T_{tckftcx}$ | TCK 下降沿到输出高阻时延 (Time from TCK falling edge to high impedance) | -    | 10ns |

| $T_{tckp}$    | TCK 时钟周期 (TCK clock period)                                   | 40ns | -    |

| $T_{tckh}$    | TCK 时钟高电平时间 (TCK clock high time)                             | 20ns | -    |

| $T_{tckl}$    | TCK 时钟低电平时间 (TCK clock low time)                              | 20ns | -    |

| $T_{jps}$     | JTAG PORT 建立时间 (JTAG PORT setup time)                         | 10ns | -    |

| $T_{jph}$     | JTAG PORT 保持时间 (JTAG PORT hold time)                          | 8ns  | -    |

### 5.3.4 JTAG 相关配置流程

#### TAP 状态机

测试访问口状态机旨在选择指令寄存器或数据寄存器，使其连接至 TDI 和 TDO 之间。一般来说，指令寄存器用于选择需扫描的数据寄存器，在状态机框图中，位于箭头一侧的数字表示 TCK 变高时 TMS 的逻辑状态，如图所示。

图 5-7 TAP 状态机

### TAP 复位

通过保持 TMS 为高电平（逻辑“1”）并在 TCK 端输入至少 5 个选通脉冲（变高后再变低）后，复位 TAP 逻辑，从而实现将处于其它状态的 TAP 状态机转换成测试逻辑复位状态，对 JTAG 接口和测试逻辑复位。

**注！**

该状态不复位 CPU 和外设。

**注！**

- 在进入 Shift\_DR 或 Shift\_IR 状态时，TDO 上的数据从 TCK 的下降沿开始有效；

- 在进入 Shift\_DR 或 Shift\_IR 状态时，数据不移位；

- 在离开 Shift\_DR 或 Shift\_IR 时，数据被移位；

- 最先移出的是数据的最低位 LSB；

- 一旦复位，所有指令将被重置或失效。

### 指令寄存器和数据寄存器

除测试逻辑复位外，状态机亦可控制两个基本操作：

- 指令寄存器（IR）扫描；

- 数据寄存器（DR）扫描。

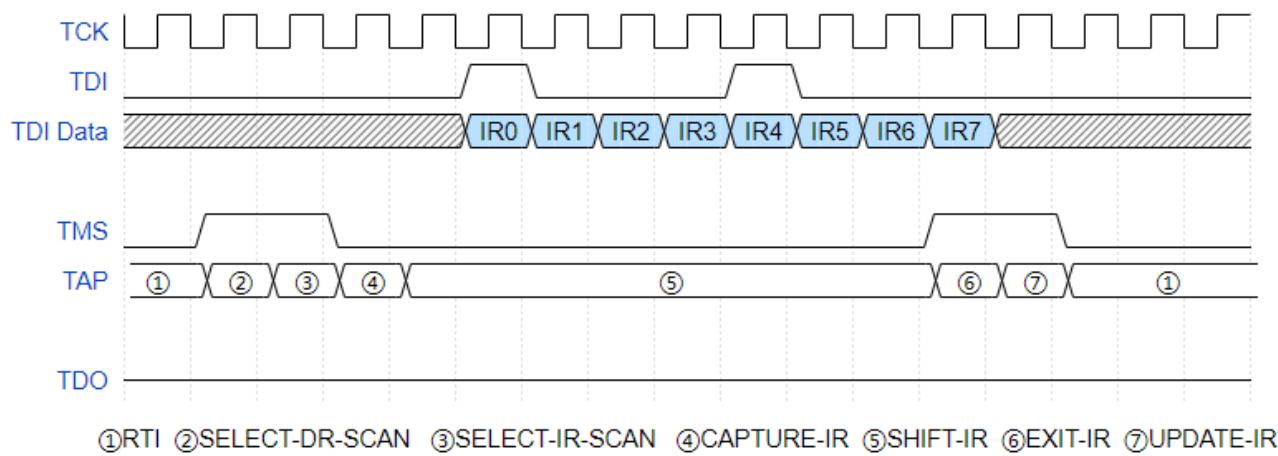

在指令寄存器扫描操作中，在 Shift\_IR 状态时，传送数据或指令给指令寄存器，发送时采用 LSB 的方式，低数据位首先被发送，回到 Run-Test-Idle 后指令即被发送完毕，如图 5-8 所示。

在数据寄存器扫描操作中，在 Shift\_DR 状态时，传送数据或指令给数据寄存器，如图 5-9 所示。数据发送采用 LSB 还是 MSB 取决于具体操作。

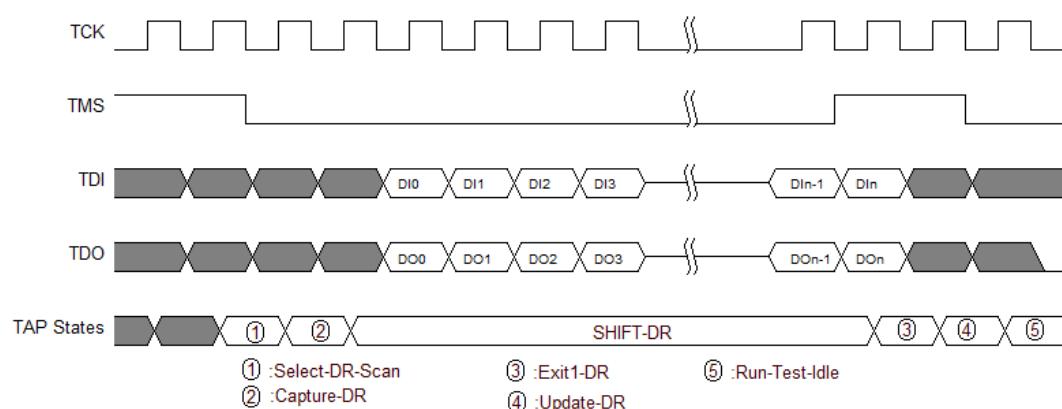

图 5-8 指令寄存器访问时序

图 5-9 数据寄存器访问时序

**注!**

- 指令寄存器的总长度为 8 位；

- 根据所选择的寄存器，数据寄存器的长度可变化。

## 读取 ID CODE 实例

ID Code 即 JEDEC ID Code，是 FPGA 器件的一个基本标识。

高云 FPGA ID Code 长度为 32 位，下表列出了高云部分 FPGA 的 ID Code。

**表 5-4 Gowin 部分 FPGA 产品 ID CODE**

| Gowin FPGA Device Family ID CODE |             |                 |           |

|----------------------------------|-------------|-----------------|-----------|

| Device Family                    | Device Part | Manufacturer ID | ID CODE   |

|                                  | Bits 31-12  | Bits 11-0       |           |

|                                  |             | h81B            |           |

| GW2AN-18X                        | h00004      | h81B            | h0000481B |

| GW2AN-9X                         | h00005      | h81B            | h0000581B |

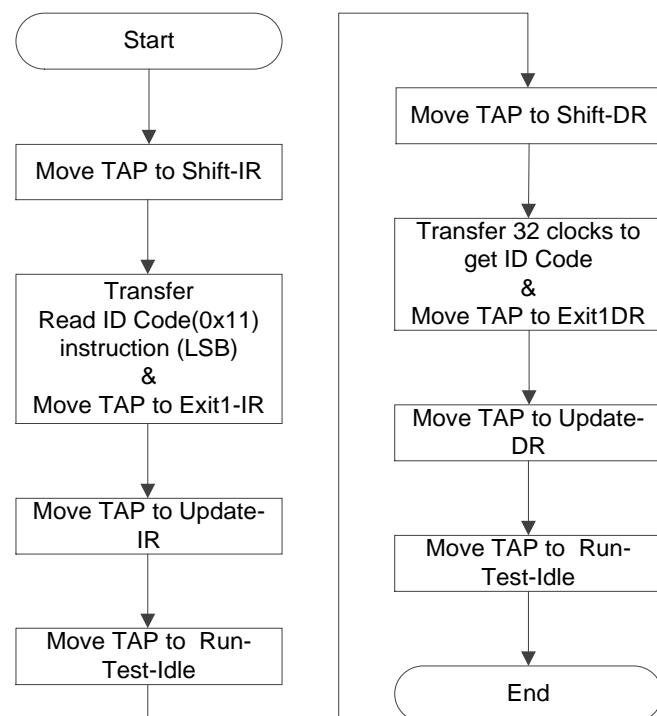

读取 FPGA 的指令是 0x11，以下步骤以读取 GW2AN-9X ID Code 为例说明 JTAG 的工作方式。

1. TAP 复位：TMS 置为高电平，连续发送至少 5 个时钟周期；

2. 移动状态机从 Test-Logic-Reset 到 Run-Test-Idle；

3. 移动状态机到 Shift-IR，从最低位开始发送 Read ID 指令 0x11，最高位（最后一位）发送的同时移动状态机到 Exit1-IR，即最高位发送前 TMS 要置于高电平，表 5-5 给出 8 个时钟周期内发送 0x11 过程中 TDI 和 TMS 的值变化，时序如图 5-11 所示。

**表 5-5 发送指令过程中 TDI 和 TMS 的值变化**

|                  | TCK 1 | TCK 2 | TCK 3 | TCK 4 | TCK 5 | TCK 6 | TCK 7 | TCK 8 |

|------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| TDI value (0x11) | 1     | 0     | 0     | 0     | 1     | 0     | 0     | 0     |

| TMS value        | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     |

4. 移动状态机，从 Exit1-IR 经过 Update-IR 后回到 Run-Test-Idle，并在 Run-Test-Idle 运行至少 3 个时钟周期；

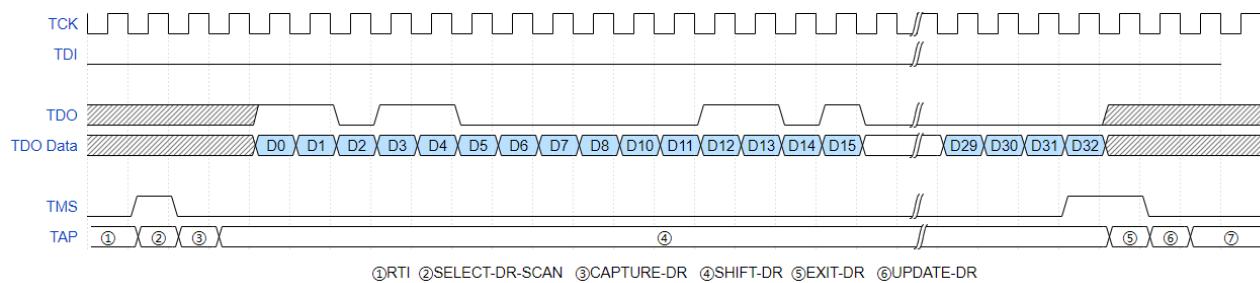

5. 移动状态机到 Shift-DR，发送 32 个时钟周期，并在第 32 个时钟发送前，置 TMS 为高电平，完成 32 个时钟周期的同时，跳出 Shift-DR 到 Exit1-DR。这期间，发送 32 个时钟即可读出 32bits 数据，即为 0x0100381B，如图 5-12 所示；

6. 移动状态回到 Run-Test-Idle。

图 5-10 读取 ID Code 状态机流程图

图 5-11 读取 ID Code 指令-0x11 访问时序

图 5-12 读取 ID Code(0x0000581B)数据寄存器访问时序

## 配置 SRAM 的流程

通过外部 Host 配置 FPGA SRAM，使 FPGA 实现功能，通过 JTAG 配置 SRAM 不受 Configuration Mode Pins 的影响。

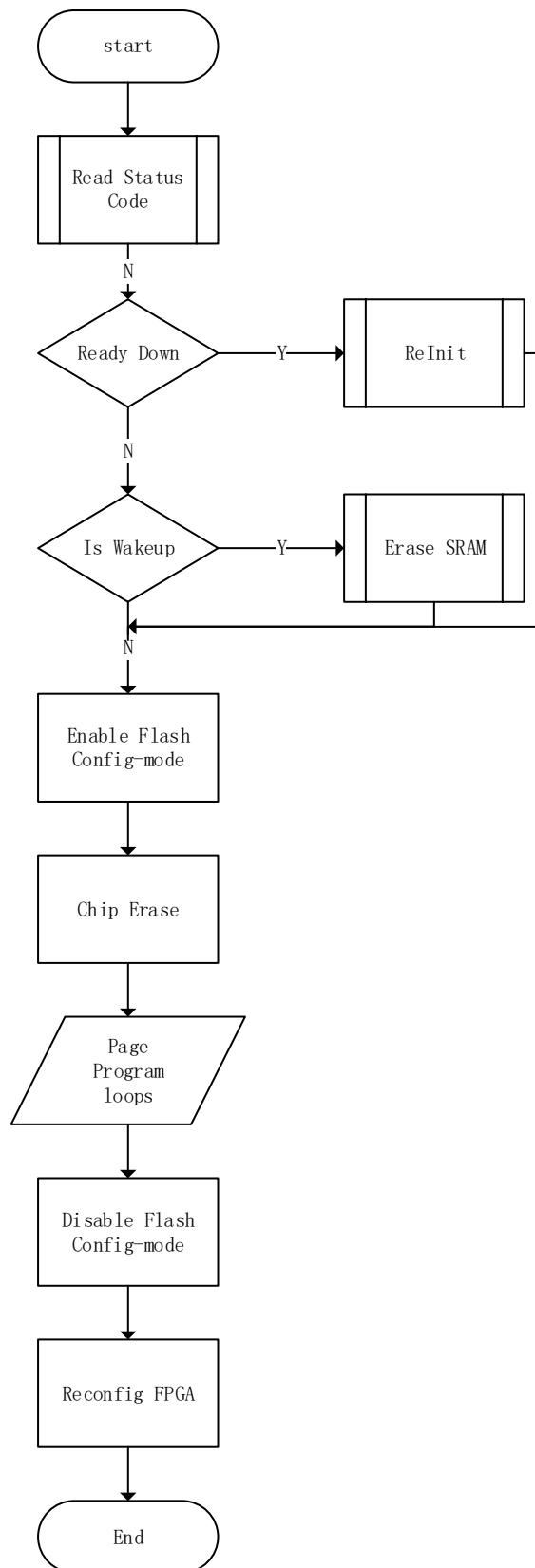

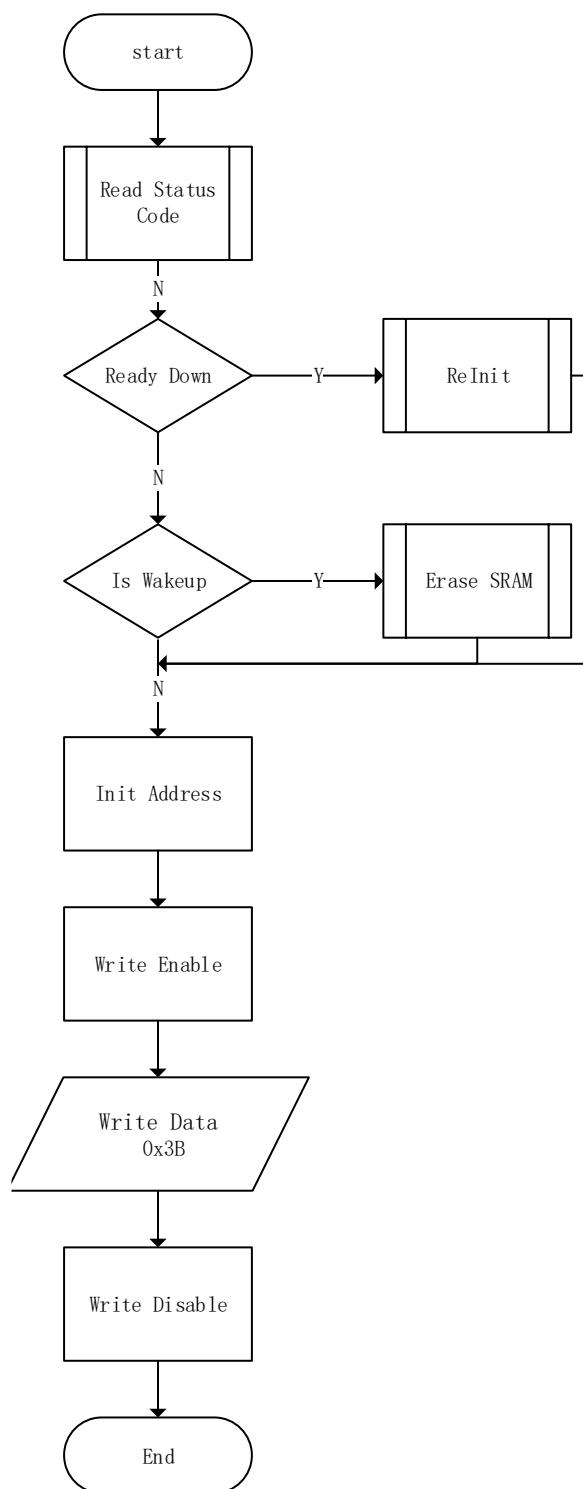

通过 Gowin software 设计软件生成数据流文件，利用 JTAG 实现 SRAM 的配置，下面介绍外部 Host 配置 SRAM 的过程，如图 5-13 所示。

1. 建立 JTAG 链路，TAP 复位；

2. 读取设备 ID Code，检查 ID CODE 是否匹配；

3. 读取设备 StatusCode，如 Ready 位为 0，发送 Reinit 指令 0x3F;或者当 SRAM 已被配置，擦除 SRAM，流程参考“[擦除 SRAM 的流程](#)”；

4. 发送 ConfigEnable 指令 0x15。

5. 发送 Address Initialize 指令 0x12；

6. 发送 Transfer Configuration Data 指令 0x17。

7. 移动状态到 Shift-DR（数据寄存器），将 Bitstream Data 从最高位开始（MSB），逐位发送，发送全部数据流文件内容，并回到 Run-Test-Idle 状态；

8. 发送 ConfigDisabled 指令 0x3A；

9. 发送 Noop 指令 0x02，结束配置流程。

10. 如需回读 Configuration Data 进行校验，请参考“[读取 SRAM 的流程](#)”。

图 5-13 配置 SRAM 流程

### 读取 SRAM 的流程

警告：处于数据保密设计，SRAM 数据默认不被允许回读。

从 FPGA 的 SRAM 区域读取 SRAM 数据，首先应保证写入 SRAM 时未配置安全位（Security Bit），安全位是用于保护运行时数据，保证数据安全。安全位完成设置后，从 SRAM 取回的数据均为 1（高电平）。

在加载过程中，FPGA 对写入数据进行 CRC 校验，以确保数据写入正

确，CRC 是否报错，可以作为配置 SRAM 的校验机制。

**表 5-6 器件 SRAM 地址数量和地址长度**

| Device       | Length of one address (bits/address) | Count of address |

|--------------|--------------------------------------|------------------|

| GW2AN-18X/9X | 3376                                 | 1342             |

下面详细介绍读取流程，如图 5-14 所示。

1. 发送 **ConfigEnable** 指令 0x15;

2. 发送 **Address Initialize** 指令 0x12;

3. 发送 **SRAM Read** 指令 0x03;

4. 移动状态机到 **Shift-DR**（数据寄存器），发送地址长度数量的时钟，请参见表 5-6。在发送最后一个时钟同时拉高 **TMS**，跳到 **Exit1-DR**，此时 **TDO** 读取相应长度的数据。最后回到 **Run-Test-Idle**;

5. 重复步骤 4，每次读取一个地址的数据，其地址会自动累加；

6. 发送 **ConfigDisabled** 指令 0x3A;

7. 发送 **Noop** 指令 0x02，结束读取流程；

图 5-14 读取 SRAM 的流程

### 擦除 SRAM 的流程

当重新配置 SRAM 时，需要擦除已存在的 SRAM。流程如下：

1. 发送 ConfigEnable 指令 0x15;

2. 发送 SRAM Erase 指令 0x05;

3. 发送 Noop 指令 0x02;

4. 延时或 Run Test 2~10ms;

5. 发送 SRAM Erase Done 指令 0x09;

6. 发送 ConfigDisabled 指令 0x3A;

## 7. 发送 Noop 指令 0x02，结束流程；

注！

- 在发送 EraseSram (0x05) 指令、Noop (0x02) 之后，要给足够的时间等待其擦除完毕；

- GW2AN-18X/9X 参考时间为 6ms；

## 内置 Flash 编程模式

高云半导体 FPGA GW2AN-18X/9X 产品内置 16 Mbit Serial Flash 存储器，JTAG 提供类 SPI 协议用来编程内置 Flash，最大操作频率支持 65MHz。

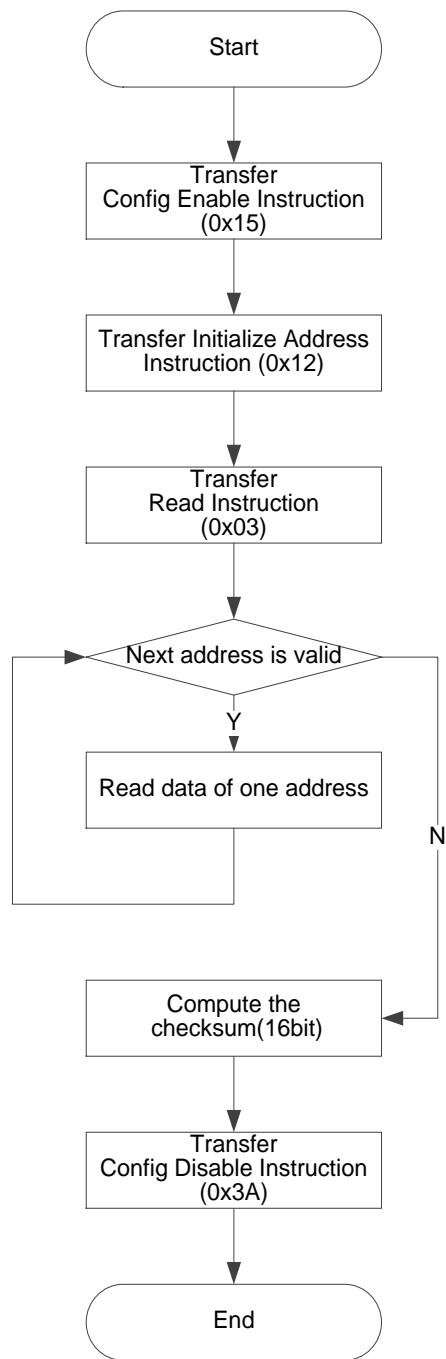

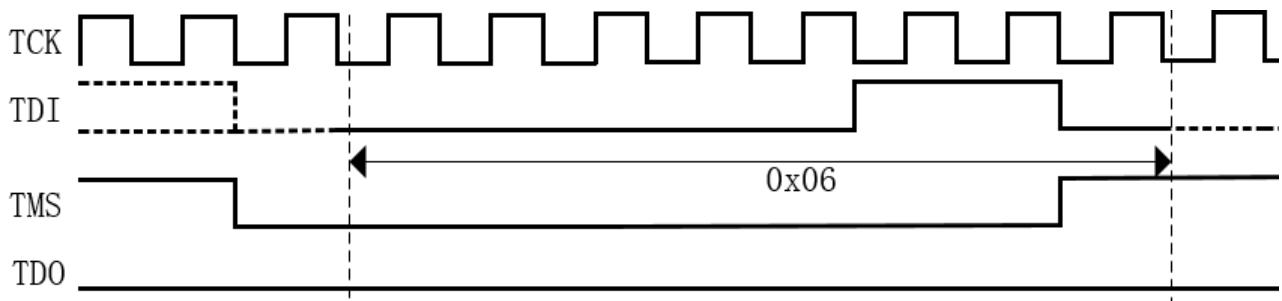

JTAG 提供的类 SPI 协议，总体与标准 SPI 逻辑一致，TMS 对应 ChipSelect (/CS) 信号，TDI 对应 DI 信号，TCK 对应 SerialClock (CLK) 信号，TDO 对应 DO 信号。时序也参考标准 SPI 对应时序，仅 TDI 数据向后位移一个时钟周期。当 TMS 拉低后，在发送一个 Clock 之后，才是有效的 DATA，并且 DATA 的最后一个 BIT 要与 TMS 一起拉高，示意图如下：

## 启用 Flash 编程模式

在编程 Flash 之前，需要将 JTAG 接口接通内部 Flash 控制器，发送标准 JTAG 指令 0x16，即可启用该模式，启用之后，JTAG 接口仅工作在 Flash 编程模式下，转为类 SPI 协议，不再支持 JTAG 指令。

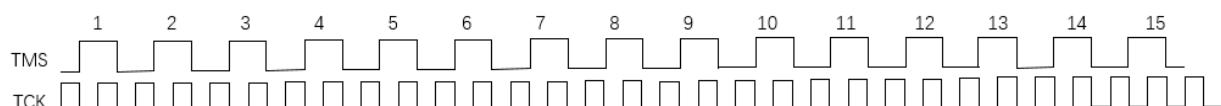

## 退出 Flash 编程模式

通过设置连续的 15 次 TMS 高低电平，即可退出 Flash 编程模式，即退出类 SPI 接口，恢复到 JTAG 标准接口，恢复 JTAG 协议对器件进行配置的模式。如下图：

### 内置 Flash 指令-WriteEnable (0x06)

WriteEnable 指令(上图)用来设置 Flash Status Register 的 Write Enable Latch (WEL) 位，WEL 位必须在每次 Page-Program、Sector Erase、Chip Erase 前设置。在 TMS 为低电平并在一个时钟周期(TCK)后，将指令“0x06”移入数据输入(TDI)引脚上，0x06 的最后一个 bit 位“0”跟随 TMS 在同一个时钟周期内完成。

### 内置 Flash 指令-WriteDisable (0x04)

WriteDisable 指令用于重置 Flash Status Register 的 Write Enable Latch (WEL) 位，在 TMS 为低电平并在一个时钟周期 (TCK) 后，将指令“0x04”移入数据输入 (TDI) 引脚上，0x04 的最后一个 bit 位“0”跟随 TMS 在同一个时钟周期内完成。

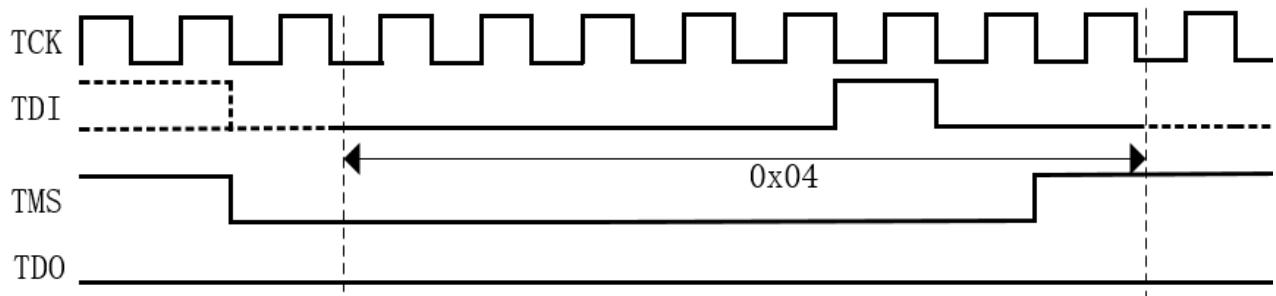

### 内置 Flash 指令-Read Status Register-1 (0x05)

Read Status Register-1 指令用于读取一个 8bit 状态寄存器，在 TMS 为低电平并在一个时钟周期 (TCK) 后，将指令“0x05”在 TCK 上升沿时候移入数据输入 (TDI) 引脚，再经历 2 个 dummy clock 后，Status Register-1

的数据将在 TCK 的下降沿从 TDO 管脚送出，最高有效位（MSB）在前。如下图。

**Read Status Register-1** 共 8 位，用 S[7:0]表示，其中 S[0]表示 BUSY 位，当 Flash 处于 Page-Program、Chip Erase、Sector Erase 等过程时，S[0]将被自动设置为 1。这个状态下 Flash 处于 BUSY 状态，不响应其他指令，当操作结束后，S[0]将自动重置为 0，可以继续发送其他指令。

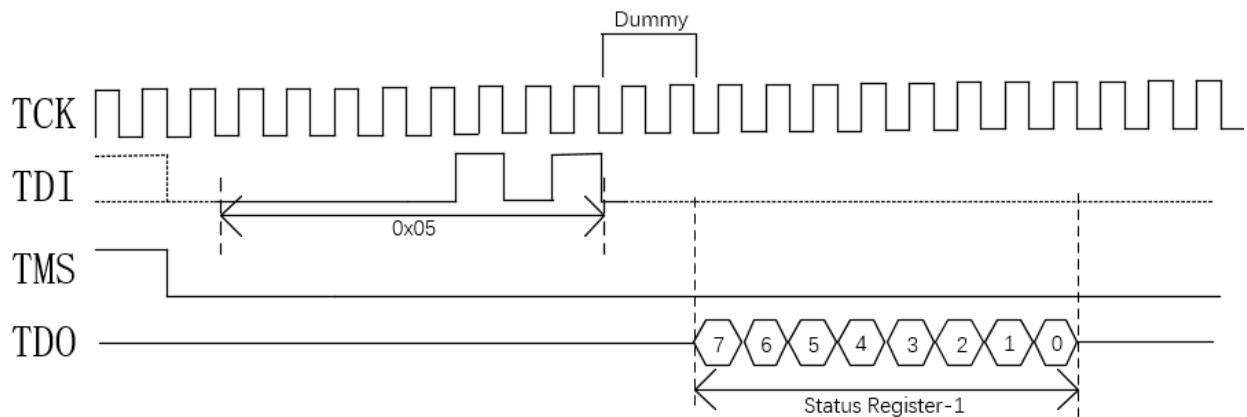

### 内置 Flash 指令-Read Data (0x03)

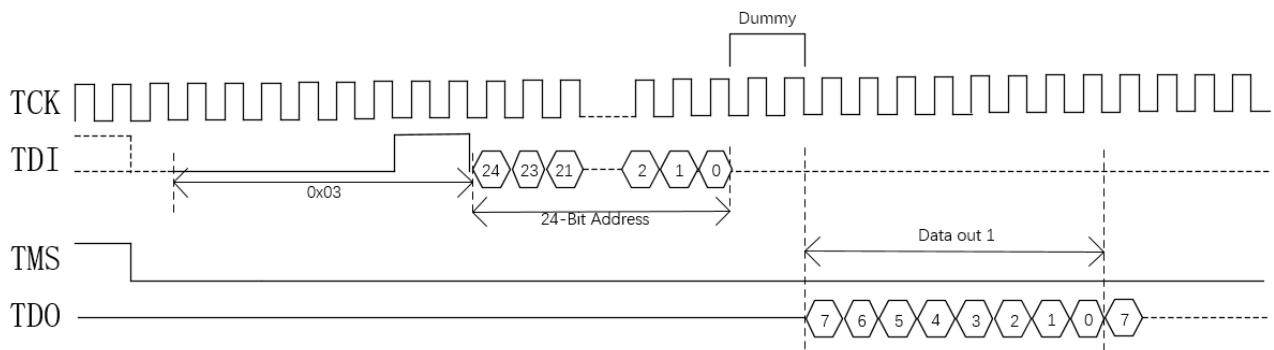

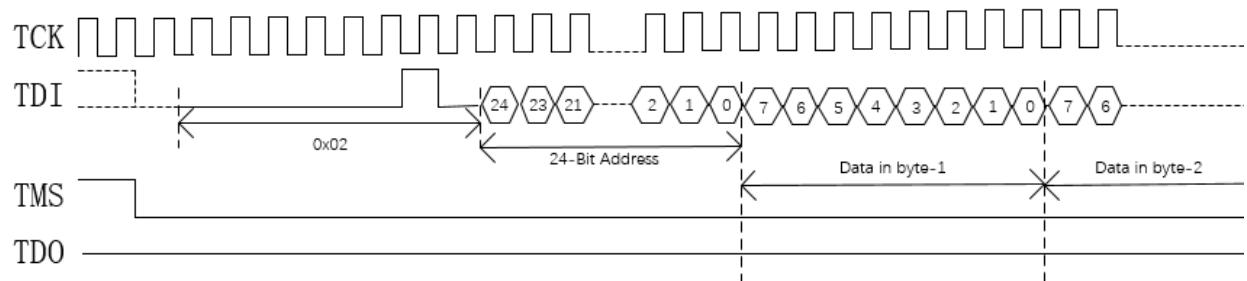

Read Data 指令用于从 Flash 中读取连续的数据，在 TMS 为低电平并在一个时钟周期（TCK）后，将指令“0x03”在 TCK 上升沿时候移入数据输入（TDI）引脚，然后将 24 位地址移入数据（DI）引脚，再经历 2 个 dummy clock 后，对应地址的数据将在 TCK 的下降沿从 TDO 管脚送出，最高有效位（MSB）在前。当回读的数据超过一个地址时，地址会自动递增，允许回读连续的数据流，也就是说一条指令可以读取整个 Flash 的数据。如下图。

### 内置 Flash 指令-Page Program (0x02)

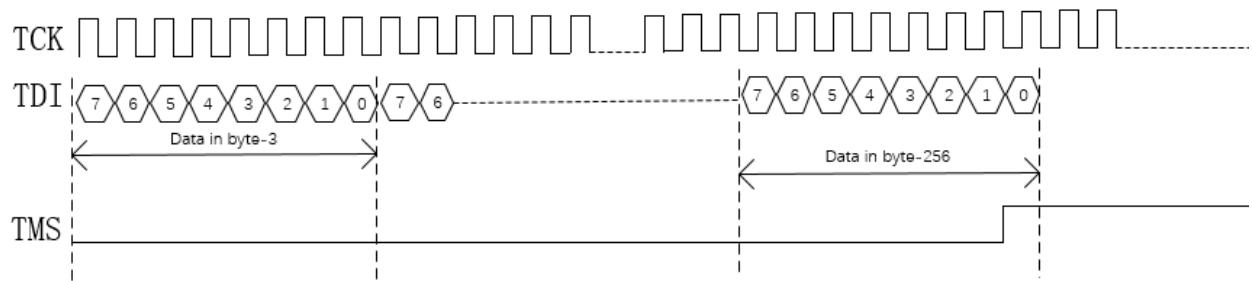

Page Program 指令用于烧录一个 page 上的一个或多个已被擦除(0xFF)的字节。在配置之前必须完成 WriteEnable 指令。指令在 TMS 为低电平并在一个时钟周期 (TCK) 后，将指令“0x02”在 TCK 上升沿时候移入数据输入 (TDI) 引脚，然后将 24 位地址移入数据 (DI) 引脚，然后按 MSB 方式将数据移入数据 (DI) 引脚。TMS 在此期间保持低电平，并在最后一个字节的最后一个 bit 位数据跟随 TMS 拉高时在同一个时钟周期内移入 DI 引脚。如下图：

### 内置 Flash 指令-Sector Erase (0x20)

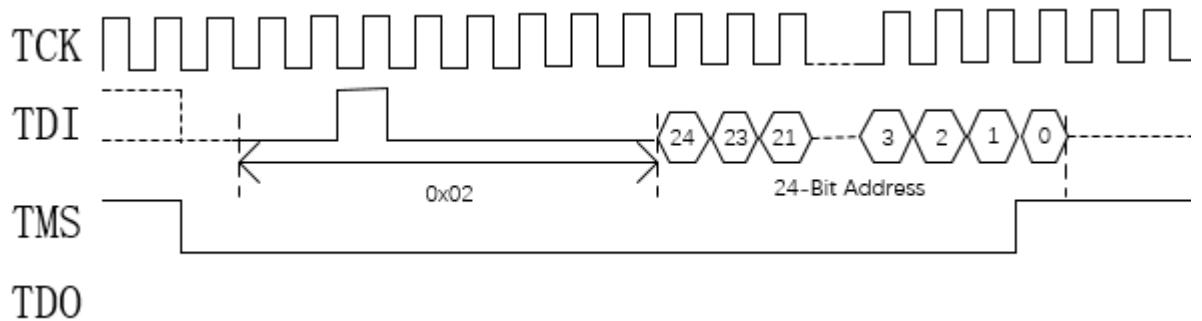

Sector Erase 指令用于擦除指定扇区 (4Kbytes) 内所有数据，擦除完成后 Flash 数据恢复到 0xFF 状态。在发送该指令之前，必须完成 WriteEnable 指令。指令在 TMS 为低电平并在一个时钟周期 (TCK) 后，将指令“0x20”在 TCK 上升沿时候移入数据输入 (TDI) 引脚，然后将 24 位地址移入数据 (DI) 引脚，在地址的最后一个 bit 时，同时将 TMS 设置为高电平。

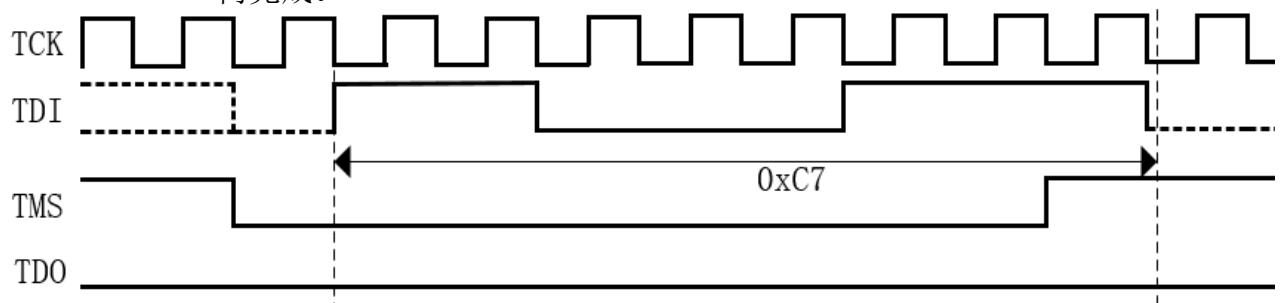

### 内置 Flash 指令-Chip Erase (0xC7/0x60)

Chip Erase 指令将擦除 Flash 内所有数据，擦除后所有数据为 1 (0xFF)。在发送该指令之前，必须完成 WriteEnable 指令。指令在 TMS 为低电平并在一个时钟周期 (TCK) 后，将指令“0xC7”在 TCK 上升沿时候移入数据输入 (TDI) 引脚，0xC7 的最后一个 bit 位“1”跟随 TMS 在同一个时钟周期内完成。

### 配置内置 Flash 流程图

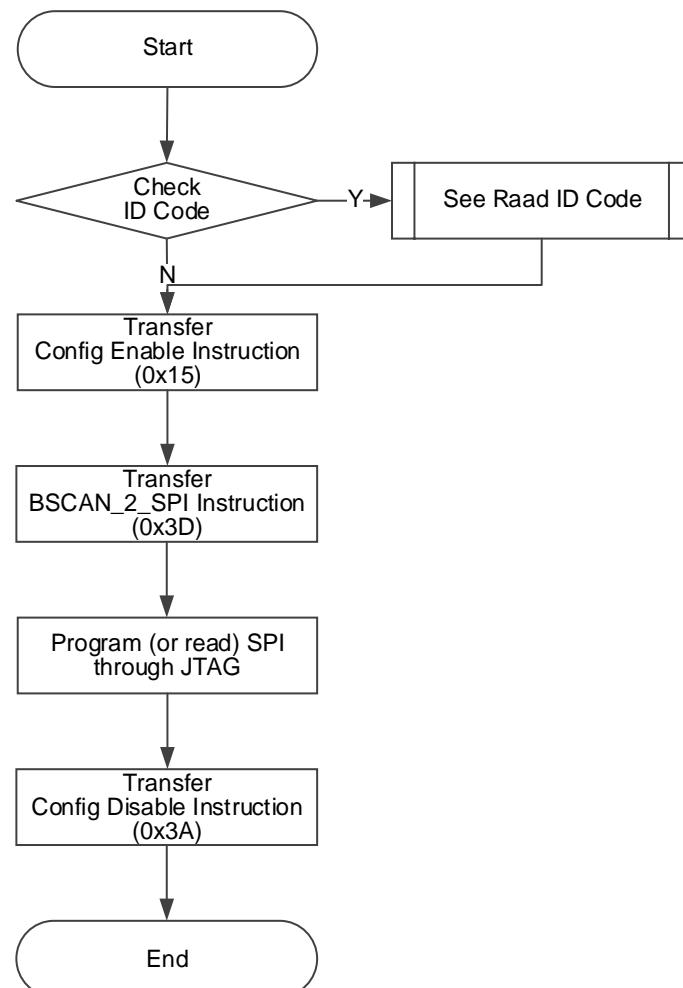

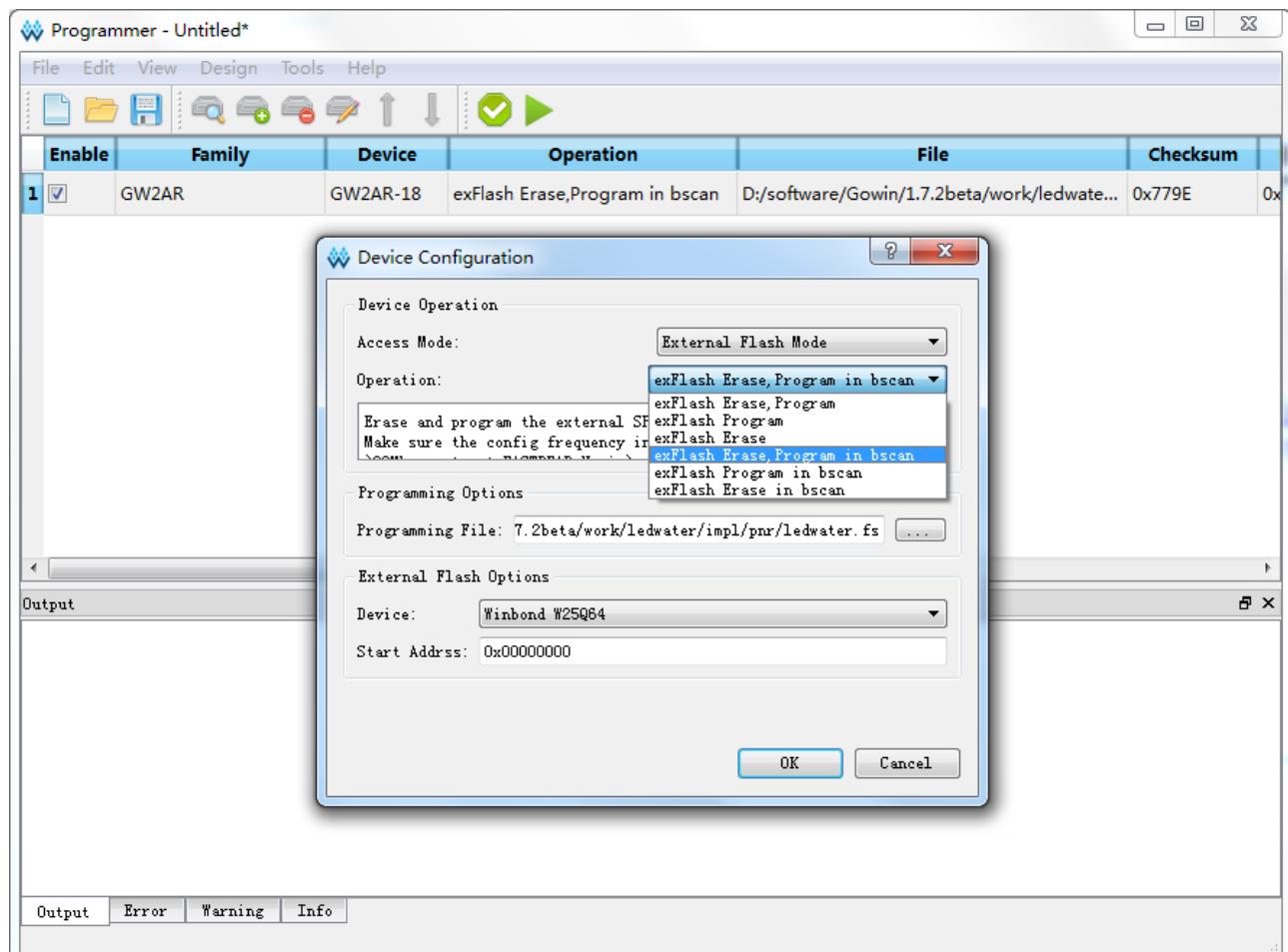

### JTAG Boundary Scan 模式烧录 SPI Flash

该模式的原理，是使用 Boundary Scan 的方式改变与 SPI 相连管脚的状态来实现 SSPI 时序，从而编程内部 Flash。

该模式采用的 Boundary Scan Chain 长度为 8 位，每 2 位组合对应管脚的状态，如表 5-7 所示，每发送两次 Boundary Scan Chain 完成一次 SCLK 驱动。

**表 5-7 管脚状态**

| Pins Name of SPI Flash | SCLK |   | CS |   | DI |   | DO |   |

|------------------------|------|---|----|---|----|---|----|---|

| Bscan Chain[7:0]       | 7    | 6 | 5  | 4 | 3  | 2 | 1  | 0 |

| (ctrl & data)          | 0    |   | 0  |   | 0  |   | 1  |   |

注！

- ctrl:0 表示输出，1 表示输入；

- data:0 表示低电平，1 表示高电平。

**图 5-15 采用 Boundary Scan 模式编程 SPI Flash 流程示意图**

### 读取 Status Register 0x41

Status Register 在器件调试和观察器件状态有很大帮助，通过读取 Status Register，可初步判断器件的状态，如判断是否成功 wakeup、是否存在加载错误等。Status Register 共有 32 位，读取指令是 0x41，时序与 Read ID Code 一致。

Status Register 的含义如表 5-8 所示。

表 5-8 Status Register 与配置加载相关的条目

| Device Status Register[31:0] | GW2AN-18X/9X                                 |

|------------------------------|----------------------------------------------|

| 0                            | CRC Error (1 表示发生错误，0 表示未发生错误)               |

| 1                            | Bad Command Error(1 表示发生错误，0 表示未发生错误)        |

| 2                            | ID Verify Failed Error(1 表示发生错误，0 表示未发生错误)   |

| 3                            | Timeout Error(1 表示发生错误，0 表示未发生错误)            |

| 4                            | Autoboot2nd Failed Error(1 表示发生错误，0 表示未发生错误) |

| 5                            |                                              |

| 6                            |                                              |

| 7                            |                                              |

| 8                            |                                              |

| 9                            | Autoboot1st Failed Error(1 表示发生错误，0 表示未发生错误) |

| 10                           |                                              |

| 11                           |                                              |

| 12                           |                                              |

| 13                           |                                              |

| 14                           |                                              |

| 15                           | Encrypted Format (1 表示使用了加密的数据流文件)           |

| 16                           | Encrypted Key Is Right (1 表示密钥正确，0 表示密钥错误)   |

| 17                           | sspi_mode,                                   |

| 18-31                        |                                              |

### 读取 User Code 0x13

User Code 共有 32 位，读取指令是 0x13，时序与 Read ID Code 一致。User Code 默认使用的是 FS 文件的 checksum 值，可在 Gowin Designer

中重新定义。

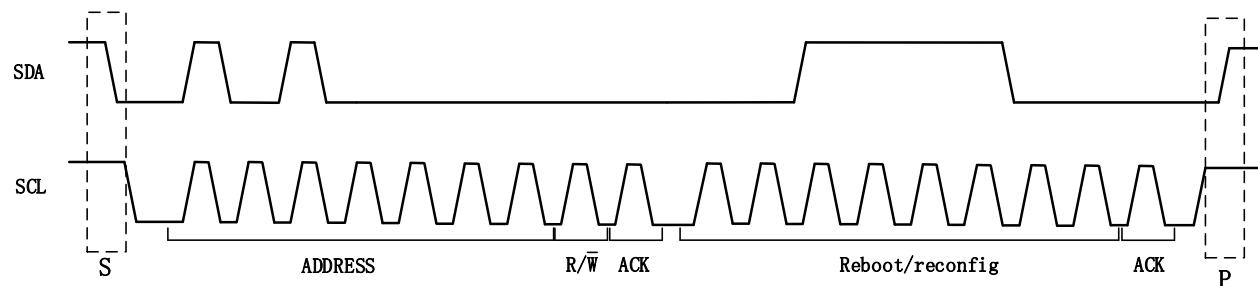

### 重加载 Reconfig 0x3C

该指令作用是使 FPGA 从 flash 中读取数据流文件，并配置到 SRAM。

通过 JTAG 依次发送 Reconfig (0x3C) 指令、Noop (0x02) 指令，可使器件重加载，效果同触发 Reconfig\_N 管脚。

### 菊花链连接示意图

图 5-16 菊花链连接示意图

### 例程文件

例程文件，请联系公司技术支持或当地办事处。

## 5.4 SSPI 配置模式

SSPI (Slave SPI) 配置模式，即 FPGA 作为从器件，由外部 Host 通过 SPI 接口对高云半导体 FPGA 产品进行配置的过程。

### 5.4.1 SSPI 配置模式管脚

SSPI 模式相关的配置管脚如表 5-9 所示。

表 5-9 SSPI 配置模式管脚

| 管脚名称       | I/O 类型        | 说明                                           |

|------------|---------------|----------------------------------------------|

| RECONFIG_N | I,<br>内部弱上拉   | 低电平脉冲：启动 GowinCONFIG 配置                      |

| READY      | I/O,<br>内部弱上拉 | 高电平：当前可以对 FPGA 进行编程配置<br>低电平：禁止对 FPGA 进行编程配置 |

| DONE       | I/O,          | 高电平：成功完成编程配置                                 |

| 管脚名称      | I/O 类型      | 说明                 |

|-----------|-------------|--------------------|

|           | 内部弱上拉       | 低电平：未完成编程配置或编程配置失败 |

| MODE[1:0] | I,<br>内部弱下拉 | 配置模式选择，READY 上升沿采样 |

| SCLK      | I,<br>内部弱上拉 | 输入时钟               |

| CLKHOLD_N | I,<br>内部弱下拉 | 高电平有效              |

| SO        | O,<br>内部弱下拉 | FPGA 输出数据到 Host    |

| SI        | I,<br>内部弱下拉 | Host 向 FPGA 输入数据   |

| SSPI_CS_N | I,<br>内部弱上拉 | SSPI 片选信号，低电平有效    |

注！

CLKHOLD\_N 默认状态为内部弱下拉，使用 SSPI 时请配置 CLKHOLD\_N 为高电平。

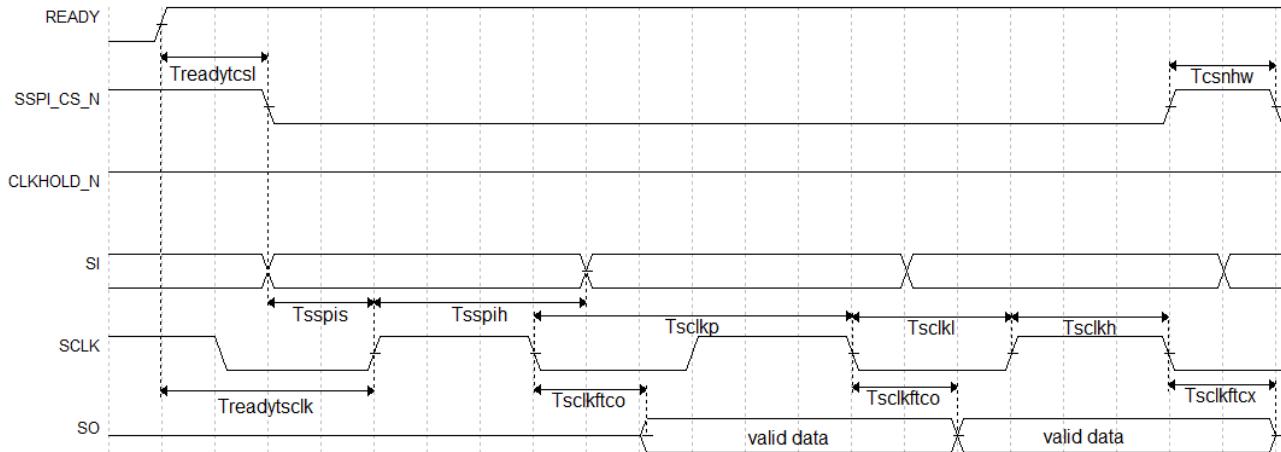

## 5.4.2 SSPI 配置模式时序图

SSPI 配置模式的时序图如图 5-17 所示。

图 5-17 SSPI 配置模式时序图

时序参数如表 5-10 所示。

表 5-10 SSPI 配置模式时序参数

| 参数名称                    | 参数含义                                                                   | 最小值   | 最大值  |

|-------------------------|------------------------------------------------------------------------|-------|------|

| T <sub>sclkp</sub>      | SCLK 时钟周期(SCLK clock period)                                           | 15ns  | -    |

| T <sub>sclkh</sub>      | SCLK 时钟高电平时间(SCLK clock high time)                                     | 7.5ns | -    |

| T <sub>sclkfco</sub>    | SCLK 时钟低电平时间(SCLK clock low time)                                      | 7.5ns | -    |

| T <sub>sspis</sub>      | SSPI PORT 建立时间(SSPI PORT setup time)                                   | 2ns   | -    |

| T <sub>sspih</sub>      | SSPI PORT 保持时间(SSPI PORT hold time)                                    | 0ns   | -    |

| T <sub>sclkftco</sub>   | SCLK 下降沿到数据输出时延(Time from SCLK falling edge to output)                 | -     | 10ns |

| T <sub>sclkftcx</sub>   | SCLK 下降沿到输出高阻时延(Time from SCLK falling edge to high impedance)         | -     | 10ns |

| T <sub>csnhw</sub>      | CSN 高电平脉冲宽度 (CSN high time)                                            | 25ns  | -    |

| T <sub>readytcs</sub>   | READY 上升沿到 CSN 低电平时间(Time from READY rising edge to CSN low)           | TBD   |      |

| T <sub>readytsclk</sub> | READY 上升沿到第一个 SCLK 沿时间(Time from READY rising edge to first SCLK edge) | TBD   | -    |

除满足上电要求外，SSPI 模式对高云半导体 FPGA 产品进行配置，还需满足以下条件：

- **SSPI 接口使能**

上电后初次配置或前一次配置时 RECONFIG\_N 未设置为普通 I/O 状态。

- **启动新的配置**

重新上电或低电平脉冲触发 RECONFIG\_N 管脚。

### 5.4.3 SSPI 配置指令

当 FPGA 处于 SSPI 模式时，通过 SSPI 可以烧录 FPGA SRAM 或者读取 ID CODE\USER CODE\STATUS CODE 等信息，也可以烧录外部存储设备（例如 SPI Flash）。

FPGA 的 SSPI 指令一般由 1-4 个字节组成，至少包含 1 个指令类字节和多个冗余信息字节，没有指定信息字节的情况下，冗余信息字节可以是任意数（下表用 0x00 表示）。

**表 5-11 配置指令**

| 指令名称                     | 完整指令（指令字节+冗余信息字节） |

|--------------------------|-------------------|

| Read ID Code             | 0x11000000        |

| Read User Code           | 0x13000000        |

| Read Status Code         | 0x41000000        |

| Reconfig/Reprogram       | 0x3C00            |

| Write Enable             | 0x1500            |

| Write Disable            | 0x3A00            |

| Write Data               | 0x3B              |

| Write Data with Quad SPI | 0x6B              |

| Program SPI Flash        | 0x1600            |

| Init Address             | 0x1200            |

| Erase SRAM               | 0x0500            |

| Reinit                   | 0x3F00            |

#### Read ID Code

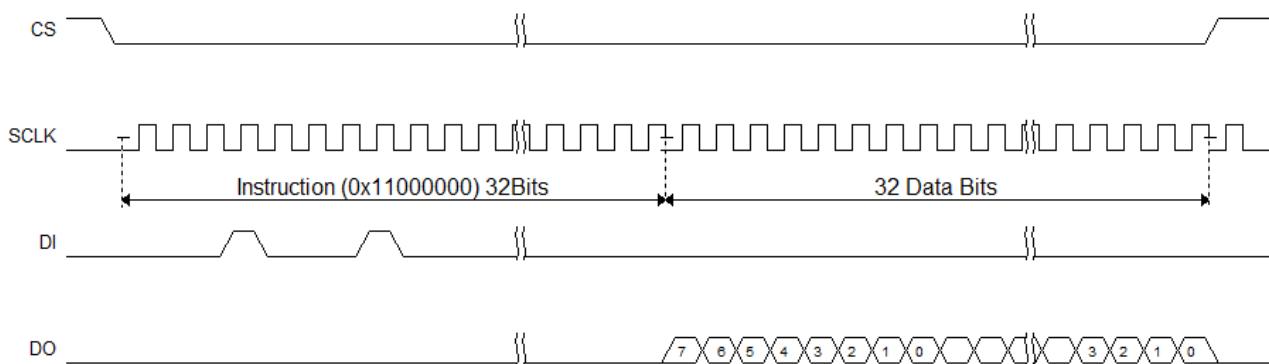

FPGA 的 ID Code 长度是 32bits，读取 ID 的指令是四个字节，即 0x11000000。在指令发送之前，使 CS 处于高电平状态，并且要在此状态产生若干时钟（两个时钟以上），以驱动 FPGA 获取 CS 状态。

当 CS 拉低之后，数据以 MSB 的方式写入指令 0x11000000，在写完四字节指令后要继续产生 32 个时钟，此时 ID CODE 数据将以 MSB 的形式从 DO 依次位移出来。

**图 5-18 读取 ID Code 时序示意图**

读取 StatusCode/UserCode 与读取 ID Code 的操作类似，替换对应的指令即可。

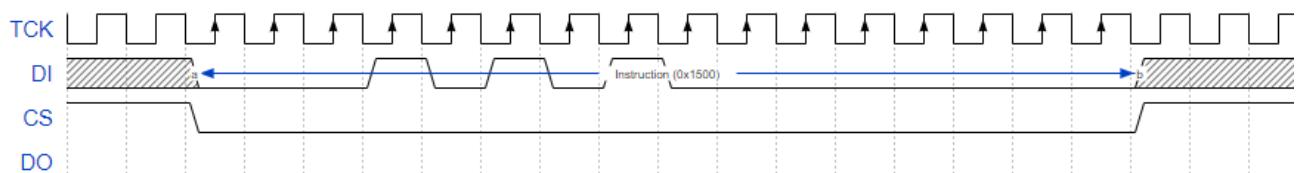

### Write Enable (0x1500)

在配置 SRAM（写 Features）前，使用 Write Enable（0x15）指令进入设备编辑模式，使设备可以接受写数据 Write Data（0x3B）指令。

图 5-19 Write Enable (0x15) 时序示意图

注！

SCLK 驱动规则，在 CS 高电平时，需要给予 SCLK 两个以上时钟，以驱动 FPGA 识别 CS 信号。发送其他指令也遵循这个规则。

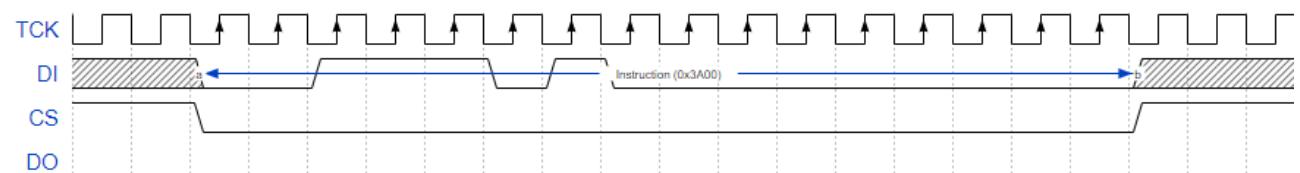

### Write Disable (0x3A00)

发送数据完成后，需使用 Write Disable 从编辑模式中退出。退出后可唤醒设备，使设备进入工作状态。

图 5-20 Write Disable (0x3A00) 时序示意图

像上述两个指令，0x1500 和 0x3A00 指令的时序基本一致，指令都是在 CS 低电平后开始，并在指令传输完成后拉高 CS，遵循这种时序的指令有 0x3C00 (Reconfig/Reprogram)、0x1500 (Write Enable)、0x3A000 (Write Disable)、0x1600 (Program SPI Flash)、0x1200 (Init Address)、0x0500 (Erase SRAM)。

另外，需要注意的是，因为 SSPI 是由外部时钟驱动，这些指令前后 CS 处于高电平时，需要 2 个以上的时钟以使 FPGA 可以采集到 CS 状态。

### Erase SRAM(0x0500)

指令时序与 WriteEnable/WriteDisable 一致，仅替换指令内容为 0x0500。

当指令发送后，需延迟至少 10ms 以使指令执行完毕。

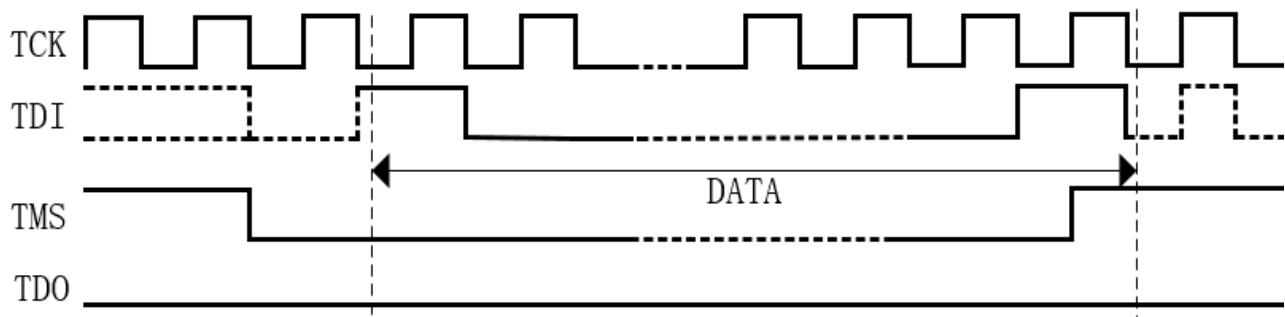

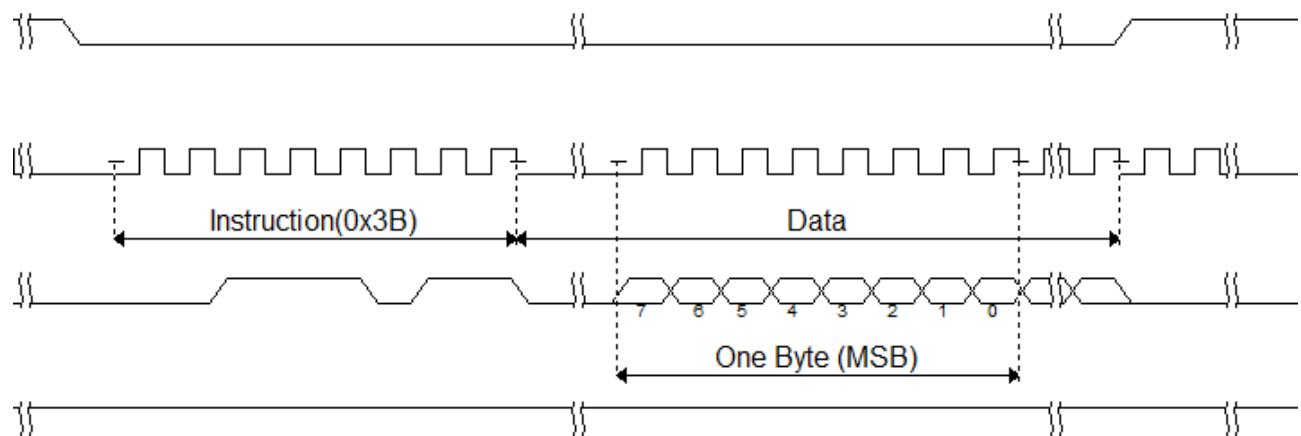

### Write Data (0x3B)

通过使用 WriteData (0x3B) 指令直接向 FPGA 设备发送数据流文件。

注意，在数据写入过程中，CS 一直处于低电平。

图 5-21 Write Data (0x3B) 时序示意图

#### 5.4.4 SSPI Configure SRAM 流程图

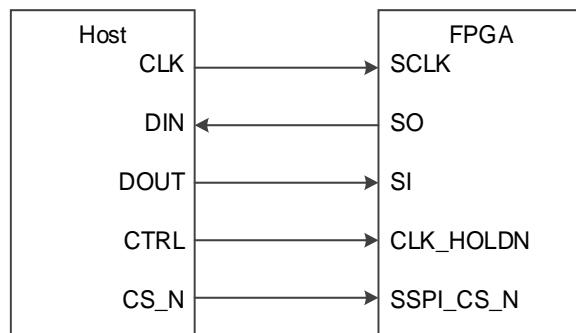

## 5.4.5 SSPI 配置模式连接示意图

使用 SSPI 配置模式对高云半导体 FPGA 产品配置的连接示意图如图 5-22 所示。

图 5-22 SSPI 配置模式连接示意图

注!

- 此图为 SSPI 配置模式的最小系统图，其他固定管脚的接法请参考图 5-1。

- `CLKHOLD_N` 默认状态为内部弱下拉，使用 SSPI 时请配置 `CLKHOLD_N` 为高电平。

SSPI 配置管脚除了进行常规的 SRAM 配置操作外，还可编程 FPGA 外部的 SPI Flash，编程 Flash 操作的 MODE 值与 SSPI 配置模式的 MODE 值相同，用户可以在 Gowin 编程软件中选择将配置数据写入 SRAM 或外部 Flash。需要从外部 Flash 加载前，需要将 MODE 值调整为 MSPI MODE，之后通过重新上电或触发 RECONFIG\_N 触发 MSPI 加载。

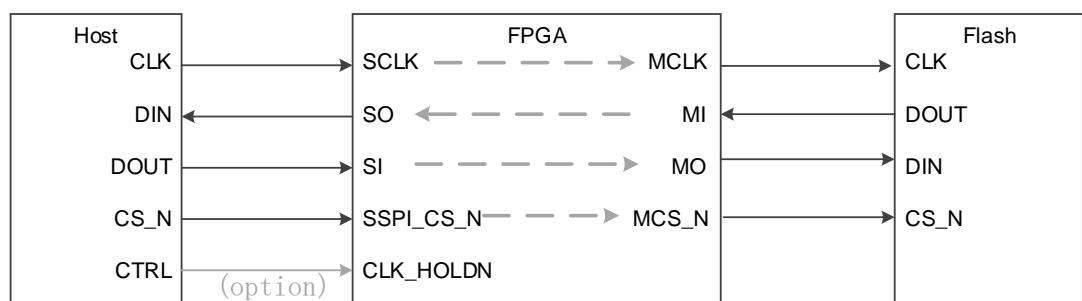

SSPI 接口编程外部 Flash 的连接示意图如图 5-23 所示。

图 5-23 SSPI 编程外部 Flash 连接示意图

烧录流程示意图见图 5-24。首先通过 SSPI 向 FPGA 发送指令“Program SPI Flash”(0x1600) 指令，完成后 FPGA 可以转发 SSPI 到 Flash，Host 端的 SSPI 可以直接访问 Flash，接下来就可以按照 Flash 的相关时序对其进行编程。

注意，从 Flash 读取数据时，回读的数据会延迟一个 Bit。例如 `sspi` 读取 Flash 的 IDCode 时，需要额外发送一个时钟从而获取最后一位。

**图 5-24 SSPI 配置 Flash 流程图**

#### 5.4.6 SSPI 模式下的多 FPGA 连线示意图

**图 5-25 多 FPGA 连线示意图 1**

图 5-26 多 FPGA 连线示意图 2

## 5.5 QSSPI 配置模式

高云内置 Flash 已经默认打开了 Flash 的 Quad Enable Bit(QE) , 可以直接使用 Quad Slave SPI(QSSPI)。QSSPI 模式相关的配置管脚如下表 5-12 所示。

表 5-12 QSSPI 配置模式管脚

| 管脚名称                        | I/O 类型     | 说明                                           |

|-----------------------------|------------|----------------------------------------------|

| RECONFIG_N                  | I, 内部弱上拉   | 低电平脉冲：启动 GowinCONFIG 配置                      |

| READY                       | I/O, 内部弱上拉 | 高电平：当前可以对 FPGA 进行编程配置<br>低电平：禁止对 FPGA 进行编程配置 |

| DONE                        | I/O, 内部弱上拉 | 高电平：成功完成编程配置<br>低电平：未完成编程配置或编程配置失败           |

| MODE[1:0]                   | I, 内部弱下拉   | 配置模式选择，READY 上升沿采样                           |

| SCLK                        | I, 内部弱上拉   | 输入时钟                                         |

| IO <sub>3</sub> (CLKHOLD_N) | I, 内部弱下拉   | 作为 Qaud SPI 的 IO <sub>3</sub>                |

| IO <sub>2</sub> (QSSPI_WPN) | I, 内部弱下拉   | 作为 Qaud SPI 的 IO <sub>2</sub>                |

| IO <sub>1</sub> (SO)        | O, 内部弱下拉   | 作为 Qaud SPI 的 IO <sub>1</sub>                |

| IO <sub>0</sub> (SI)        | I, 内部弱下拉   | 作为 Qaud SPI 的 IO <sub>0</sub>                |

| SSPI_CS_N                   | I, 内部弱上拉   | QSSPI 片选信号，低电平有效                             |

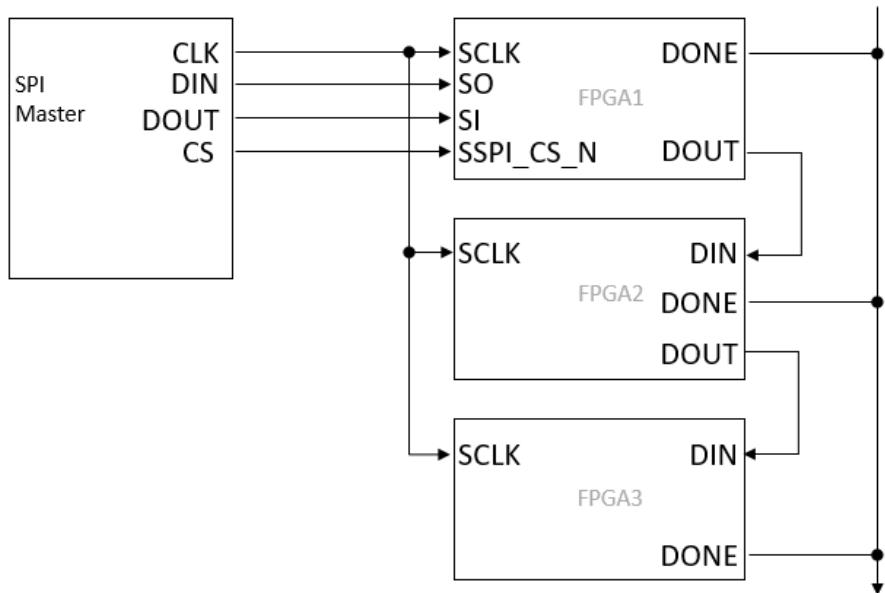

QSSPI 模式下配置 SRAM 流程如下所述，其中 Read Status、Reinit、EraseSram、InitAddress、WriteEnable、WriteDisable 依旧使用 SSPI 指令，只有 Write Data 时采用 QSSPI。

QSSPI Write Data (0x6B) 时序图如图 5-27 所示。

图 5-27 QSSPI Write Data (0x6B) 时序图

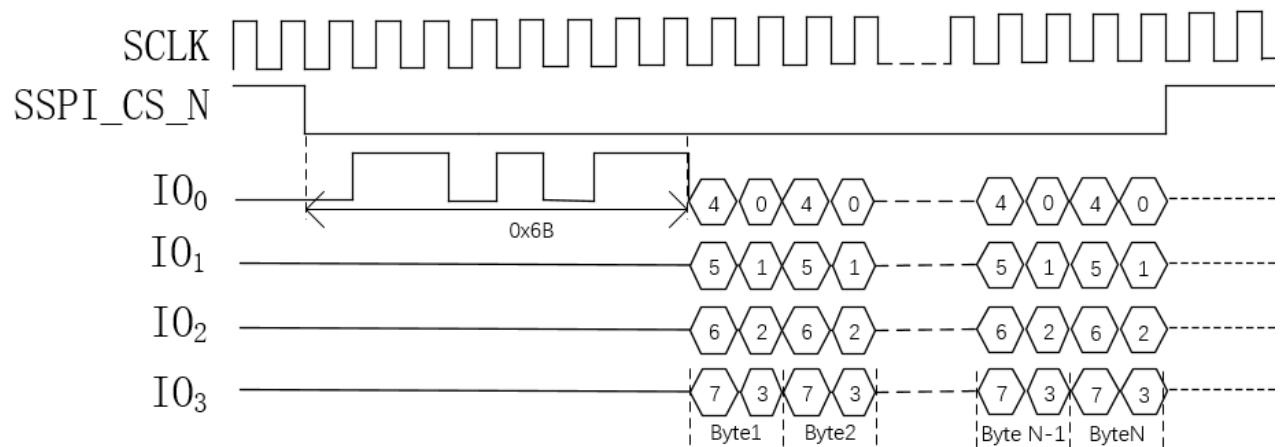

QSSPI 配置 SRAM 流程图如图 5-28 所示。

图 5-28 QSSPI 配置 SRAM 流程图

QSSPI 模式下编程 Flash 流程如下所述：

1. Standard SPI 发送 0x1B 指令（`sspi_prgm_qspi`），该阶段的 QSSPI\_WPN 和 CLKHOLD\_N 两个管脚要保持为 1。

2. QSPI 开始编程 Flash（编程 Flash 时指令 `write enable(0x04)` 和 `write disable(0x06)` 使用 Standard SPI 发送，写数据时使用 QSPI）。

3. 编程结束后 Standard SPI 需要发送 15 个 0x00 指令。

4. 如果需要回读 Flash，则需要使用 Standard SPI 回读 Flash，QSSPI 不

支持四线回读 Flash。

5. Standard SPI 发送 Reboot(0x3C)指令或触发 RECONFIG\_N 管脚, 然后 FPGA 自动加载 bitstream 文件。

QSPI 编程 Flash 流程图如下:

图 5-29 QSSPI 编程 Flash 流程图

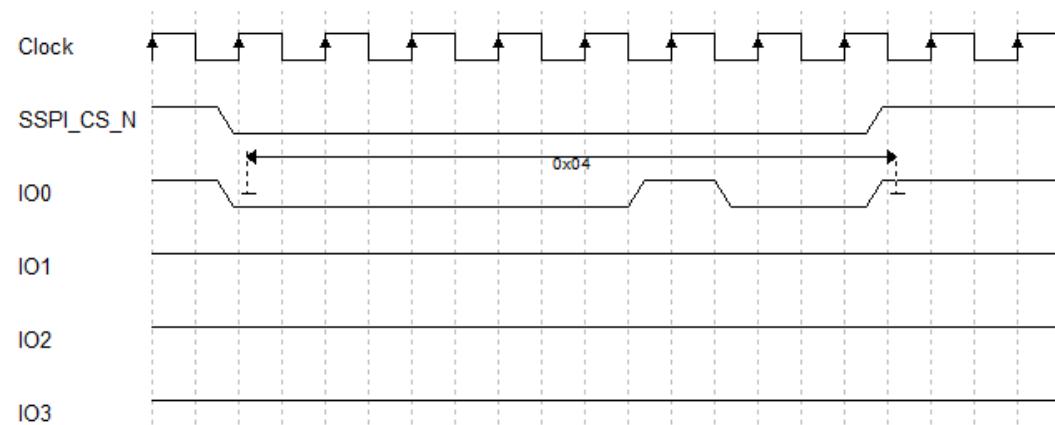

QSSPI write instruction (如 0x04) 时序如下图所示。

**图 5-30 QSSPI write instruction 时序图**

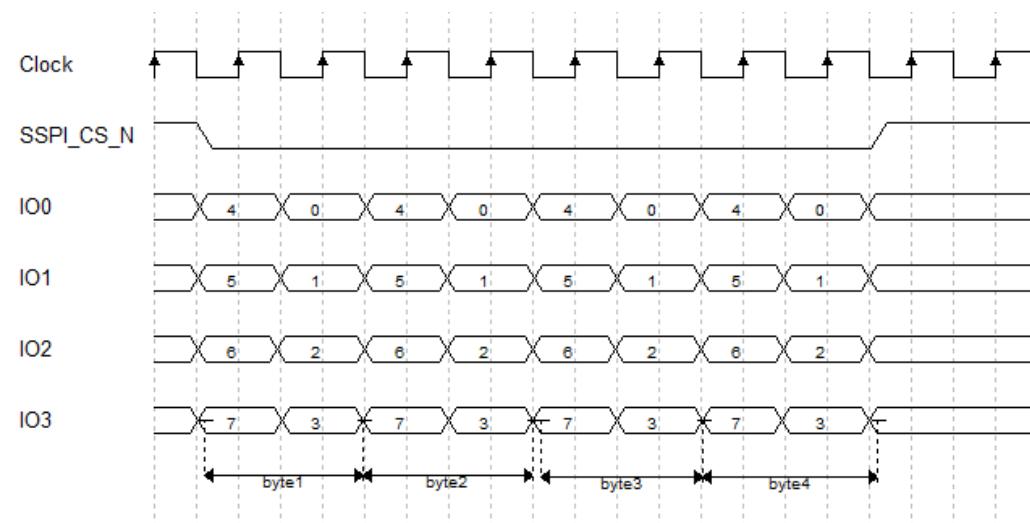

QSSPI write data 时序如下图所示：

**图 5-31 QSSPI write data 时序图**

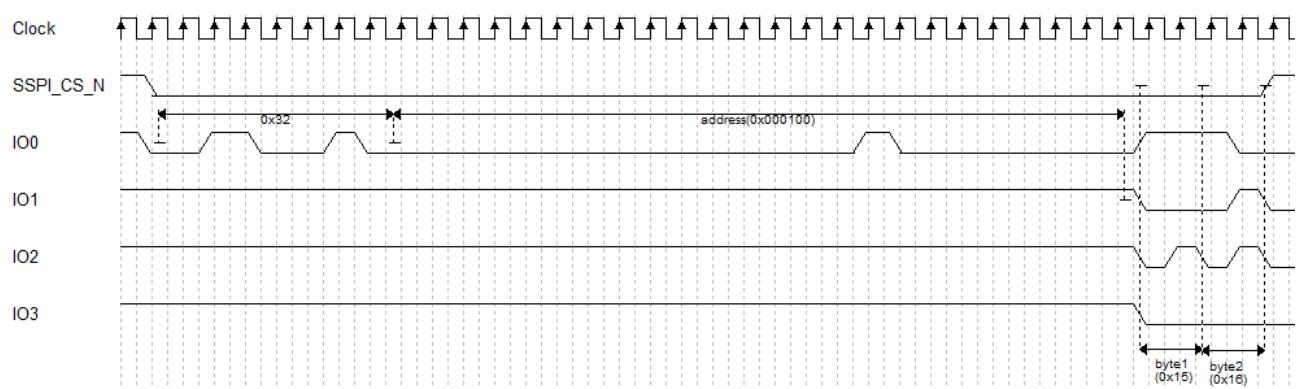

QSSPI page program 时序如下图所示：

**图 5-32 QSSPI page program 时序图**

**注！**

时序图表示从地址 0x000100 开始写 2Byte 数据 0x15 0x16。

## 5.6

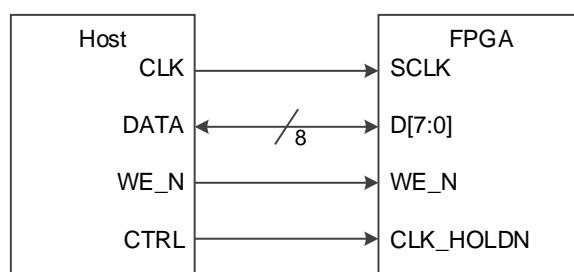

## 5.6 CPU 配置模式

CPU 配置模式下，Host 通过 8-bit 位宽的数据总线接口对高云半导体 FPGA 产品进行配置，CPU 配置模式的管脚如表 5-13 所示。

**表 5-13 CPU 配置模式管脚**

| 管脚名称       | I/O 类型     | 说明                                                |

|------------|------------|---------------------------------------------------|

| RECONFIG_N | I, 内部弱上拉   | 低电平脉冲：启动 GowinCONFIG 配置                           |

| READY      | I/O, 内部弱上拉 | 高电平：当前可以对器件进行编程配置<br>低电平：禁止对器件进行编程配置              |

| DONE       | I/O, 内部弱上拉 | 高电平：成功完成编程配置<br>低电平：未完成编程配置或编程配置失败                |

| MODE[1:0]  | I, 内部弱下拉   | 配置模式选择信号，READY 上升沿采样                              |

| SCLK       | I, 内部弱上拉   | 输入时钟                                              |

| CLKHOLD_N  | I, 内部弱下拉   | CPU 模式下的片选信号，低电平有效。即，若要在 CPU 模式下配置 FPGA，此信号需为低电平。 |

| WE_N       | I, 内部弱下拉   | 读写使能<br>0：写<br>1：读                                |

| D[7:0]     | I/O        | 数据输入输出端口：CPU 配置模式时作为输入管脚，配置结束后可以转换为输出管脚进行验证       |

CPU 配置模式的连接示意图如图 5-33 所示。

**图 5-33 CPU 配置模式连接示意图**

注！

此图为 CPU 配置模式的最小系统图，MODE 值设置为“111”，其他固定管脚的接法请参考图 5-1。

除满足上电要求外，使用 CPU 模式对高云半导体 FPGA 产品进行配置，还需满足以下条件：

- CPU 接口使能

上电后初次配置或前一次配置时 RECONFIG\_N 未设置为普通 I/O 状态。

- 启动新的配置

重新上电或者低电平脉冲触发 RECONFIG\_N 管脚。

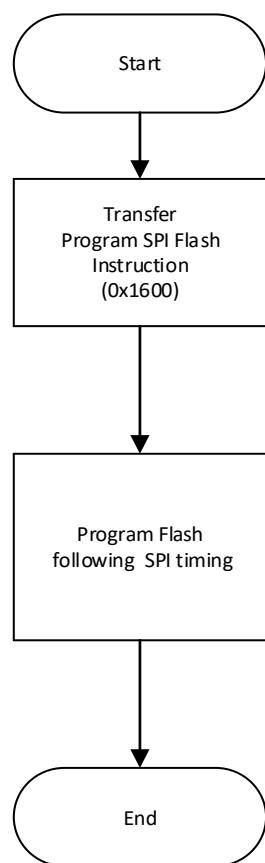

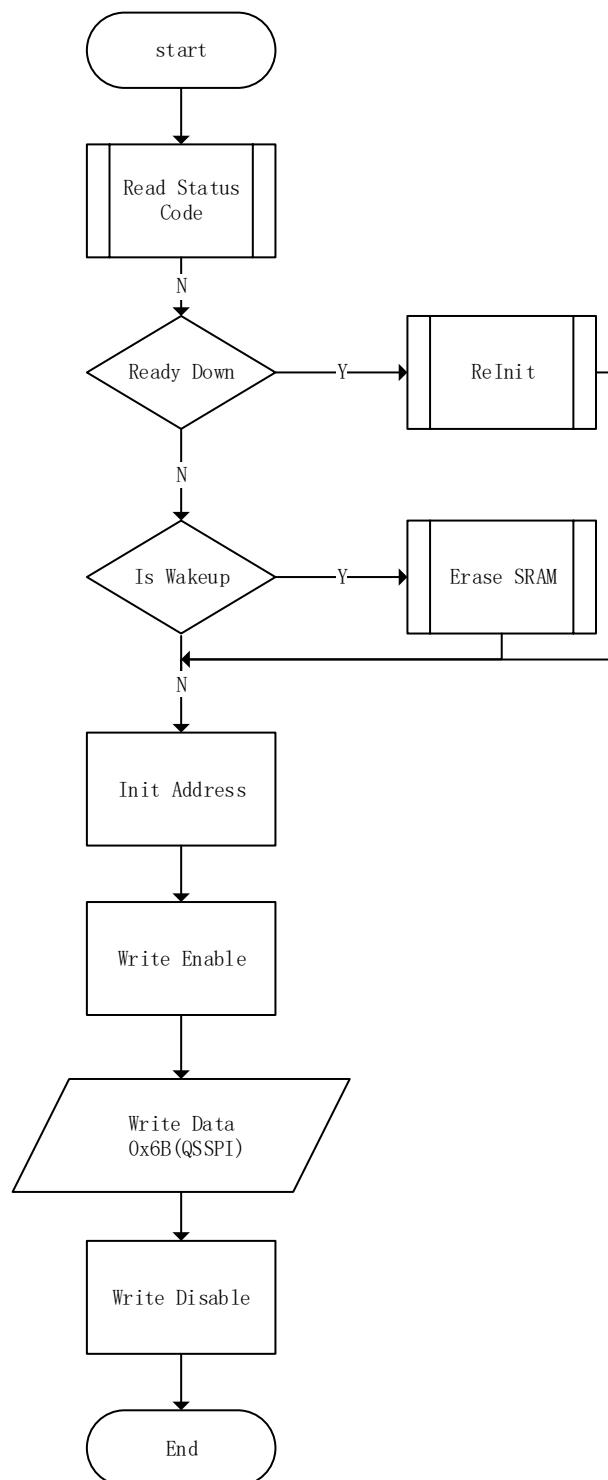

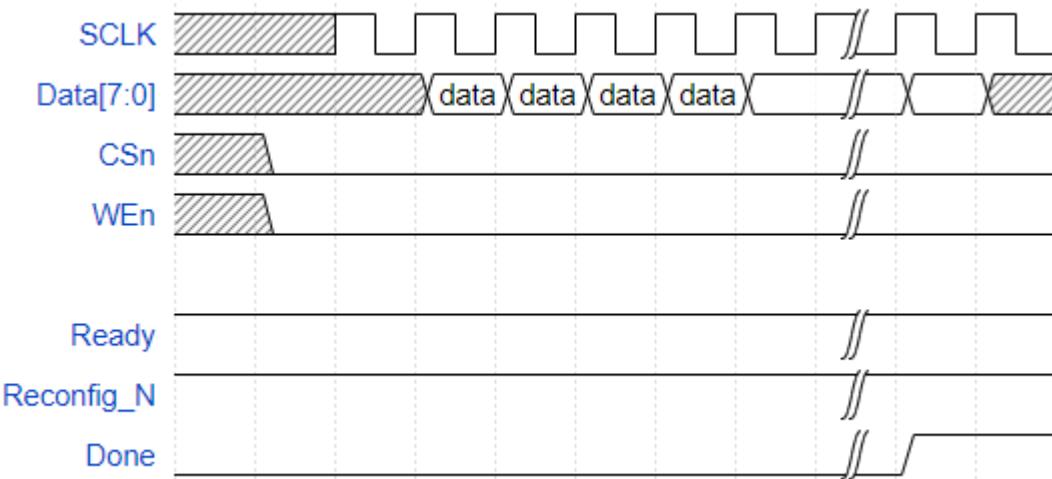

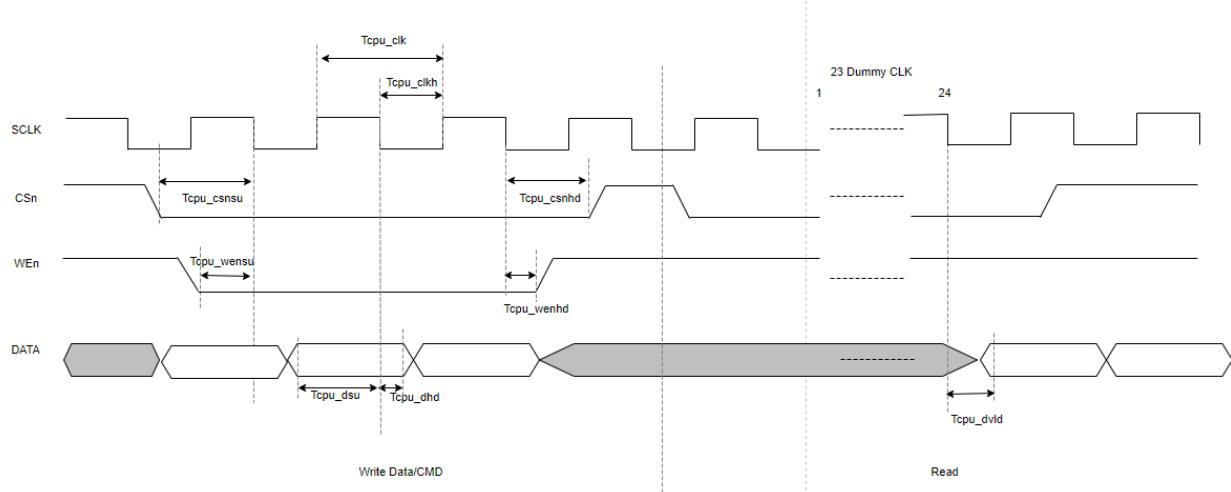

## 5.6.1 配置时序

在配置之前确保 MODE[1:0]=11，在配置完成后 DONE 会拉高。如果 DONE 或者 READY 被拉低，说明配置未成功。

配置过程中，数据总线 D[7:0]按大端模式（MSB）表示，FPGA 在 SCLK 下降沿读取数据。

图 5-34 CPU 模式配置流程示意图

图 5-35 CPU 配置模式时序图

**表 5-14 CPU 配置模式时序参数**

| 名称                     | 描述                                           | 最小值                   | 最大值                   | 单位 |

|------------------------|----------------------------------------------|-----------------------|-----------------------|----|

| T <sub>cpu_clk</sub>   | CPU input clock period                       | 40                    | —                     | ns |

| T <sub>cpu_csnSu</sub> | CLKHOLD_N(CSn) setup time to SCLK falling    | 8                     | —                     | ns |

| T <sub>cpu_csnhd</sub> | CLKHOLD_N(CSn) hold time from SCLK falling   | 0                     | —                     | ns |

| T <sub>cpu_wensu</sub> | WE_N setup time to SCLK falling              | 8                     | —                     | ns |

| T <sub>cpu_wenhd</sub> | WE_N hold time from SCLK falling             | 0                     | —                     | ns |

| T <sub>cpu_dsu</sub>   | Write data input setup time to SCLK falling  | 10                    | —                     | ns |

| T <sub>cpu_dhd</sub>   | Write data input hold time from SCLK falling | 0                     | —                     | ns |

| T <sub>cpu_dvld</sub>  | SCLK falling to read data output valid       | —                     | 10                    | ns |

| T <sub>cpu_clkh</sub>  | CPU input clock high duration                | (clock cycle)<br>*45% | (clock cycle)<br>*55% | —  |

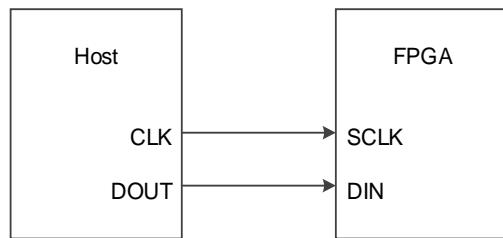

## 5.7 SERIAL 配置模式

SERIAL 配置模式, Host 通过串行接口对高云半导体 FPGA 产品进行配置。SERIAL 配置模式是使用管脚数量最少的配置模式之一。SERIAL 配置模式只能将比特流数据写入 FPGA, 无法从 FPGA 器件回读数据, 因此, SERIAL 配置模式无法读取 ID CODE 和 USER CODE 以及状态寄存器信息。SERIAL 配置模式的管脚定义如表 5-15 所示。

**表 5-15 SERIAL 配置模式管脚定义**

| 管脚名称       | I/O 类型     | 说明                                     |

|------------|------------|----------------------------------------|

| RECONFIG_N | I, 内部弱上拉   | 低电平脉冲: 启动 GowinCONFIG 配置               |

| READY      | I/O, 内部弱上拉 | 高电平: 当前可以对器件进行编程配置<br>低电平: 禁止对器件进行编程配置 |

| DONE       | I/O, 内部弱上拉 | 高电平: 成功完成编程配置<br>低电平: 未完成编程配置或编程配置失败   |

| MODE[1:0]  | I, 内部弱下拉   | 配置模式选择信号, READY 上升沿采样                  |

| SCLK       | I, 内部弱上拉   | 输入时钟                                   |

| DIN        | I, 内部弱下拉   | 输入数据                                   |

| DOUT       | O, 内部弱下拉   | 输出数据, 只用于 FPGA 级联时 SERIAL 配置模式         |

SERIAL 配置模式的连接示意图如图 5-36 所示。

图 5-36 SERIAL 配置模式连接示意图

注！

此图为 SERIAL 配置模式的最小系统图，MODE 值为“10”，其他固定管脚的接法请参考图 5-1。

### SERIAL 配置模式时序图

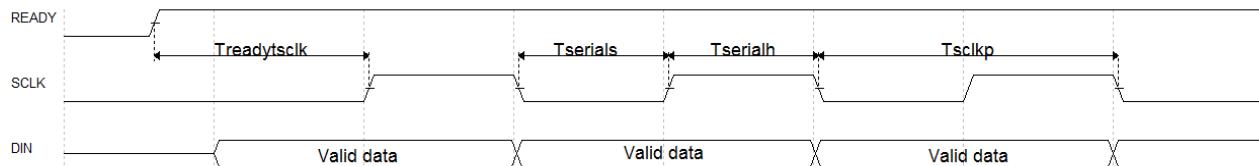

SERIAL 配置模式时序如图 5-37 所示。

图 5-37 SERIAL 配置模式时序图

表 5-16 SERIAL 配置模式时序参数

| 参数名称        | 参数含义                                                                   | 最小值  | 最大值 |

|-------------|------------------------------------------------------------------------|------|-----|

| Tsclkp      | SCLK 时钟周期(SCLK clock period)                                           | 15ns | -   |

| Tserials    | SERIAL PORT 建立时间(SERIAL PORT setup time)                               | 2ns  | -   |

| Tserialh    | SERIAL PORT 保持时间(SERIAL PORT hold time)                                | 0ns  | -   |

| Treadytsclk | READY 上升沿到第一个 SCLK 沿时间(Time from READY rising edge to first SCLK edge) | TBD  | -   |

除满足上电要求外，使用 SERIAL 模式对高云半导体 FPGA 产品进行配置，还需满足以下条件：

- SERIAL 接口使能

上电后初次配置或前一次配置时 RECONFIG\_N 未设置为普通 I/O 状态。

- 启动新的配置

重新上电或者低电平脉冲触发 RECONFIG\_N 管脚。

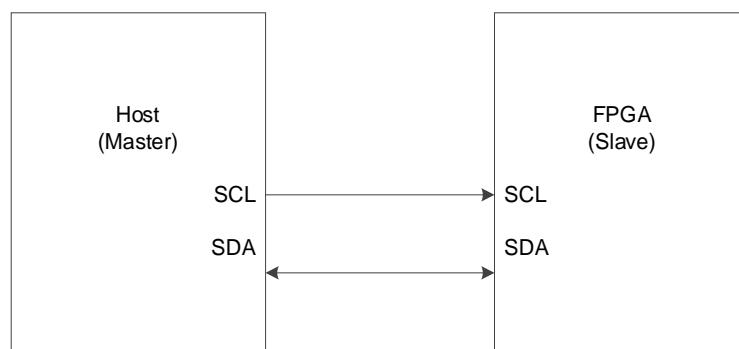

## 5.8 I<sup>2</sup>C 配置模式

I<sup>2</sup>C 配置模式，Host 通过 I<sup>2</sup>C 接口对高云半导体 FPGA 产品进行配置。I<sup>2</sup>C 配置模式是使用管脚数量最少的配置模式之一。I<sup>2</sup>C 配置模式只能将比特流数据写入 FPGA，无法从 FPGA 器件回读数据，因此，I<sup>2</sup>C 配置模式无法读取 ID CODE、USER CODE、状态寄存器和回读校验。I<sup>2</sup>C 配置模式的管脚定义如表 5-17 所示。

**表 5-17 I<sup>2</sup>C 配置模式管脚定义**

| 管脚名称       | I/O 类型     | 说明                                                       |

|------------|------------|----------------------------------------------------------|

| RECONFIG_N | I, 内部弱上拉   | 低电平脉冲：启动 GowinCONFIG 配置。                                 |

| READY      | I/O, 内部弱上拉 | 高电平：当前可以对器件进行编程配置。<br>低电平：禁止对器件进行编程配置。                   |

| DONE       | I/O, 内部弱上拉 | 高电平：成功完成编程配置。<br>低电平：未完成编程配置或编程配置失败。                     |

| MODE[1:0]  | I, 内部弱下拉   | 配置模式选择信号，READY 上升沿采样。                                    |

| SCL        | I, 内部弱下拉   | 输入时钟。                                                    |

| SDA        | I/O, 内部弱下拉 | 输入数据，或输出 ACK。<br>当配置模式支持 I <sup>2</sup> C 时，SDA 管脚需要外上拉。 |

I<sup>2</sup>C 配置模式的连接示意图如图 5-38 所示。

**图 5-38 I<sup>2</sup>C 配置模式连接示意图**

注！

- 此图为 I<sup>2</sup>C 配置模式的最小系统图，其他固定管脚的接法请参考图 5-1。

- GW2AN-18X/9X 不支持标准 I<sup>2</sup>C 总线，仅支持 I<sup>2</sup>C 协议下单一设备配置。

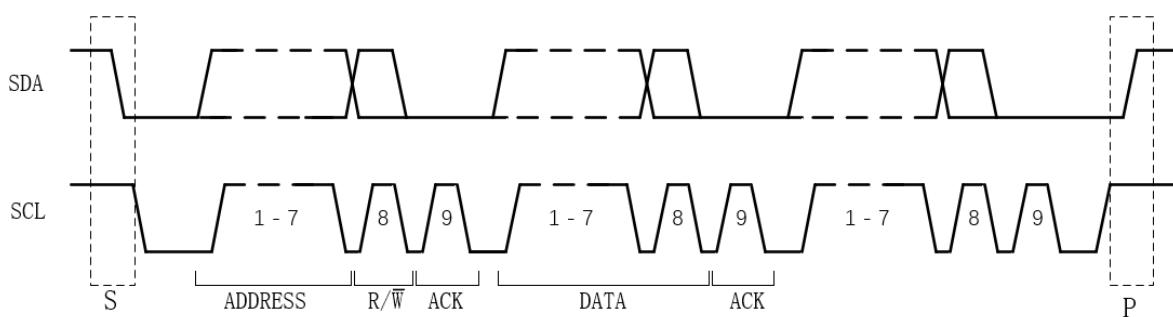

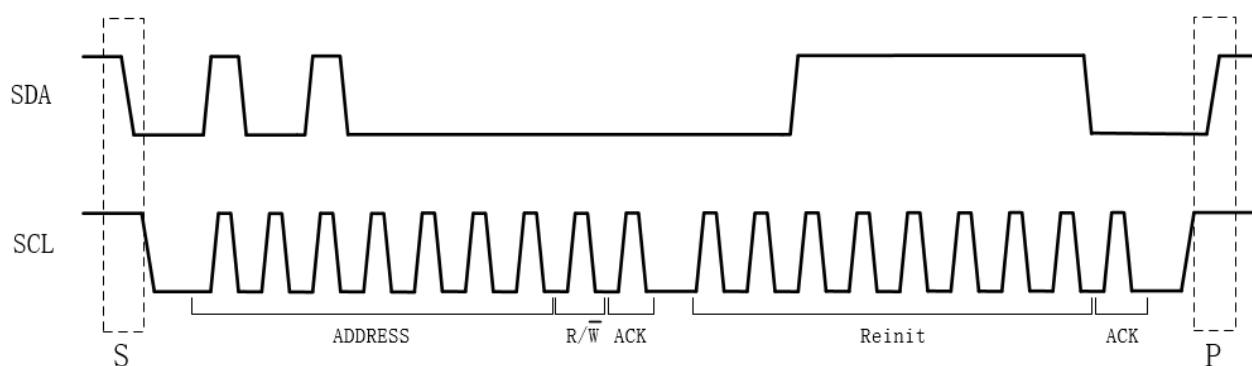

图 5-39 I<sup>2</sup>C 配置模式时序图

I<sup>2</sup>C 是串行传输总线，按照上图所示协议进行数据传输，正常状态下，SDA 和 SCL 都处于高电平。

表 5-18 I<sup>2</sup>C 配置模式时序参数

| 参数      | 参数含义       |                                            |

|---------|------------|--------------------------------------------|

| S       | 启动条件       | SCL 是高电平时，SDA 从高电平向低电平切换。                  |

| P       | 停止条件       | SCL 是高电平时，SDA 由低电平向高电平跳变。                  |

| ADDRESS | 地址帧        | 每个从属设备唯一的 7 位或 10 位序列，用于在主设备要与之通信时标识该从属设备。 |

| R/W     | 读/写位       | 指定主设备是向从设备发送数据（0）还是向从机读取数据（1）。             |

| ACK     | ACK/NACK 位 | 消息中的每个帧后均带有一个 ACK/NACK 位，高云 FPGA 正确时返回 0。  |

| DATA    | 数据         | 一个数据有 8bits，并以最高有效位优先发送。                   |

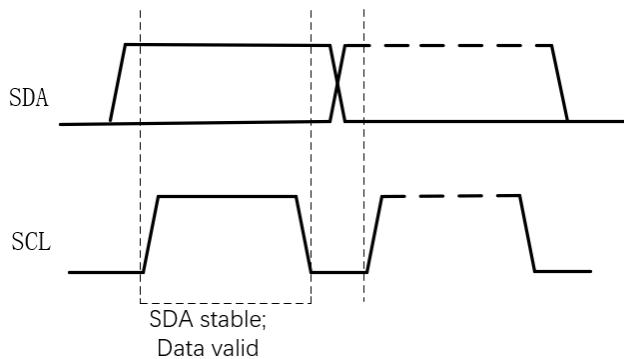

I<sup>2</sup>C 总线上的所有 DATA 都是以 8 位字节传送的，发送器每发送一个字节，就在时钟脉冲 9 期间释放数据线，由接收器反馈一个应答信号。应答信号为低电平时，规定为有效应答位（ACK 位），表示接收器已经成功地接收了该字节；应答信号为高电平时，规定为非应答位（NACK），一般表示接收器接收该字节没有成功，对于反馈有效应答位 ACK 的要求是，接收器在第 9 个时钟脉冲之前的低电平期间将 SDA 线拉低，并且确保在该时钟的高电平期间为稳定的低电平。如果接收器是主控器，则在它收到最后一个字节后，发送一个 NACK 信号，以通知被控发送器结束数据发送，并释放 SDA 线，以便主控接收器发送一个停止信号。在 I<sup>2</sup>C 总线上传送的每一位数据都有一个时钟脉冲相对应（或同步控制），即在 SCL 串行时钟的配合下，在 SDA 上逐位地串行传送每一位数据。进行数据传送时，在 SCL 呈现高电平期间，SDA 上的电平必须保持稳定，低电平为数据 0，高电平为数据 1。只有在 SCL 为低电平期间，才允许 SDA 上的电平改变状态。逻辑 0 的电平为低电压，而逻辑 1 则为高电平，如下图所示。

高云器件支持的 I<sup>2</sup>C 配置模式信息如表 5-19 所示。

**表 5-19 I<sup>2</sup>C 配置模式频率及地址**

| 模式                              | 器件              | 频率          | 地址                                |

|---------------------------------|-----------------|-------------|-----------------------------------|

| SRAM<br>内置 Flash <sup>[2]</sup> | GW2AN-18X/9X 系列 | 100KHz~555K | 7'b1010 <u>000</u> <sup>[1]</sup> |

注!

- [1] I<sup>2</sup>C 的 slave 地址支持 2bit 配置，默认地址为 7'b1010000，下划线位置为可修改为 1，但不能回改为 0。

- [2] I<sup>2</sup>C 操作 Flash，需要先将数据流文件转换成特定数据码流，该转换工具包含在 Programer 中，转换后的文件名后缀以".i2c"表示。“.i2c”是一个二进制文件。

除满足上电要求外，使用 I<sup>2</sup>C 模式对高云半导体 FPGA 产品进行配置，还需满足以下条件：

- I<sup>2</sup>C 接口使能

上电后初次配置或前一次配置时 RECONFIG\_N 未设置为普通 I/O 状态。

- 启动新的配置

重新上电或者低电平脉冲触发 RECONFIG\_N 管脚。

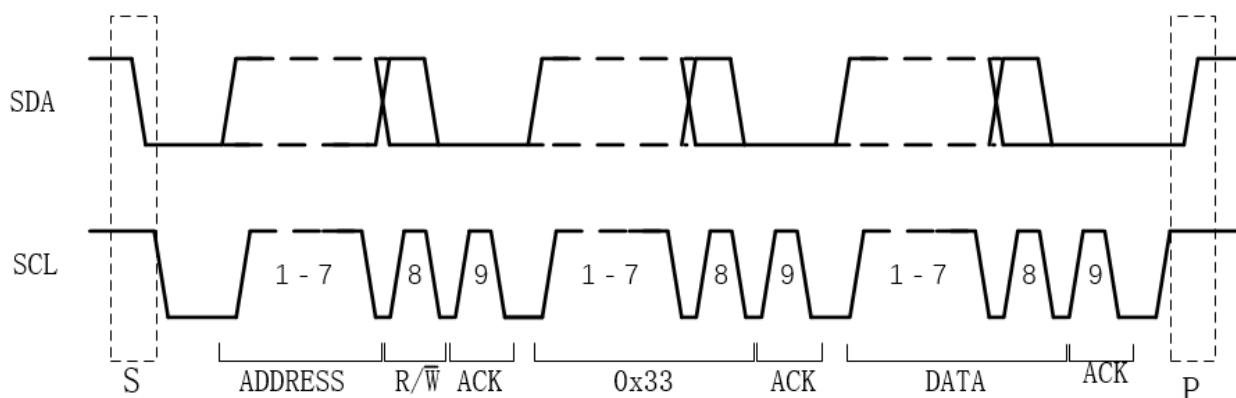

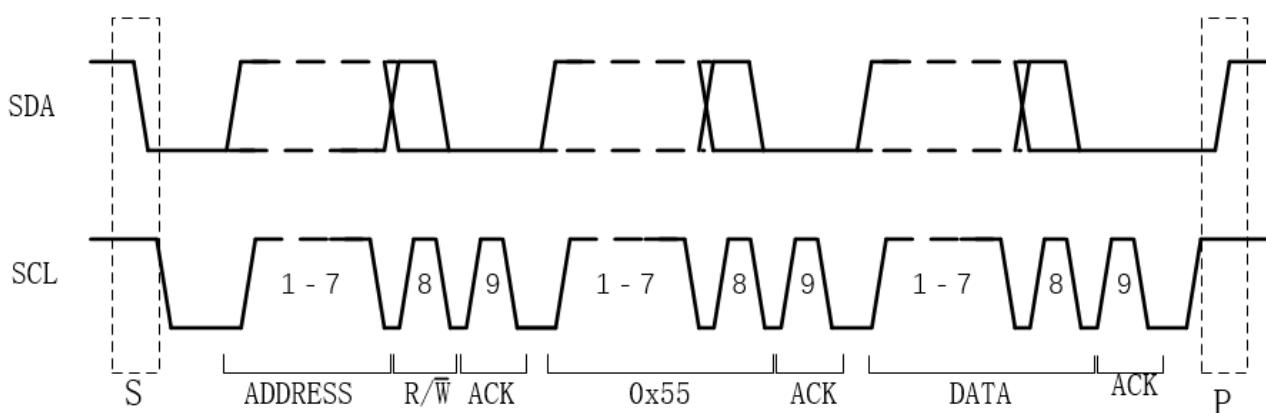

## 5.8.1 配置指令

I<sup>2</sup>C 配置模式使用了统一的地址，通过不同的指令指定配置 SRAM 或 Flash。以下是 I<sup>2</sup>C 指令一览表：

**表 5-20 I<sup>2</sup>C 配置指令**

| 名称              | 完整指令（指令字节+冗余信息字节） |

|-----------------|-------------------|

| Reinit          | 0x3f              |

| Config-SRAM     | 0x33              |

| Config-Flash    | 0x55              |

| Reboot/Reconfig | 0x3c              |

图 5-40 Reinit 时序图

图 5-41 配置 SRAM 时序图

图 5-42 配置 Flash 时序图

图 5-43 Reboot 时序图

## 5.8.2 I<sup>2</sup>C 配置 SRAM 流程

I<sup>2</sup>C 配置 SRAM 的流程如下：

1. 发送 start 信号和 7 位地址+写操作；

2. 发送数据 0x3f(reinit 指令)；

3. 发送 stop 信号；

4. 发送 start 信号和 7 位地址+写操作；

5. 发送数据 0x33(config\_sram)；

6. 发送数据流文件数据，按照 MSB 方式发送；

7. 数据流文件发送完成后发送 stop 信号。

图 5-44 I<sup>2</sup>C 配置 SRAM 的流程图

## 5.8.3 I<sup>2</sup>C 配置 Flash 流程

I<sup>2</sup>C 配置 Flash 的 data 形式如下：

|      |      |       |              |

|------|------|-------|--------------|

| CS   | SI   | ----- | SPI value    |

| bit7 | bit6 | ----- | SPI vector 1 |

| bit5 | bit4 | ----- | SPI vector 2 |

| bit3 | bit2 | ----- | SPI vector 3 |

| bit1 | bit0 | ----- | SPI vector 4 |

注！

I<sup>2</sup>C 解析得到 CS 的值同 Flash 需要的 CS 值相反！

### I<sup>2</sup>C 擦除 Flash 的流程：

1. 发送 start 信号和 7 位地址+写操作；

2. 发送数据 0x3f(reinit 指令)；

3. 发送 stop 信号；

4. 发送 start 信号和 7 位地址+写操作；

5. 发送数据 0x55(config\_flash);

6. 发送数据 0x00,拉高 CS 信号;

7. 发送数据 0xaa 0xbe(DI:06&CS:ff), Flash 写使能;

8. 发送数据 0x00,拉高 CS 信号;

9. 发送数据 0xfa 0xbf(DI:c7&CS:ff), Flash 整片擦除;

10. 发送数据 0x00,拉高 CS 信号;

11. 发送数据 0xaa 0xba(DI:04&CS:ff), Flash 写失能;

12. 发送数据 0x00,拉高 CS 信号;

13. 发送 stop 信号;

14. 延时 30s, 等待 flash 擦除完成。

**图 5-45 I2C 擦除 Flash 的流程图**

### I2C 写 Flash 的流程:

1. 发送 start 信号和 7 位地址+写操作;

2. 发送数据 0x3f(reinit 指令);

3. 发送 stop 信号;

4. 发送 start 信号和 7 位地址+写操作;

5. 发送数据 0x55(config\_flash);

6. 发送数据 0x00,拉高 CS 信号;

7. 发送数据 0xaa 0xbe(DI:06&CS:ff), Flash 写使能;

8. 发送数据 0x00,拉高 CS 信号;

9. 发送数据 0xaa 0xae(DI:02&CS:ff), pageprogram 指令;

10. 发送 24bit 地址(DI:xx&CS:ff);

11. 发送数据流文件数据(DI:xx&CS:ff);

12. delay 20 ms;

13. 发送数据 0xaa 0xba(DI:04&CS:ff), Flash 写失能;

14. 发送数据 0x00, 拉高 CS 信号;

15. 发送 stop 信号;

16. 循环步骤 5-15, 直到数据流文件写完;

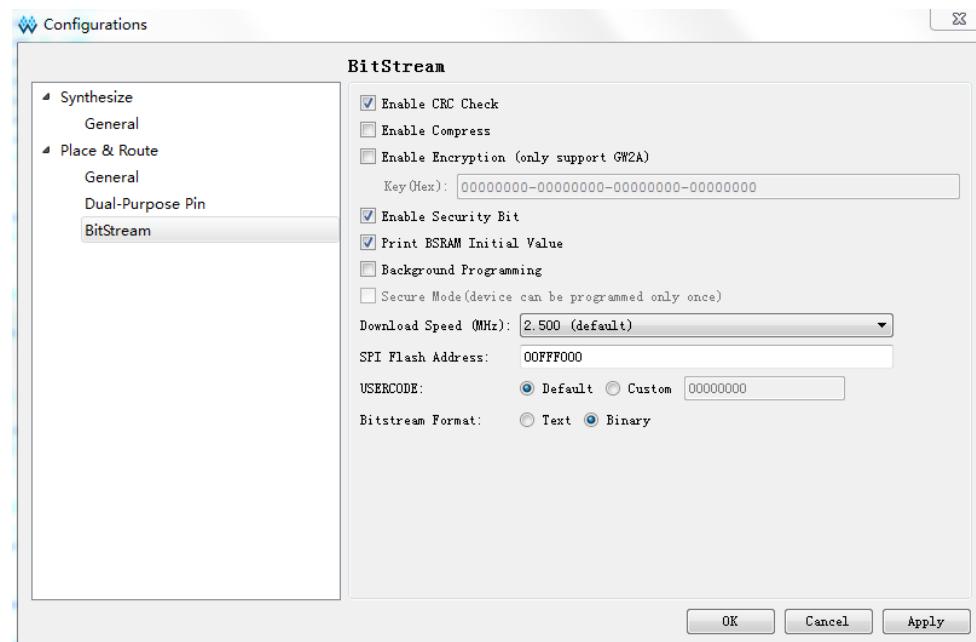

17. 发送 start 信号和 7 位地址+写操作;