# Gowin Serial RapidIO IP 用户指南

IPUG1023-1.0,2023-08-18

#### 版权所有 © 2023 广东高云半导体科技股份有限公司

**GO**₩IN高云、₩、Gowin、GowinSynthesis、云源以及高云均为广东高云半导体科技股份有限公司注册商标,本手册中提到的其他任何商标,其所有权利属其拥有者所有。未经本公司书面许可,任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部,并不得以任何形式传播。

#### 免责声明

本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止发言或其它方式授予任何知识产权许可。除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。高云半导体不承诺对这些文档进行适时的更新。

## 版本信息

| 日期         | 版本  | 说明    |

|------------|-----|-------|

| 2023/08/18 | 1.0 | 初始版本。 |

i

## 目录

| 目 | 录                               | i    |

|---|---------------------------------|------|

| 冬 | 目录                              | . iv |

| 表 | 目录                              | V    |

| 1 | 关于本手册                           | 1    |

|   | 7.1 手册内容                        |      |

|   | 1.2 相关文档                        |      |

|   | 1.3 术语、缩略语                      |      |

|   | 1.4 技术支持与反馈                     |      |

| 2 | 功能简介                            |      |

| _ | 2.1 概述                          |      |

|   | 2.2 主要特性                        |      |

|   | 2.3 资源利用                        |      |

| 2 | 功能描述                            |      |

| 3 | 3.1 系统框图                        |      |

|   | 3.2 模块功能                        |      |

|   |                                 |      |

|   | 3.2.1 SerDes 模块                 |      |

|   | 3.2.2 LOG 模块                    |      |

|   | 3.2.3 BUF 模块                    |      |

|   | 3.2.4 PHY 模块                    |      |

|   | 3.2.5 Maintenance 模块            |      |

|   | 3.2.6 Srio_config 模块            |      |

|   | 3.3 用户接口                        |      |

|   | 3.4 端口列表                        |      |

|   | 3.5 用户接口时序                      |      |

|   | 3.5.1 I/O 事务接口时序图               |      |

|   | 3.5.2 配置接口时序图                   |      |

|   | 3.6 寄存器接口                       |      |

|   | 3.6.1 Device Identity CAR (0x0) | . 24 |

|   | 3.6.2 Device Information CAR (0x4)                           | 25 |

|---|--------------------------------------------------------------|----|

|   | 3.6.3 Assembly Identity CAR (0x8)                            | 25 |

|   | 3.6.4 Assembly Information CAR (0xc)                         | 25 |

|   | 3.6.5 Processing Element Features CAR(0x10)                  | 25 |

|   | 3.6.6 Switch Port Information CAR (0x14)                     | 26 |

|   | 3.6.7 Source Operations CAR (0x18)                           | 26 |

|   | 3.6.8 Destination Operations CAR (0x1c)                      | 27 |

|   | 3.6.9 Processing Element Logical Layer Control CSR (0x4c)    | 27 |

|   | 3.6.10 Local Configuration Space Base Address 0 CSR (0x58)   | 28 |

|   | 3.6.11 Local Configuration Space Base Address 1 CSR (0x5c)   | 28 |

|   | 3.6.12 Base Device ID CSR (0x60)                             | 28 |

|   | 3.6.13 Host Base Device ID Lock CSR(0x68)                    | 28 |

|   | 3.6.14 Component Tag CSR(0x6c)                               | 28 |

|   | 3.6.15 LP-Serial Register Block Header(0x100)                | 28 |

|   | 3.6.16 Port Link Timeout Control CSR(0x120)                  | 29 |

|   | 3.6.17 Port Response Timeout Control CSR (0x124)             | 29 |

|   | 3.6.18 Port General Control CSR(0x13c)                       | 29 |

|   | 3.6.19 Port n Link Maintenance Request CSR(0x140)            | 29 |

|   | 3.6.20 Port n Link Maintenance Response CSR(0x144)           | 29 |

|   | 3.6.21 Port n Local ackID CSR(0x148)                         | 29 |

|   | 3.6.22 Port n Control 2 CSR(0x154)                           | 30 |

|   | 3.6.23 Port n Error and Status CSR(0x158)                    | 30 |

|   | 3.6.24 Port n Control CSR(0x15c)                             | 31 |

|   | 3.6.25 LP-Serial Lane Command and Status Registers(0x400)    | 32 |

|   | 3.6.26 Lane n Status 0 CSRs(0x410/0x430/0x450/0x470)         | 32 |

|   | 3.6.27 Lane n Status 1 CSRs(0x414/0x434/0x454/0x474)         | 32 |

|   | 3.6.28 Watermarks CSR(0x10000)                               | 32 |

|   | 3.6.29 Buffer Control CSR (0x10004)                          | 33 |

|   | 3.6.30 Maintenance Request Information Register(0x10100)     | 33 |

|   | 3.6.31 Maintenance Request HopCount Register(0x10104)        | 33 |

|   | 3.6.32 Maintenance Response Time-out Scale Register(0x10108) | 33 |

| 4 | 界面配置                                                         | 35 |

| 5 | 参考设计                                                         | 42 |

|   | 5.1 应用                                                       |    |

|   | 5.2 Serial RapidIO IP 参考设计工程                                 |    |

|   | 5.3 参考设计板测一                                                  |    |

|   |                                                              |    |

|   | 5.4 参考设计板测二   | 47 |

|---|---------------|----|

| 6 | <b>3</b> 文件交付 | 49 |

|   | 6.1 文档        | 49 |

|   | 6.2 设计源代码(加密) | 49 |

|   | 6.3 参差设计      | 49 |

## 图目录

| 图 | 3-1 系统框图                         | 6  |

|---|----------------------------------|----|

| 图 | 3-2 SerDes 模块框图                  | 7  |

| 图 | 3-3 LOG 模块框图                     | 8  |

| 图 | 3-4 远端设备操作本地设备的维护操作流程图           | 10 |

| 图 | 3-5 本地设备操作远端设备的维护操作流程图           | 11 |

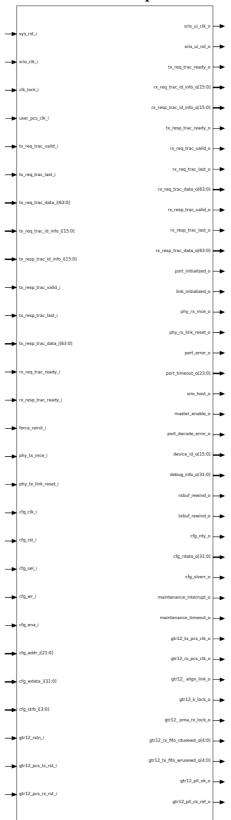

| 图 | 3-6 Gowin Serial RapidIO IP 端口图  | 13 |

| 图 | 3-7 I/O 事务接口时序图                  | 20 |

| 冬 | 3-8 Header 信息定义图                 | 21 |

| 冬 | 3-9 cfg 接口读时序图                   | 21 |

| 冬 | 3-10 cfg 接口写时序图                  | 22 |

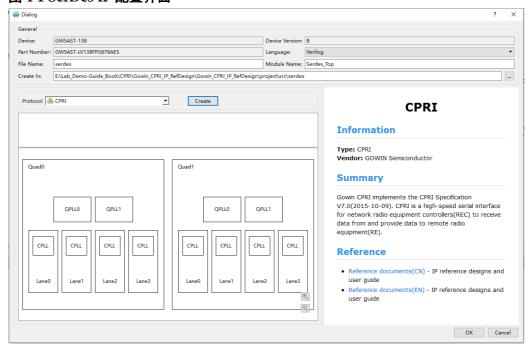

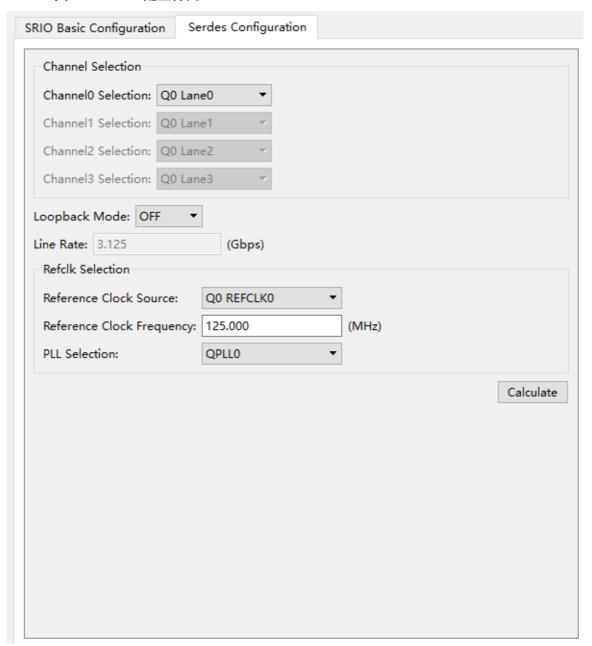

| 冬 | 4-1 SerDes IP 配置界面               | 35 |

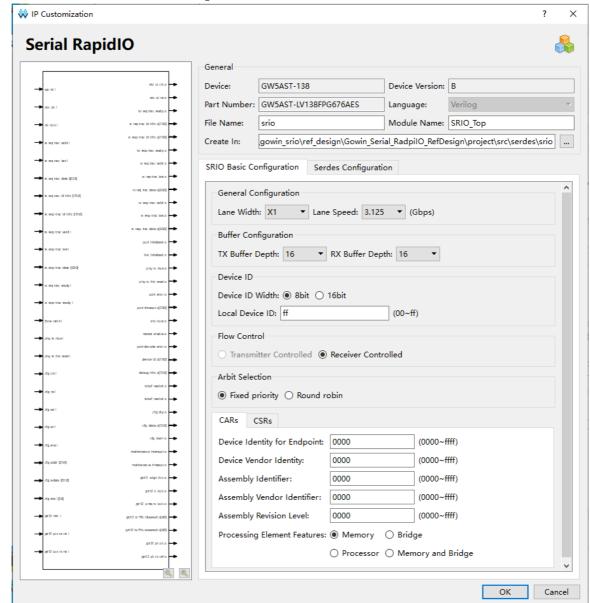

| 图 | 4-2 Gowin Serial RapidIO IP 配置界面 | 36 |

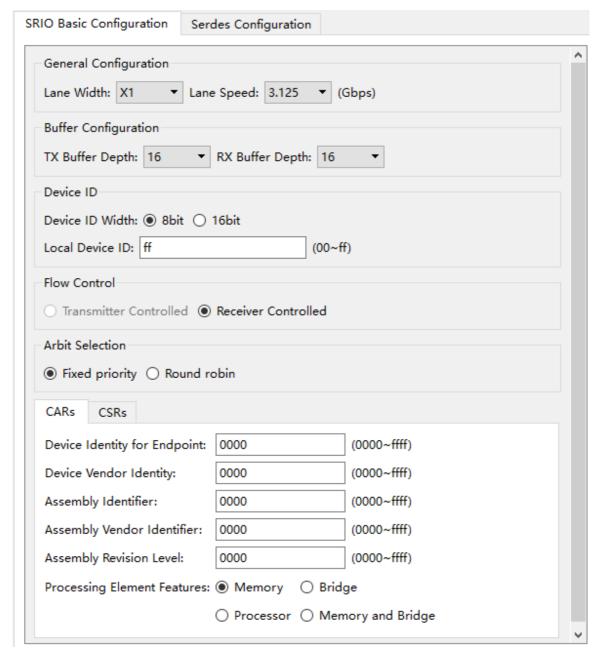

| 图 | 4-3 IP 协议配置界面 1                  | 37 |

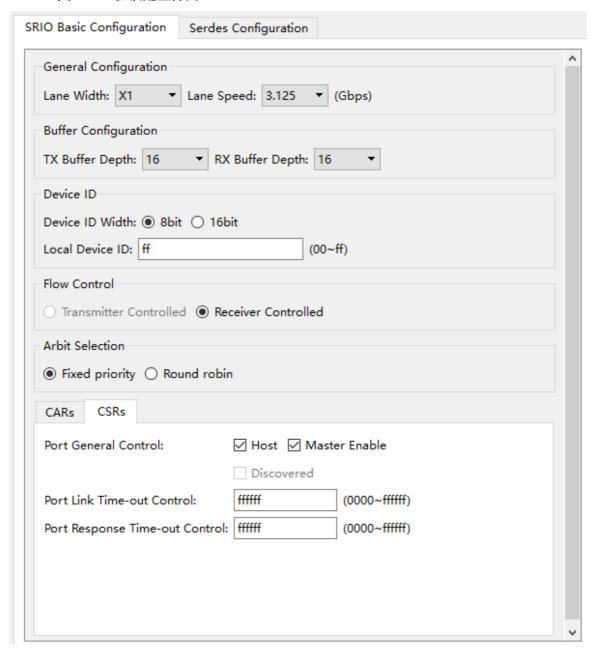

| 图 | 4-4 IP 协议配置界面 2                  | 38 |

| 图 | 4-5 SerDes 配置界面                  | 39 |

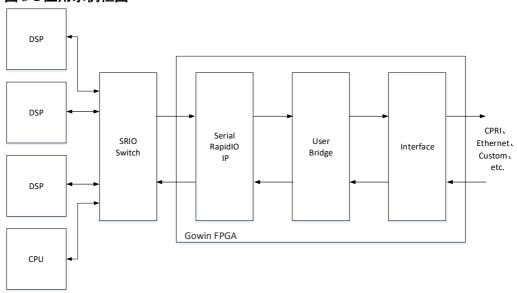

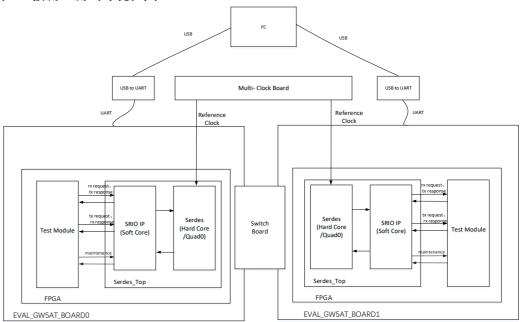

| 图 | 5-1 应用示例框图                       | 42 |

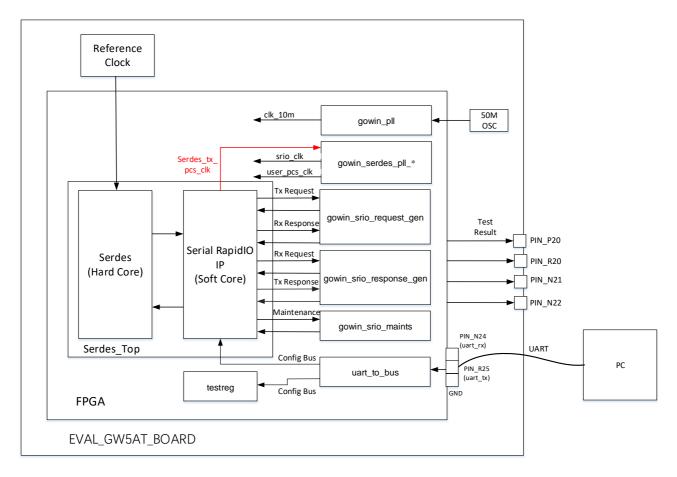

| 图 | 5-2 参考设计实例基本结构图                  | 44 |

| 图 | 5-3 板测一测试环境框图                    | 45 |

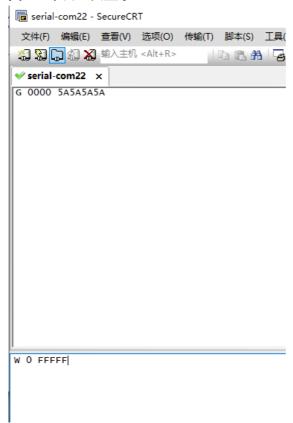

| 图 | 5-4 串口工具显示                       | 47 |

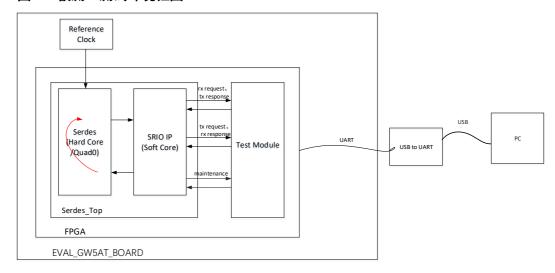

| 图 | 5-5 板测二测试环境框图                    | 48 |

| 图 | 5-6 Serial RapidIO IP 板测二 GUI 设置 | 48 |

## 表目录

| 表 1-1 术语、缩略语                                                  | 1  |

|---------------------------------------------------------------|----|

| 表 2-1 Gowin Serial RapidIO IP 概述                              | 4  |

| 表 2-2 Gowin Serial RapidIO IP 占用资源                            | 5  |

| 表 3-1 Gowin Serial RapidIO IP 端口列表                            | 14 |

| 表 3-2 寄存器地址空间                                                 | 22 |

| 表 3-3 本地设备寄存器列表概述                                             | 22 |

| 表 3-4 Device Identity CAR 各个 bit 含义                           | 24 |

| 表 3-5 Device Information CAR 各个 bit 含义                        | 25 |

| 表 3-6 Assembly Identity CAR 各个 bit 含义                         | 25 |

| 表 3-7 Assembly Information CAR 各个 bit 含义                      | 25 |

| 表 3-8 Processing Element Features CAR 各个 bit 含义               | 25 |

| 表 3-9 Switch Port Information CAR 各个 bit 含义                   | 26 |

| 表 3-10 Source Operations CAR 各个 bit 含义                        | 26 |

| 表 3-11 Destination Operations CAR 各个 bit 含义                   | 27 |

| 表 3-12 Processing Element Logical Layer Control CSR 各个 bit 含义 | 27 |

| 表 3-13 Local Configuration Space Base Address 0 CSR 各个 bit 含义 | 28 |

| 表 3-14 Local Configuration Space Base Address 1 CSR 各个 bit 含义 | 28 |

| 表 3-15 Base Device ID CSR 各个 bit 含义                           | 28 |

| 表 3-16 Host Base Device ID Lock CSR 各个 bit 含义                 | 28 |

| 表 3-17 Component Tag CSR 各个 bit 含义                            | 28 |

| 表 3-18 LP-Serial Register Block 各个 bit 含义                     | 28 |

| 表 3-19 Port Link Timeout Control CSR 各个 bit 含义                | 29 |

| 表 3-20 Port Response Timeout Control CSR 各个 bit 含义            | 29 |

| 表 3-21 Port General Control CSR 各个 bit 含义                     | 29 |

| 表 3-22 Port n Link Maintenance Request CSR 各个 bit 含义          | 29 |

| 表 3-23 Port n Link Maintenance Response CSR 各个 bit 含义         | 29 |

| 表 3-24 Port n Local ackID CSR 各个 bit 含义                       | 29 |

| 表 3-25 Port n Control 2 CSR 各个 bit 含义                         | 30 |

| 表 3-26 Port n Error and Status CSR 久介 hit 今♡                  | 30 |

| 表 3-27 Port n Control CSR 各个 bit 含义                           | 31 |

|---------------------------------------------------------------|----|

| 表 3-28 LP-Serial Lane Command and Status Registers 各个 bit 含义  | 32 |

| 表 3-29 Lane n Status 0 CSRs 各个 bit 含义                         | 32 |

| 表 3-30 Lane n Status 1 CSRs 各个 bit 含义                         | 32 |

| 表 3-31 Watermarks CSR 各个 bit 含义                               | 32 |

| 表 3-32 Buffer Control CSR 各个 bit 含义                           | 33 |

| 表 3-33 Maintenance Request Information Register 各个 bit 含义     | 33 |

| 表 3-34 Maintenance Request HopCount Register 各个 bit 含义        | 33 |

| 表 3-35 Maintenance Response Time-out Scale Register 各个 bit 含义 | 33 |

| 表 4-1 Serial RapidIO IP 配置界面参数                                | 39 |

| 表 5-1 testreg 寄存器列表                                           | 45 |

| 表 6-1 文档列表                                                    | 49 |

| 表 6-2 Gowin Serial RapidIO IP 设计源代码列表                         | 49 |

| 表 6-3 Gowin Serial RapidIO IP RefDesign 文件夹内容列表               | 49 |

IPUG1023-1.0 vi

1 关于本手册 1.1 手册内容

#

## 1.1 手册内容

Gowin Serial RapidIO IP 用户指南主要包括功能简介、功能描述、界面配置和参考设计,旨在帮助用户快速了解 Gowin Serial RapidIO IP 的特性及使用方法。本手册中的软件界面截图参考的是 1.9.9 Beta-2 版本,因软件版本升级,部分信息可能会略有差异,具体以用户软件版本的信息为准。

## 1.2 相关文档

通过登录高云半导体网站 <u>www.gowinsemi.com.cn</u> 可以下载、查看以下相关文档:

- SUG100, Gowin 云源软件用户指南

- DS981, GW5AT 系列 FPGA 产品数据手册

- DS1104, GW5AST 系列 FPGA 产品数据手册

## 1.3 术语、缩略语

本手册中出现的相关术语、缩略语及相关释义如表 1-1 所示。

#### 表 1-1 术语、缩略语

| 术语、缩略语                          | 全称                                                                                                        | 含义                     |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------|--|

| ackID                           | acknowledgement identifier                                                                                | 确认标识符,在器件间的物<br>理层进行传递 |  |

| CAR                             | Capability Register                                                                                       | 能力寄存器                  |  |

| Control Symbol                  | A quantum of information transmitted between two linked devices to manage packet flow between the devices | 控制符号                   |  |

| CRC                             | Cyclic Redundancy Code                                                                                    | 循环冗余编码                 |  |

| CRF                             | Critical Request Flow                                                                                     | 关键请求流                  |  |

| CSR Command and Status Register |                                                                                                           | 命令和状态寄存器               |  |

| Destination                     | The termination point of a packet on the RapidlO interconnect, also                                       | 目标器件                   |  |

IPUG1023-1.0 1(50)

| 术语、缩略语             | 全称                                                                                                                                                                       | 含义                      |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|

|                    | referred to as a target                                                                                                                                                  |                         |  |

| Device             | A generic participant on the<br>RapidIO interconnect that sends or<br>receives RapidIO transactions, also<br>called a processing element                                 | 设备                      |  |

| Device ID          | The identifier of an end point processing element connected to the RapidIO interconnect.                                                                                 | 设备 ID                   |  |

| Doorbell           | A port on a device that is capable of generating an interrupt to a processor                                                                                             | 门铃                      |  |

| Double-word        | An eight byte quantity, aligned on eight byte boundaries.                                                                                                                | 双字                      |  |

| End point          | A processing element which is the source or destination of transactions through a RapidIO fabric                                                                         | 端点                      |  |

| FPGA               | Field Programmable Gate Array                                                                                                                                            | 现场可编程门阵列                |  |

| Ftype              | Format Type                                                                                                                                                              | 包格式类型                   |  |

| IP                 | Intellectual Property                                                                                                                                                    | 知识产权                    |  |

| Mailbox            | Dedicated hardware that receives messages                                                                                                                                | 信箱                      |  |

| Operation          | A set of transactions between end point devices in a RapidIO system (requests and associated responses) such as a read or a write                                        | 操作                      |  |

| Packet             | A set of information transmitted between devices in a RapidIO system                                                                                                     | 数据包                     |  |

| PCS                | Physical Coding Sublayer                                                                                                                                                 | 物理编码子层                  |  |

| PMA                | Physical Media Attachment                                                                                                                                                | 物理介质连接                  |  |

| Priority           | The relative importance of a transaction or packet; in most systems a higher priority transaction or packet will be serviced or transmitted before one of lower priority | 优先级                     |  |

| rdsize             | Read Size                                                                                                                                                                | 读字节长度                   |  |

| srcTID             | The Packet's Transaction ID                                                                                                                                              | 源器件事务 ID                |  |

| Transaction        | A specific request or response packet transmitted between end point devices in a RapidIO system                                                                          | 事务                      |  |

| Ttype              | Transaction Type                                                                                                                                                         | 事务类型                    |  |

| wdptr Word Pointer |                                                                                                                                                                          | 控制读/写数据字节数及其在<br>双字中的位置 |  |

IPUG1023-1.0 2(50)

1 关于本手册 1.4 技术支持与反馈

| 术语、缩略语 | 全称         | 含义    |

|--------|------------|-------|

| wrsize | Write Size | 写字节长度 |

## 1.4 技术支持与反馈

高云半导体提供全方位技术支持,在使用过程中如有任何疑问或建议,可直接与公司联系:

网址: www.gowinsemi.com.cn

E-mail: <a href="mailto:support@gowinsemi.com">support@gowinsemi.com</a>

Tel: +86 755 8262 0391

IPUG1023-1.0 3(50)

2 功能简介 2.1 概述

# 2功能简介

## 2.1 概述

Gowin Serial RapidIO IP 按照 RapidIO 协议 V2.1 版本进行设计,应用于 RapidIO 系统中的端点设备(Endpoint Device)。该 IP 包含协议规定的逻辑层(Logical Layer)、传输层(Transport Layer)和物理层(Physical Layer),提供用户独立的发送请求事务接口、接收请求事务接口、发送响应事务接口、接收响应事务接口和维护事务接口。

#### 表 2-1 Gowin Serial RapidIO IP 概述

| Gowin Serial RapidIO IP |                                   |  |  |  |

|-------------------------|-----------------------------------|--|--|--|

| 逻辑资源                    | 参见表 2-2                           |  |  |  |

| 交付文件                    | 交付文件                              |  |  |  |

| 设计文件                    | Verilog(encrypted)                |  |  |  |

| 参考设计                    | Verilog                           |  |  |  |

| TestBench               | Verilog                           |  |  |  |

| 测试设计流程                  |                                   |  |  |  |

| 综合软件                    | GowinSynthesis®                   |  |  |  |

| 应用软件                    | Gowin Software(V1.9.9 Beta-2 及以上) |  |  |  |

#### 注!

可登录高云半导体网站查看芯片支持信息。

## 2.2 主要特性

#### 通用特性

● 参照 RapidIO 协议 V2.1 版本设计

#### 逻辑层特性

- 支持读事务(NREAD)、写事务(NWRITE)、带响应的写事务(NWRITE\_R)、流写事务(SWRITE)、响应事务(Response)、消息事务(MESSAGE)、门铃事务(DOORBELL)、Atomic 事务和维护事务(Maintenance)的发送和接收

- Arbiter 可选,可选 fixed priority 或 round robin 模式

IPUG1023-1.0 4(50)

2 功能简介 2.3 资源利用

#### 传输层特性

● 支持 8 bits、16 bits 位宽的设备 ID(DeviceID)

#### 物理层特性:

- 支持 1x、2x 和 4x 通道数

- 支持每通道线速率 1.25Gbps、2.5Gbps、3.125Gbps、5.0Gbps

- 支持接收流控(Receiver flow control)

- 支持 IDLE1

- 缓存(Buffer) 深度 8/16/32 可配

- 支持数据包(Packet)缓存资源的动态释放

- 支持数据包(Packet)的重传恢复

- 支持数据包(Packet)的错误恢复

#### 注!

- 暂不支持从 2x/4x 回退到 1x, 暂不支持从 4x 回退到 2x

- 暂不支持 5Gbps 2x 模式, 暂不支持 2.5Gbps/3.125Gbps/5Gbps 4x 模式

- 暂不支持发送流控(Transmitter flow control)

- 暂不支持 crf(Critical request flow)处理

## 2.3 资源利用

通过 Verilog 语言实现 Gowin Serial RapidIO IP。因使用器件的密度、速度和等级不同,其性能和资源利用情况可能不同。以高云 GW5AT 系列 FPGA 为例,Serial RapidIO IP 资源利用情况如表 2-2 所示。

表 2-2 Gowin Serial RapidIO IP 占用资源

| Lane  | Buffer<br>Depth | 占用资源     |      |     |       |       |

|-------|-----------------|----------|------|-----|-------|-------|

| Width |                 | Register | LUT  | ALU | BSRAM | SSRAM |

|       | 8               | 7069     | 6506 | 610 | 20    | 0     |

| 1x    | 16              | 7141     | 6543 | 631 | 24    | 0     |

|       | 32              | 7233     | 6722 | 680 | 32    | 0     |

|       | 8               | 7369     | 6662 | 628 | 20    | 0     |

| 2x    | 16              | 7441     | 6793 | 649 | 24    | 0     |

|       | 32              | 7533     | 6933 | 698 | 32    | 0     |

|       | 8               | 8668     | 7021 | 670 | 20    | 0     |

| 4x    | 16              | 8740     | 7235 | 691 | 24    | 0     |

|       | 32              | 8832     | 7215 | 740 | 32    | 0     |

IPUG1023-1.0 5(50)

3 功能描述 3.1 系统框图

# 3功能描述

## 3.1 系统框图

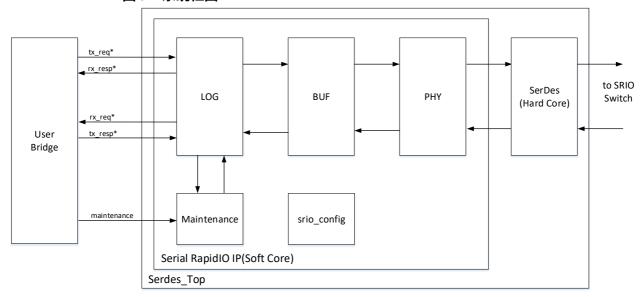

Gowin Serial RapidIO IP 的系统框图如图 3-1 所示。IP 包含 RapidIO 协议定义的逻辑层、传输层、物理层处理,包含 Buffer 缓冲机制,包含协议规定的 CARs 和 CSRs。IP 提供用户发送请求事务接口、接收请求事务接口、接收响应事务接口和维护事务接口。

#### 图 3-1 系统框图

#### 注!

系统框图接口说明如下:

- tx req\*: 发送请求事务接口

- rx resp\*: 接收响应事务接口

- rx\_req\*:接收请求事务接口

- tx resp\*: 发送响应事务接口

- maintenance: 维护事务访问接口

IPUG1023-1.0 6(50)

## 3.2 模块功能

本章节介绍 Gowin Serial RapidIO IP 各个子模块的功能。

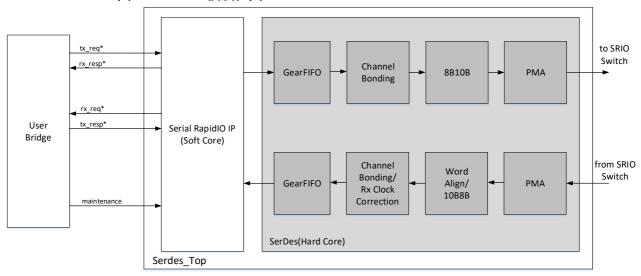

## 3.2.1 SerDes 模块

SerDes 模块:使用 Gowin FPGA 内部的 Serdes 硬核(Hard Core),支持 8B10B 编解码、通道对齐(Channel Bonding)和接收时钟调整(Rx Clock Correction)。

#### 注!

Serial RapidIO IP v1.0 版本尚未开放 SerDes 的接收时钟调整(Rx Clock Correction)功能,预计下一个版本会开放。所以用户应用 V1.0 IP 时,对接的两块开发板的 SerDes 参考时钟需要同源。

SerDes 模块输出数据对应的 PCS 时钟频率与线速率有关,PCS 时钟用于 SerDes GearFIFO 的 Fabric 侧,PCS 时钟也用于 PHY 模块的部分设计:

- 通道线速率为 1.25Gbps, PCS 时钟 31.25M。

- 通道线速率为 2.5Gbps, PCS 时钟 62.5M。

- 通道线速率为 3.125Gbps, PCS 时钟 78.125M。

- 通道线速率为 5Gbps, PCS 时钟 125M。

#### 图 3-2 SerDes 模块框图

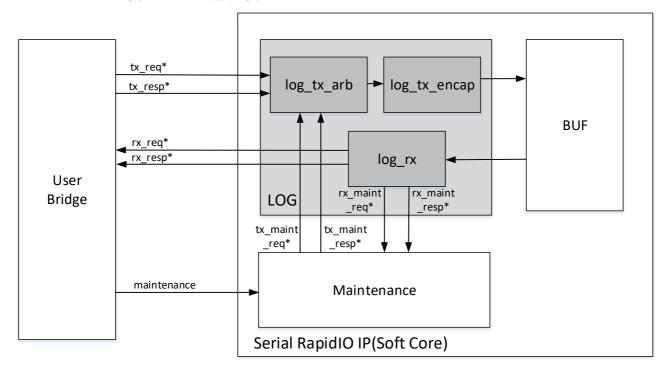

## 3.2.2 LOG 模块

LOG 模块:对应 RapidIO 协议中的逻辑层和传输层,包含发送方向和接收方向。

● 发送方向:子模块 log\_tx\_arb 对输入的四组信号进行仲裁,四组信号分别为发送维护请求事务、发送维护响应事务、发送请求事务、发送响应事务。子模块 log\_tx\_encap 按照协议对数据进行封装后发送给下一级BUF 模块。

IPUG1023-1.0 7(50)

● 接收方向:子模块 log\_rx 按照协议进行解析并拆分出四组信号,四组接收信号包含接收维护请求事务、接收维护响应事务、接收请求事务和接收响应事务,分别提供独立的接口。

- 请求事务:包含读事务(NREAD)、写事务(NWRITE)、带响应写事务(NWRITE\_R)、流写事务(SWRITE)、Atomic 事务、消息事务(MESSAGE)、门铃事务(DOORBELL)。

- 响应事务(Response)表示对请求事务的响应。

- 维护(Maintenance)请求事务用于对协议定义的寄存器进行操作,包含写寄存器或者读寄存器操作。

- 维护(Maintenance)响应事务表示对维护(Maintenance)请求事务的响应。

#### 图 3-3 LOG 模块框图

#### 3.2.3 BUF 模块

BUF 模块:对应 RapidIO 协议中的 Buffer 缓冲机制,通过 GUI 界面可选 8/16/32 三种缓存深度,分为发送方向和接收方向。

- 发送方向将事务包按照优先级(priority)放入不同的队列中,四种优先级都有对应的一个队列。发送方向在物理层空闲进行发包时,优先发送优先级更高的事务包。每个发送的事务包都会添加确认标识符(ackID)。若对端设备返回事务包被正确接收,才会在队列里将对应事务包进行释放,否则会开始重传,再次发送传输出错的事务包。

- 接收方向将来自物理层的数据包按顺序放入 fifo,并把数据传输给 LOG 模块。

IPUG1023-1.0 8(50)

## 3.2.4 PHY 模块

PHY 模块:对应 RapidIO 协议中的物理层,分为发送方向和接收方向。

● 发送方向:包含对事务包进行 CRC 添加,产生控制符号(Control Symbol),对控制符号(Control Symbol)和事务包进行合并,对合并后的数据进行跨时钟域处理,在包(packet)与包(packet)之间填充 IDLE 序列。

● 接收方向的处理:包含端口(port)初始化,链路(link)初始化,对数据进行跨时钟域处理,从接收数据里提取出事务包和控制符号,并进行CRC 校验,根据接收到的控制符号(Control Symbol)进行相应的操作。

#### 3.2.5 Maintenance 模块

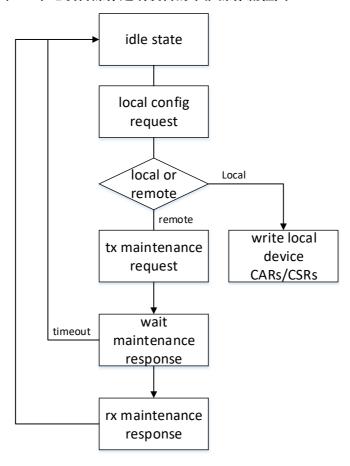

Maintenance 模块:对维护事务进行处理,包含三种功能,一种是处理远端(Remote)设备发起的访问本地寄存器的维护(Maintenance)操作(Operation),一种是处理本地(Local)设备发起的访问远端(Remote)寄存器的维护(Maintenance)操作,最后一种是本地(Local)设备访问本地寄存器。

● 处理远端(Remote)设备发起的访问本地寄存器的维护 (Maintenance)操作(Operation):接收 LOG 层的维护请求事务,判 断是读操作还是写操作,然后操作 IP 内部维护的寄存器,完成后生成对 应的响应事务,并将响应事务发送给 LOG 层。

IPUG1023-1.0 9(50)

## idle state rx maintenance request Write or Read Read Write write Read CARs/CSRs CARs/CSRs generate generate maintenance maintenance read response write response tx maintenance response

#### 图 3-4 远端设备操作本地设备的维护操作流程图

● 处理本地(Local)设备发起的访问远端(Remote)寄存器的维护 (Maintenance)操作:接收本地设备通过配置接口发起的寄存器读写 操作,判断是访问本地设备还是远端设备,若访问远端设备,则向 LOG 层发送维护请求事务,然后等待 LOG 层的接收维护响应事务,若 正确接收到响应事务,则通过本地配置接口返回结果,若超时未收到应 答,则返回错误并置位 maintenance timeout o 信号。

#### 注!

本地设备每发起一次对远端设备的维护事务操作,需要先操作寄存器 0x10100 和寄存器 0x10104,正确配置维护事务包的请求信息(srcTID、prio、crf、Destination ID 和 hop count),然后再通过配置接口发起请求。

IPUG1023-1.0 10(50)

图 3-5 本地设备操作远端设备的维护操作流程图

本地(Local)设备访问本地寄存器:接收本地设备通过配置接口发起的寄存器读写操作,判断是访问本地设备还是远端设备,若访问本地设备,则向 Srio\_config 模块发起寄存器读写,并将结果返回给配置接口。

## 3.2.6 Srio\_config 模块

Srio\_config 模块:根据 RapidIO 协议,定义本地设备的能力寄存器(CARs)和命令状态寄存器(CSRs)。远端设备或本地设备可访问 srio\_config 模块进行读寄存器操作或者写寄存器操作。

IPUG1023-1.0 11(50)

3 功能描述 3.3 用户接口

## 3.3 用户接口

Gowin Serial RapidIO 提供的用户侧接口简介如下:

- 时钟接口:用户输入 IP Core 的工作时钟

- 复位接口:用户对 IP Core 进行复位操作

- 发送请求事务接口:用户发起 I/O 请求事务总线接口

- 发送响应事务接口:用户发起 I/O 响应事务总线接口

- 接收请求事务接口:用户接收 I/O 请求事务总线接口

- 接收响应事务接口:用户接收 I/O 响应事务总线接口

- 维护(Maintenance)接口:用户操作维护事务接口,用于访问本地 IP 内部寄存器或访问远端设备寄存器

- 状态接口:端口(port)初始化状态,链路(Link)状态和其它便于 Debug 的端口状态

- SerDes 相关接口: SerDes 复位及 SerDes 状态接口。

## 3.4 端口列表

Gowin Serial RapidIO IP 的详细端口图如图 3-6 所示。

IPUG1023-1.0 12(50)

#### 图 3-6 Gowin Serial RapidIO IP 端口图

IPUG1023-1.0 13(50)

表 3-1 Gowin Serial RapidIO IP 端口列表

| 表 3-1 Gowin Serial R<br>端口名称 | 1/0    | 位宽 | 描述                                                                                                                                                                                                                                                       |

|------------------------------|--------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 时钟与复位                        | I      |    |                                                                                                                                                                                                                                                          |

| sys_rst_i                    | input  | 1  | 复位信号,高电平有效。                                                                                                                                                                                                                                              |

| srio_clk_i                   | input  | 1  | 工作时钟,LOG、BUF 和部分 PHY 的工作时钟,时钟频率与配置模块有关:  ■ 1.25G 1x,15.625M  ■ 1.25G 2x,31.25M  ■ 1.25G 4x,62.5M  ■ 2.5G 1x,31.25M  ■ 2.5G 2x,62.5M  ■ 3.125G 1x,39.0625M  ■ 3.125G 2x,78.125M  ■ 5G 1x,62.5M  注! PHY 另外一部分的工作时钟频率为SerDes PCS 层工作时钟频率,详见3.2.1 SerDes 模块。 |

| clk_lock_i                   | input  | 1  | 工作时钟 PLL 锁定指示,高电平表示 PLL 锁定。                                                                                                                                                                                                                              |

| user_pcs_clk_i input         | input  | 1  | 输入 SerDes PCS 层工作时钟,需与<br>srio_clk_i 同源:<br>● 1.25Gbps,31.25M<br>● 2.5Gbps,62.5M<br>● 3.125Gbps,78.125M<br>● 5Gbps,125M                                                                                                                                  |

| srio_ui_clk_o                | output | 1  | 输出工作时钟,将输入的 srio_clk_i 直接进行输出,用户侧设计可直接使用此时钟信号。                                                                                                                                                                                                           |

| srio_ui_rst_o                | output | 1  | 输出复位信号,高电平有效,用户侧设计<br>可直接使用此复位信号。                                                                                                                                                                                                                        |

| cfg_rst_i                    | input  | 1  | 配置模块同步复位信号,高有效。                                                                                                                                                                                                                                          |

| cfg_clk_i                    | input  | 1  | 配置模块工作时钟。                                                                                                                                                                                                                                                |

| 发送请求事务接口                     |        |    |                                                                                                                                                                                                                                                          |

| tx_req_trac_valid_i          | input  | 1  | 发送请求事务接口的数据有效指示,高电<br>平有效,为高表示总线上的数据有效。                                                                                                                                                                                                                  |

| tx_req_trac_ready_<br>o      | output | 1  | 发送请求事务接口的握手信号,当tx_req_trac_ready_o 为高且tx_req_trac_valid_i 为高时,总线上的数据有效。                                                                                                                                                                                  |

| tx_req_trac_last_i           | input  | 1  | 发送请求事务接口的包尾指示信号,高电平有效,当 tx_req_trac_last_i 为高且 tx_req_trac_valid_i 为高且 tx_req_trac_ready_o 为高时表示事务包的 最后一个时钟周期。                                                                                                                                           |

IPUG1023-1.0 14(50)

| 端口名称                       | I/O    | 位宽          | 描述                                                                                                                                                                                                                      |

|----------------------------|--------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tx_req_trac_data_i         | input  | [63:0]      | 发送请求事务接口的数据,包含事务包<br>(packet)的 header 信息和 data。                                                                                                                                                                         |

|                            |        |             | 发送请求事务接口事务包(packet)对应<br>的 ID 信息,位宽与 GUI 选项 "Device ID<br>Width"有关。<br>● GUI 选项 "Device ID Width"为 8bit                                                                                                                 |

| tx_req_trac_id_info<br>_i  | input  | [N-<br>1:0] | 时,N为16,其中[7:0]对应目的器件ID(Destination ID),其中[15:8]对应源器件ID(Source ID)。                                                                                                                                                      |

|                            |        |             | ● GUI 选项 "Device ID Width"为 16bit 时, N 为 32, 其中[15:0]对应目的器件 ID(Destination ID),其中[31:16]对应源器件 ID(Source ID)。                                                                                                            |

| 发送响应事务接口                   |        |             |                                                                                                                                                                                                                         |

| tx_resp_trac_valid_i       | input  | 1           | 发送响应事务接口的数据有效指示,高电<br>平有效,为高表示总线上的数据有效。                                                                                                                                                                                 |

| tx_resp_trac_ready<br>_o   | output | 1           | 发送响应事务接口的握手信号,当 tx_resp_trac_ready_o 为高且 tx_resp_trac_valid_i 为高时,总线上的数据有效。                                                                                                                                             |

| tx_resp_trac_last_i        | input  | 1           | 发送响应事务接口的包尾指示信号,高电平有效,当 tx_resp_trac_last_i 为高且 tx_resp_trac_valid_i 为高且 tx_resp_trac_ready_o 为高时表示事务包的最后一个时钟周期。                                                                                                        |

| tx_resp_trac_data_i        | input  | [63:0]      | 发送响应事务接口的数据,包含事务包<br>(packet)的 header 信息和 data。                                                                                                                                                                         |

| tx_resp_trac_id_info<br>_i | input  | [N-<br>1:0] | 发送响应事务接口事务包(packet)对应的 ID 信息,位宽与 GUI 选项"Device ID Width"有关。  ● GUI 选项"Device ID Width"为 8bit时,N为 16,其中[7:0]对应目的器件ID(Destination ID),其中[15:8]对应源器件 ID(Source ID)。  ● GUI 选项"Device ID Width"为 16bit时,N为 32,其中[15:0]对应目的器 |

|                            |        |             | 件 ID(Destination ID),其中[31:16]<br>对应源器件 ID(Source ID)。                                                                                                                                                                  |

| 接收请求事务接口                   |        |             |                                                                                                                                                                                                                         |

| rx_req_trac_ready_i        | input  | 1           | 接收请求事务接口的握手信号,当rx_req_trac_ready_i 为高且rx_req_trac_valid_o 为高时,总线上的数据有效。                                                                                                                                                 |

| rx_req_trac_valid_o        | output | 1           | 接收请求事务接口的数据有效指示,高电平有效,为高表示总线上的数据有效。                                                                                                                                                                                     |

IPUG1023-1.0 15(50)

| 端口名称                       | I/O    | 位宽          | 描述                                                                                                                                                                                                                                                                       |

|----------------------------|--------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rx_req_trac_last_o         | output | 1           | 接收请求事务接口的包尾指示信号,高电平有效,当 rx_req_trac_ready_i 为高且 rx_req_trac_valid_o 为高且 rx_req_trac_last_o 为高时表示事务包的最后一个时钟周期。                                                                                                                                                            |

| rx_req_trac_data_o         | output | [63:0]      | 接收请求事务接口的数据,包含事务包<br>(packet)的 header 信息和 data。                                                                                                                                                                                                                          |

| rx_req_trac_id_info<br>_o  | output | [N-<br>1:0] | 接收请求事务接口事务包(packet)对应的 ID 信息,位宽与 GUI 选项"Device ID Width"有关。  ● GUI 选项"Device ID Width"为 8bit时,N为 16,其中[7:0]对应目的器件ID(Destination ID),其中[15:8]对应源器件 ID(Source ID)。  ● GUI 选项"Device ID Width"为 16bit时,N为 32,其中[15:0]对应目的器件ID(Destination ID),其中[31:16]对应源器件 ID(Source ID)。 |

| 接收响应事务接口                   |        |             |                                                                                                                                                                                                                                                                          |

| rx_resp_trac_ready<br>_i   | input  | 1           | 接收响应事务接口的握手信号,当 rx_resp_trac_ready_i 为高且 rx_resp_trac_valid_o 为高时,总线上的数 据有效。                                                                                                                                                                                             |

| rx_resp_trac_valid_<br>o   | output | 1           | 接收响应事务接口的数据有效指示,高电平有效,为高表示总线上的数据有效。                                                                                                                                                                                                                                      |

| rx_resp_trac_last_o        | output | 1           | 接收响应事务接口的包尾指示信号,高电平有效,当 rx_resp_trac_ready_i 为高且 rx_resp_trac_valid_o 为高且 rx_resp_trac_last_o 为高时表示事务包的 最后一个时钟周期。                                                                                                                                                        |

| rx_resp_trac_data_<br>o    | output | [63:0]      | 接收响应事务接口的数据,包含事务包<br>(packet)的 header 信息和 data。                                                                                                                                                                                                                          |

| rx_resp_trac_id_inf<br>o_o | output | [N-<br>1:0] | 接收响应事务接口事务包(packet)对应的 ID 信息,位宽与 GUI 选项"Device ID Width"有关。  GUI 选项"Device ID Width"为 8bit时,N为 16,其中[7:0]对应目的器件ID(Destination ID),其中[15:8]对应源器件 ID(Source ID)。  GUI 选项"Device ID Width"为 16bit时,N为 32,其中[15:0]对应目的器件 ID(Destination ID),其中[31:16]对应源器件 ID(Source ID)。    |

| IP 核控制接口                   |        |             |                                                                                                                                                                                                                                                                          |

| force_reinit_i             | input  | 1           | 触发 PHY 层重新进行初始化,高电平有效,在 srio_ui_clk_o 时钟域下至少持续 2                                                                                                                                                                                                                         |

IPUG1023-1.0 16(50)

| 端口名称                    | I/O    | 位宽     | 描述                                                                                                                                                                                             |  |  |  |  |  |

|-------------------------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                         |        |        | 个时钟周期。                                                                                                                                                                                         |  |  |  |  |  |

| phy_tx_mce_i            | input  | 1      | 触发 PHY 层发送多播事件(Multicastevent)控制符号(Control Symbol),高电平有效,在 srio_ui_clk_o 时钟域下至少持续 1 个时钟周期。                                                                                                     |  |  |  |  |  |

| phy_tx_link_reset_i     | input  | 1      | 触发 PHY 层发送链路复位(link-request/reset-device)控制符号(Control Symbol),高电平有效。在 srio_ui_clk_o 时钟域下将 phy_tx_link_reset_i 置成高电平执行链路复位操作,需要等port_initialized_o 拉低,确定对端完成复位后,再重新将 phy_tx_link_reset_i 置成低电平。 |  |  |  |  |  |

| IP 核状态信号                |        | T      |                                                                                                                                                                                                |  |  |  |  |  |

| port_initialized_o      | output | 1      | 端口初始化完成信号,高有效。                                                                                                                                                                                 |  |  |  |  |  |

| link_initialized_o      | output | 1      | 链路初始化完成信号,高有效。                                                                                                                                                                                 |  |  |  |  |  |

| phy_rx_mce_o            | output | 1      | phy 层接收到多播事件(Multicastevent)控制符号(Control Symbol)标识,高有效。在 srio_ui_clk_o 时钟域下每 1 个时钟周期表示收到一个多播事件控制符号。                                                                                            |  |  |  |  |  |

| phy_rx_link_reset_o     | output | 1      | phy 层接收到至少 4 个连续的链路复位<br>(link-request/reset-device)控制符号<br>(Control Symbol),高有效。当至少收到 4<br>个连续的链路复位控制符号后,IP 会执行<br>复位操作。                                                                      |  |  |  |  |  |

| port_error_o            | output | 1      | 端口出错指示,高有效。                                                                                                                                                                                    |  |  |  |  |  |

| port_timeout_o          | output | [23:0] | 端口响应超时值,由 CSRs 里的 Port<br>Response Timeout Control 寄存器控制。                                                                                                                                      |  |  |  |  |  |

| srio_host_o             | output | 1      | 表示系统是 Host 设备,高电平有效,由<br>CSRs 里的 Port General Control 寄存器控<br>制。                                                                                                                               |  |  |  |  |  |

| master_enable_o         | output | 1      | Master 使能信号,高电平有效,由 CSRs<br>里的 Port General Control 寄存器控制。                                                                                                                                     |  |  |  |  |  |

| port_decode_error_<br>o | output | 1      | 端口解码出错标识,表示逻辑层接收到了<br>不支持的事务类型,高电平有效。                                                                                                                                                          |  |  |  |  |  |

| device_id_o             | output | [15:0] | 本地设备的 ID 信息,由 CSRs 里的 Base Device ID 寄存器控制。                                                                                                                                                    |  |  |  |  |  |

|                         |        |        | PHY 层 Debug 信息                                                                                                                                                                                 |  |  |  |  |  |

|                         |        |        | ● bit0~15, rsv                                                                                                                                                                                 |  |  |  |  |  |

| debug_info_o            | output | [31:0] | ● bit16~20,期望下一个接收包的确认<br>标识符。(The value of the ackID field<br>expected in the next packet the port<br>receives.)                                                                              |  |  |  |  |  |

IPUG1023-1.0 17(50)

| 端口名称           | I/O    | 位宽     | 描述                                                                                                                                                                                 |

|----------------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |        |        | <ul> <li>bit21~23, rsv</li> <li>bit24~28,端口状态:</li> <li>- 5'd2 表示端口遇到无法恢复的错误,无法接收数据包。(The port has encountered an unrecoverable error and is unable to accept packets.)</li> </ul> |

|                |        |        | - 5'd4 表示端口已重试数据包,并<br>且正在输入重试停止状态下等待<br>重新启动。(The port has retried<br>a packet and is waiting in the<br>input retry-stopped state to be<br>restarted.)                            |

|                |        |        | - 5'd5 表示端口遇到传输错误,正在输入错误停止状态下等待重新启动。(The port has encountered a transmission error and is waiting in the input error-stopped state to be restarted.)                               |

|                |        |        | - 5'd16 表示端口正常接收包。<br>(The port is accepting<br>packets.)                                                                                                                          |

|                |        |        | - 5'd0 表示复位状态。                                                                                                                                                                     |

|                |        |        | <ul><li>bit29~30, rsv</li><li>bit31, 链路多通道对齐指示, 高电平<br/>有效</li></ul>                                                                                                               |

| rxbuf_rewind_o | output | 1      | 接收方向发生重传指示,高有效。                                                                                                                                                                    |

| txbuf_rewind_o | output | 1      | 发送方向发生重传指示,高有效。                                                                                                                                                                    |

| 配置接口           |        |        |                                                                                                                                                                                    |

| cfg_sel_i      | input  | 1      | 片选使能信号,时钟域为 cfg_clk_i。                                                                                                                                                             |

| cfg_wr_i       | input  | 1      | 写控制信号,高表示当前操作为写操作。<br>时钟域为 cfg_clk_i。                                                                                                                                              |

| cfg_ena_i      | input  | 1      | 传输使能信号,高表示当前传输有效。时钟域为 cfg_clk_i。                                                                                                                                                   |

| cfg_addr_i     | input  | [21:0] | 地址线,字节地址。时钟域为 cfg_clk_i。                                                                                                                                                           |

| cfg_wdata_i    | input  | [31:0] | 写数据总线,时钟域为 cfg_clk_i。                                                                                                                                                              |

| cfg_strb_i     | input  | [3:0]  | 字节有效指示,目前 IP 保留未用,时钟域为 cfg_clk_i。                                                                                                                                                  |

| cfg_rdy_o      | output | 1      | Ready 信号,时钟域为 cfg_clk_i,时钟域<br>为 cfg_clk_i。                                                                                                                                        |

| cfg_rdata_o    | output | [31:0] | 读数据总线,时钟域为 cfg_clk_i。                                                                                                                                                              |

| cfg_slverr_o   | output | 1      | 总线出错指示,在 cfg_rdy_o 为高时有效。时钟域为 cfg_clk_i。                                                                                                                                           |

IPUG1023-1.0 18(50)

| 端口名称                        | I/O    | 位宽                                                                                                                      | 描述                                                                                                                                                                                   |  |  |  |  |  |

|-----------------------------|--------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| maintenance_interr<br>upt_o | output | 1                                                                                                                       | 维护事务中断指示,目前 IP 保留未用。时钟域为 cfg_clk_i。                                                                                                                                                  |  |  |  |  |  |

| maintenance_timeo<br>ut_o   | output | 1                                                                                                                       | 维护事务超时指示,高电平有效,表示配置接口请求的事务超时未收到正确的应答。时钟域为 cfg_clk_i。                                                                                                                                 |  |  |  |  |  |

| 用户侧控制 SerDes 相              | 美接口    |                                                                                                                         |                                                                                                                                                                                      |  |  |  |  |  |

| gtr12_rstn_i                | input  | 1                                                                                                                       | SerDes 通道复位信号,低有效,同时复位 IP 对应的所有 lane。                                                                                                                                                |  |  |  |  |  |

| gtr12_pcs_tx_rst_i          | input  | 1                                                                                                                       | SerDes PCS 层发送方向复位,高有效,同时复位 IP 对应的所有 lane。                                                                                                                                           |  |  |  |  |  |

| gtr12_pcs_rx_rst_i          | input  | 1                                                                                                                       | SerDes PCS 层接收方向复位,高有效,同时复位 IP 对应的所有 lane。                                                                                                                                           |  |  |  |  |  |

| gtr12_align_link_o          | output | [N-1:<br>0]                                                                                                             | SerDes 通道对齐状态,高表示链路正常,位宽和选项 Lane Width 选择的通道数对应,x1 时位宽为 1 bit, x2 时位宽为 2 bits, x4 时位宽为 4 bits。                                                                                       |  |  |  |  |  |

| gtr12_k_lock_o              | output | [N-1:<br>0]                                                                                                             | SerDes 通道 K 码锁定状态,高表示链路<br>正常,位宽和选项 Lane Width 选择的通<br>道数对应,x1 时位宽为 1 bit, x2 时位宽<br>为 2 bits, x4 时位宽为 4 bits。                                                                       |  |  |  |  |  |

| gtr12_pma_rx_lock<br>_o     | output | SerDes 通道接收 PMA 层锁定状态,高<br>[N-1: 示链路正常,位宽和选项 Lane Width 进<br>0] 择的通道数对应,x1 时位宽为 1 bit,x2<br>时位宽为 2 bits,x4 时位宽为 4 bits。 |                                                                                                                                                                                      |  |  |  |  |  |

| gtr12_pll_ok_o              | output | [N-1:<br>0]                                                                                                             | SerDes PLL 锁定状态,高表示时钟锁定。  ● 在配置界面的选项 PLL_Selection 选择 QPLL1 或 QPLL0 时,位宽为1bit。  ● 在配置界面的选项 PLL_Selection 选择 CPLL 时,位宽和选项 Lane Width选择的通道数对应,x1 时位宽为1bit,x2 时位宽为2 bits,x4 时位宽为4 bits。 |  |  |  |  |  |

| gtr12_pll_ck_ref_o          | output | 1                                                                                                                       | SerDes PLL 参考时钟输出。用户用此时 钟作为系统 PLL 的参考时钟,重新产生 IP 的工作时钟,具体参照参考设计。                                                                                                                      |  |  |  |  |  |

| gtr12_rx_fifo_rduse<br>wd_o | output | [N-1:<br>0]                                                                                                             | SerDes 通道接收 FIFO 读写两端的指针差异,位宽和选项 Lane Width 选择的通道数对应:  ■ x1 时位宽为 5 bits ■ x2 时位宽为 10 bits ■ x4 时位宽为 20 bits                                                                          |  |  |  |  |  |

| gtr12_tx_fifo_wruse<br>wd_o | output | [N-1:<br>0]                                                                                                             | SerDes 通道发送 fifo 读写两端的指针差异,位宽和选项 Lane Width 选择的通道                                                                                                                                    |  |  |  |  |  |

IPUG1023-1.0 19(50)

| 端口名称               | I/O    | 位宽 | 描述                                                                          |

|--------------------|--------|----|-----------------------------------------------------------------------------|

|                    |        |    | 数对应:                                                                        |

|                    |        |    | ● x1 时位宽为 5 bits                                                            |

|                    |        |    | ● x2 时位宽为 10 bits                                                           |

|                    |        |    | ● x4 时位宽为 20 bits                                                           |

| gtr12_tx_pcs_clk_o | output | 1  | SerDes 输出发送方向 PCS 层时钟                                                       |

| gtr12_rx_pcs_clk_o | output | 1  | SerDes 输出接收方向 PCS 层时钟                                                       |

| SerDes 硬核接口        |        |    |                                                                             |

| SerDes_*           | -      | -  | SerDes_开头的信号为 Serial RapidIO IP<br>与 SerDes 硬核连接信号,用户可不关<br>注,EDA 工具自动完成连线。 |

## 3.5 用户接口时序

## 3.5.1 I/O 事务接口时序图

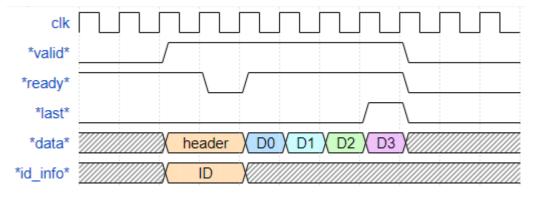

Gowin Serial RapidIO IP 为 I/O 事务提供 valid&ready 的握手接口。I/O 事务指除了维护(Maintenance)事务外的其它事务,包含读事务(NREAD)、写事务(NWRITE)、带响应写事务(NWRITE\_R)、流写事务(SWRITE)、消息事务(MESSAGE)、门铃事务(DOORBELL)和应答事务(Response)。

接口事务如图 3-7 所示,约定总线的第一个有效的时钟周期作为头信息(Header),剩余时钟周期作为数据载荷。当\*valid\*与\*ready\*同时为高时,当前的数据才有效,其中第一个有效的时钟周期对应 Header 信息,Header 信息包含当前事务包的类型、事务包的长度、优先级等,从第二个有效的时钟周期开始到有效的\*last\*信号,则传输事务包的载荷。需要注意有些事务包类型是不需要载荷的,此处\*last\*信号会出现在第一个有效的时钟周期处。\*data\*的位宽为 64bit,\*id\_info\*的位宽与 GUI 选择的 Device ID Width 有关。I/O 事务接口对应端口列表里的发送请求事务接口、发送响应事务接口、接收请求事务接口、接收响应事务接口。

#### 图 3-7 I/O 事务接口时序图

头信息(Header)定义如图 3-8 所示。Header 信息位宽固定为 64 bits,在每个事务包有效的第一个时钟周期传递。其中 R 表示保留字段

IPUG1023-1.0 20(50)

(Reserved),E 表示错误(Error),FTYPE 表示包格式类型,SrcTID 表示源器件事务 ID,Ttype 表示事务类型,FTYPE 与 TTYPE 组合成唯一标识事务的格式,prio 表示优先级(priority),crf(Critical Request Flow)表示关键请求流,addr 表示地址,Size 表示字节长度,msglen 表示组成MESSAGE 序列的包数,msgseg 表示当前事务包代表的消息段,mailbox表示当前事务包对应的邮箱。

| 图 3-8 Header 信息定 | 义 | 冬 |

|------------------|---|---|

|------------------|---|---|

| Packet Type | [63         | :56]         | [55          | :48]       |        | [47:      | 40]      | [3           | 39:3   | 2]     |        | [31:24] [23:16] [15:08] |               | [07:00] |                        |

|-------------|-------------|--------------|--------------|------------|--------|-----------|----------|--------------|--------|--------|--------|-------------------------|---------------|---------|------------------------|

| NREAD       |             | etid<br>8    | FTYPE2<br>4  | TTYPE<br>4 | R<br>1 | prio<br>2 | crf<br>1 | Siz e-1<br>8 | R<br>1 | R<br>1 |        |                         | addr<br>34    |         |                        |

| NWRITE      |             | TID<br>8     | FTYPE5<br>4  | TTYPE<br>4 | R<br>1 | prio<br>2 | crf<br>1 | Siz e-1<br>8 | R<br>1 |        |        |                         | addr<br>34    |         |                        |

| SWRITE      | 1           | R<br>8       | FTYPE6<br>4  | R<br>4     | R<br>1 | prio<br>2 | crf<br>1 | R<br>8       | R<br>1 |        |        |                         | addr<br>34    |         |                        |

| DOORBELL    |             | TID<br>8     | FTYPE10<br>4 | R<br>4     | R<br>1 | prio<br>2 | crf<br>1 | R<br>8       | R<br>1 | R<br>1 | R<br>2 | Info MSB<br>8           | Info LSB<br>8 |         | R<br>16                |

| MESSAGE     | msglen<br>4 | msgseg<br>4  | FTYPE11<br>4 | R<br>4     | R<br>1 | prio<br>2 | crf<br>1 | Siz e-1<br>8 | R<br>1 | R<br>1 | R<br>2 |                         | R<br>24       |         | mailbox R letter 6 2 2 |

| RESPONSE    | -           | et info<br>8 | FTYPE13      | TTYPE      | R      | prio      | crf      | R            | E      | R      |        |                         | R             |         |                        |

| RESPONSE    | -           | et TID<br>8  | 4            | 4          | 1      | 2         | 1        | 8            | 1      | 1      |        |                         | 34            |         |                        |

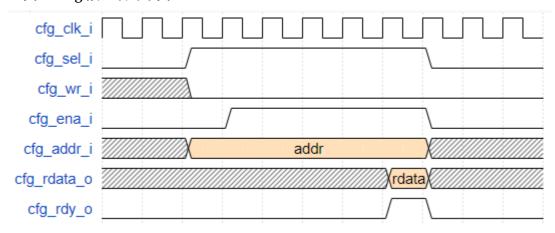

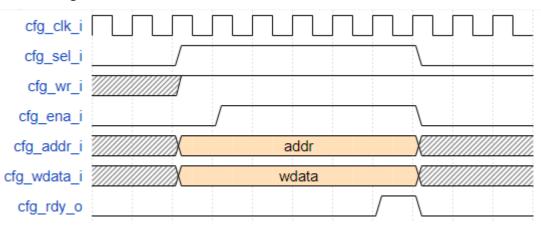

#### 3.5.2 配置接口时序图

Gowin Serial RapidIO IP 提供配置接口,用户可通过配置接口访问本地 IP 内部寄存器或访问远端设备的寄存器,配置接口读时序如图 3-9 所示,写时序如图 3-10 所示。如果访问本地 IP 内部寄存器,发起配置请求后几个时钟周期就会响应返回结果。但如果访问远端设备的寄存器,则需等待较长时间才会响应返回结果,若超过本地寄存器设置的 timeout 值未收到响应,则会拉高 maintenance\_timeout\_o 端口一个电平,表示请求事务发生了超时。

#### 图 3-9 cfg 接口读时序图

IPUG1023-1.0 21(50)

## 图 3-10 cfg 接口写时序图

## 3.6 寄存器接口

#### 表 3-2 寄存器地址空间

| 地址空间(Byte)        | 访问设备 | 描述                                                                                                                         |

|-------------------|------|----------------------------------------------------------------------------------------------------------------------------|

| 0x200000~0x3ffffc | 远端设备 | 访问远端设备的寄存器地址空间,具体寄存器定义需参照远端设备的寄存器定义。bit21仅用于区分是访问本地设备还是远端设备。bit21为高电平表示访问远端设备,实际往远端设备发送的地址(cfg_offset)为低21bit(bit0~bit20)。 |

| 0x000000~0x1ffffc | 本地设备 | 访问本地设备的寄存器地址空间,具体寄存器定义参照下文介绍。bit21 仅用于区分是访问本地设备还是远端设备。bit21 为低电平表示访问本地设备,实际最终访问本地设备 IP srio_config 模块只有低 21bit(bit0~20)。   |

#### 表 3-3 本地设备寄存器列表概述

| 地址 (Byte)      | 名称                                 | 类型 | 描述                      |

|----------------|------------------------------------|----|-------------------------|

| 0x00~0x3c CARs | S                                  |    |                         |

| 0x0            | Device Identity CAR                | RO | GUI 可配,参见 RapidIO 协议介绍。 |

| 0x4            | Device Information CAR             | RO | GUI 可配,参见 RapidIO 协议介绍。 |

| 0x8            | Assembly Identity CAR              | RO | GUI 可配,参见 RapidIO 协议介绍。 |

| 0xc            | Assembly Information CAR           | RO | GUI 可配,参见 RapidIO 协议介绍。 |

| 0x10           | Processing Element<br>Features CAR | RO | GUI 可配,参见 RapidIO 协议介绍。 |

| 0x14           | Switch Port<br>Information CAR     | RO | rsv                     |

| 0x18           | Source Operations                  | RO | 源端支持的操作类型,目前固定          |

IPUG1023-1.0 22(50)

| 地址 (Byte)       | 名称                                                 | 类型 | 描述                                      |

|-----------------|----------------------------------------------------|----|-----------------------------------------|

|                 | CAR                                                |    | 成初始值,若有需要后续开放<br>GUI 可配。                |

| 0x1c            | Destination Operations CAR                         | RO | 目的端支持的操作类型,目前固定成初始值,若有需要后续开放<br>GUI 可配。 |

| 0x20~0x3c       | Reserved                                           | _  | -                                       |

| 0x40~0xfc CSRs  |                                                    |    |                                         |

| 0x40~0x48       | Reserved                                           | -  | -                                       |

| 0x4c            | Processing Element<br>Logical Layer Control<br>CSR | RO | 支持的地址位宽。                                |

| 0x50~0x54       | Reserved                                           | =  | -                                       |

| 0x58            | Local Configuration<br>Space Base Address 0<br>CSR | RO | 地址空间配置。                                 |

| 0x5c            | Local Configuration<br>Space Base Address 1<br>CSR | RW | 地址空间配置。                                 |

| 0x60            | Base Device ID CSR                                 | RW | GUI 可配,设置设备 ID。                         |

| 0x64            | Reserved                                           | =  | -                                       |

| 0x68            | Host Base Device ID<br>Lock CSR                    | RW | 用于初始化。                                  |

| 0x6c            | Component Tag CSR                                  | RW | 组件标签值。                                  |

| 0x70~0xfc       | Reserved                                           | -  | -                                       |

| 0x0100~0xfffc 扭 | i展地址                                               |    |                                         |

| 0x100           | LP-Serial Register<br>Block Header                 | RO | 地址空间配置。                                 |

| 0x104~0x11c     | Reserved                                           |    | -                                       |

| 0x120           | Port Link Timeout<br>Control CSR                   | RW | 端口建链超时寄存器。                              |

| 0x124           | Port Response<br>Timeout Control CSR               | RW | 端口响应超时寄存器。                              |

| 0x128~0x138     | Reserved                                           | -  | -                                       |

| 0x13c           | Port General Control<br>CSR                        | RW | GUI 可配。                                 |

| 0x140           | Port n Link<br>Maintenance Request<br>CSR          | RO | rsv                                     |

| 0x144           | Port n Link<br>Maintenance<br>Response CSR         | RO | rsv                                     |

| 0x148           | Port n Local ackID<br>CSR                          | RO | rsv                                     |

| 0x14c~0x1508    | Reserved                                           | -  | -                                       |

| 0x154           | Port n Control 2 CSR                               | RO | 端口控制。                                   |

IPUG1023-1.0 23(50)

| 地址 (Byte)                   | 名称                                                | 类型 | 描述                           |

|-----------------------------|---------------------------------------------------|----|------------------------------|

| 0x158                       | Port n Error and<br>Status CSR                    | RO | 端口出错情况和状态。                   |

| 0x15c                       | Port n Control CSR                                | RW | 端口控制状态。                      |

| 0x160~0x3fc                 | Reserved                                          | _  | -                            |

| 0x400                       | LP-Serial Lane<br>Command and Status<br>Registers | RO | 拓展空间指示。                      |

| 0x410/0x430/0<br>x450/0x470 | Lane n Status 0 CSRs                              | _  | 通道状态                         |

| 0x414/0x434/0<br>x454/0x474 | Lane n Status 1 CSRs                              | RO | rsv                          |

| 0x010000~0x1fff             | fc 自定义地址                                          |    |                              |

| 0x10000                     | Watermarks CSR                                    | RW | rsv                          |

| 0x10004                     | Buffer Control CSR                                | RO | 缓存控制寄存器。                     |

| 0x10100                     | Maintenance Request<br>Information Register       | RW | 维护事务请求信息寄存器。                 |

| 0x10104                     | Maintenance Request HopCount Register             | RW | 维护事务请求跳数设置<br>(hopcount)寄存器。 |

| 0x10108                     | Maintenance<br>Response Time-out<br>Scale Registe | RW | 维护事务响应超时刻度寄存器。               |

#### 注!

寄存器读写定义:

- RC表示读清

- RO表示只读

- RW 表示读写

## 3.6.1 Device Identity CAR (0x0)

## 表 3-4 Device Identity CAR 各个 bit 含义

| 名称                   | 比特位   | 类型 | 描述                                                                | 默认值 |

|----------------------|-------|----|-------------------------------------------------------------------|-----|

| DeviceIdentity       | 31:16 | RO | GUI 可设置(选项"Device<br>Identity for Endpoint"),由设备<br>供应商分配和管理。     | 0x0 |

| DeviceVendorIdentity | 15:0  | RO | GUI 可设置(选项"Device<br>Vendor Identity"),由 RapidIO<br>贸易联盟分配给设备供应商。 | 0x0 |

IPUG1023-1.0 24(50)

#### 3.6.2 Device Information CAR (0x4)

表 3-5 Device Information CAR 各个 bit 含义

| 名称             | 比特位   | 类型 | 描述       | 默认值 |

|----------------|-------|----|----------|-----|

| rsv            | 31:12 | RO | N/A      | 0x0 |

| Major version  | 11:8  | RO | 大版本号     | 0x0 |

| Minor Revision | 7:4   | RO | 小版本号     | 0x0 |

| Patch          | 3:0   | RO | BUG 修复标识 | 0x0 |

## 3.6.3 Assembly Identity CAR (0x8)

表 3-6 Assembly Identity CAR 各个 bit 含义

| 名称                 | 比特位   | 类型 | 描述                                                          | 默认值 |

|--------------------|-------|----|-------------------------------------------------------------|-----|

| Assyldentity       | 31:16 | RO | GUI 可设置(选项"Assembly Identifier"),由 RapidIO 贸易联盟唯一分配给设备供应商。  | 0x0 |

| AssyVendorldentity | 15:0  | RO | GUI 可设置(选项"Assembly<br>Vendor Identifier"),由设备供<br>应商分配和管理。 | 0x0 |

## 3.6.4 Assembly Information CAR (0xc)

#### 表 3-7 Assembly Information CAR 各个 bit 含义

| 名称                  | 比特位   | 类型 | 描述                                                       | 默认值   |

|---------------------|-------|----|----------------------------------------------------------|-------|

| AssyRev             | 31:16 | RO | GUI 可设置(选项"Assembly<br>Revision Level"),由设备供应<br>商分配和管理。 | 0x0   |

| ExtendedFeaturesPtr | 15:0  | RO | 扩展功能的起始地址。                                               | 0x100 |

## 3.6.5 Processing Element Features CAR (0x10)

#### 表 3-8 Processing Element Features CAR 各个 bit 含义

| 名称        | 比特位  | 类型 | 描述                                                                    | 默认值 |

|-----------|------|----|-----------------------------------------------------------------------|-----|

| Bridge    | 31   | RO | GUI 可设置(选项 "Processing<br>Element Features"),当前端点<br>用作 Bridge 功能。    | 0x0 |

| Memory    | 30   | RO | GUI 可设置(选项 "Processing Element Features"),当前端点用作 Memory 功能。           | 0x0 |

| Processor | 29   | RO | GUI 可设置(选项 "Processing<br>Element Features"),当前端点<br>用作 Processor 功能。 | 0x0 |

| rsv       | 28   | RO | N/A                                                                   | 0x0 |

| rsv       | 27   | RO | N/A                                                                   | 0x0 |

| rsv       | 26:7 | RO | N/A                                                                   | 0x0 |

| rsv       | 6    | RO | N/A                                                                   | 0x0 |

| rsv       | 5    | RO | N/A                                                                   | 0x0 |

IPUG1023-1.0 25(50)

| 名称                                  | 比特位 | 类型 | 描述                                                                                                  | 默认值 |

|-------------------------------------|-----|----|-----------------------------------------------------------------------------------------------------|-----|

| common_tra<br>ns_large_su<br>pport  | 4   | RO | GUI 可设置,选项 "Device ID<br>Width"设置为 8 bits 则值为<br>1'b0。选项 "Device ID Width"<br>设置为 16 bits 则值为 1'b1。 | 0x0 |

| Extended_fe atures                  | 3   | RO | 支持拓展功能,值固定为<br>1'b1。                                                                                | 0x1 |

| Extended_a<br>ddressing_s<br>upport | 2:0 | RO | 仅支持 34 bits 地址模式                                                                                    | 0x1 |

## 3.6.6 Switch Port Information CAR (0x14)

## 表 3-9 Switch Port Information CAR 各个 bit 含义

| 名称  | 比特位  | 类型 | 描述  | 默认值 |

|-----|------|----|-----|-----|

| rsv | 31:0 | RO | N/A | 0x0 |

## 3.6.7 Source Operations CAR (0x18)

#### 表 3-10 Source Operations CAR 各个 bit 含义

| 名称                              | 比特位   | 类型 | 描述                  | 默认值 |

|---------------------------------|-------|----|---------------------|-----|

| rsv                             | 31:16 | RO | N/A                 | 0x0 |

| Source_Read                     | 15    | RO | 置高电平,后续开放 GUI<br>可配 | 0x1 |

| Source_Write                    | 14    | RO | 置高电平,后续开放 GUI<br>可配 | 0x1 |

| Source_Streaming_w rite         | 13    | RO | 置高电平,后续开放 GUI<br>可配 | 0x1 |

| Source_Write_with_r esponse     | 12    | RO | 置高电平,后续开放 GUI<br>可配 | 0x1 |

| Source_Message                  | 11    | RO | 置高电平,后续开放 GUI<br>可配 | 0x1 |

| Source_Doorbell                 | 10    | RO | 置高电平,后续开放 GUI<br>可配 | 0x1 |

| Source_Atomic_com pare_and_swap | 9     | RO | 置高电平,后续开放 GUI<br>可配 | 0x1 |

| Source_Atomic_test_<br>and_swap | 8     | RO | 置高电平,后续开放 GUI<br>可配 | 0x1 |

| Source_Atomic_incre ment        | 7     | RO | 置高电平,后续开放 GUI<br>可配 | 0x1 |

| Source_Atomic_decr<br>ement     | 6     | RO | 置高电平,后续开放 GUI<br>可配 | 0x1 |

| Source_Atomic_set               | 5     | RO | 置高电平,后续开放 GUI<br>可配 | 0x1 |

| Source_Atomic_clear             | 4     | RO | 置高电平,后续开放 GUI<br>可配 | 0x1 |

IPUG1023-1.0 26(50)

| 名称                 | 比特位 | 类型 | 描述                  | 默认值 |

|--------------------|-----|----|---------------------|-----|

| Source_Atomic_swap | 3   | RO | 置高电平,后续开放 GUI<br>可配 | 0x1 |

| rsv                | 2:0 | RO | N/A                 | =   |

## 3.6.8 Destination Operations CAR (0x1c)

## 表 3-11 Destination Operations CAR 各个 bit 含义

| 名称                                      | 比特位   | 类型 | 描述               | 默认值 |

|-----------------------------------------|-------|----|------------------|-----|

| rsv                                     | 31:16 | RO | N/A              | 0x0 |

| Destination_Read                        | 15    | RO | 置高电平,后续开放 GUI 可配 | 0x1 |

| Destination_Write                       | 14    | RO | 置高电平,后续开放 GUI 可配 | 0x1 |

| Destination_Streamin g_write            | 13    | RO | 置高电平,后续开放 GUI 可配 | 0x1 |

| Destination_Write_wit h_response        | 12    | RO | 置高电平,后续开放 GUI 可配 | 0x1 |

| Destination_Message                     | 11    | RO | 置高电平,后续开放 GUI 可配 | 0x1 |

| Destination_Doorbell                    | 10    | RO | 置高电平,后续开放 GUI 可配 | 0x1 |

| Destination_Atomic_c<br>ompare_and_swap | 9     | RO | 置高电平,后续开放 GUI 可配 | 0x1 |

| Destination_Atomic_t est_and_swap       | 8     | RO | 置高电平,后续开放 GUI 可配 | 0x1 |

| Destination_Atomic_i ncrement           | 7     | RO | 置高电平,后续开放 GUI 可配 | 0x1 |

| Destination_Atomic_<br>decrement        | 6     | RO | 置高电平,后续开放 GUI 可配 | 0x1 |

| Destination_Atomic_s et                 | 5     | RO | 置高电平,后续开放 GUI 可配 | 0x1 |

| Destination_Atomic_c<br>lear            | 4     | RO | 置高电平,后续开放 GUI 可配 | 0x1 |

| Destination_Atomic_s wap                | 3     | RO | 置高电平,后续开放 GUI 可配 | 0x1 |

| rsv                                     | 2:0   | RO | N/A              | -   |

## 3.6.9 Processing Element Logical Layer Control CSR (0x4c)

## 表 3-12 Processing Element Logical Layer Control CSR 各个 bit 含义

| 名称                           | 比特位  | 类型 | 描述          | 默认值 |

|------------------------------|------|----|-------------|-----|

| rsv                          | 31:3 | RO | N/A         | 0x0 |

| Extended_addressing _control | 2:0  | RO | 支持 34bit 地址 | 0x1 |

IPUG1023-1.0 27(50)

## 3.6.10 Local Configuration Space Base Address 0 CSR (0x58)

## 表 3-13 Local Configuration Space Base Address 0 CSR 各个 bit 含义

| 名称  | 比特位  | 类型 | 描述  | 默认值 |

|-----|------|----|-----|-----|

| rsv | 31:3 | RO | N/A | 0x0 |

## 3.6.11 Local Configuration Space Base Address 1 CSR (0x5c)

#### 表 3-14 Local Configuration Space Base Address 1 CSR 各个 bit 含义

| •           | -     |    |          |       |

|-------------|-------|----|----------|-------|

| 名称          | 比特位   | 类型 | 描述       | 默认值   |

| rsv         | 31    | RO | N/A      | 0x0   |

| LCSBA_ADDR1 | 30:21 | RW | 默认 0x3ff | 0x3ff |

| rsv         | 20:0  | RO | N/A      | 0x0   |

## 3.6.12 Base Device ID CSR (0x60)

#### 表 3-15 Base Device ID CSR 各个 bit 含义

| 名称                 | 比特位   | 类型 | 描述                                                                 | 默认值    |

|--------------------|-------|----|--------------------------------------------------------------------|--------|

| rsv                | 31:24 | RO | N/A                                                                | 0x0    |

| Base_deviceID      | 23:16 | RW | GUI 可设置(选项 "Local<br>Device ID"),Device ID<br>Width 为 8 bits 时有效。  | 0xff   |

| Large_base_devicel | 15:0  | RW | GUI 可设置(选项 "Local<br>Device ID"),Device ID<br>Width 为 16 bits 时有效。 | 0x00ff |

## 3.6.13 Host Base Device ID Lock CSR (0x68)

#### 表 3-16 Host Base Device ID Lock CSR 各个 bit 含义

| 名称                 | 比特位   | 类型 | 描述    | 默认值    |

|--------------------|-------|----|-------|--------|

| rsv                | 31:16 | RO | N/A   | 0x0    |

| Host_base_deviceID | 15:0  | RW | 用于初始化 | 0xffff |

## 3.6.14 Component Tag CSR (0x6c)

### 表 3-17 Component Tag CSR 各个 bit 含义

| 名称            | 比特位  | 类型 | 描述    | 默认值 |

|---------------|------|----|-------|-----|

| component_tag | 31:0 | RW | 组件标签值 | 0x0 |

## 3.6.15 LP-Serial Register Block Header (0x100)

### 表 3-18 LP-Serial Register Block 各个 bit 含义

| 名称                            | 比特位  | 类型 | 描述                              | 默认值   |

|-------------------------------|------|----|---------------------------------|-------|

| Extended_Features_<br>Pointer | 31:0 | RO | 下一个拓展空间的起始地址                    | 0x400 |

| Extended_Features_I D         | 15:0 | RO | Hard-wired extended features ID | 0x1   |

IPUG1023-1.0 28(50)

## 3.6.16 Port Link Timeout Control CSR (0x120)

#### 表 3-19 Port Link Timeout Control CSR 各个 bit 含义

| 名称                       | 比特位  | 类型 | 描述                                                      | 默认值    |

|--------------------------|------|----|---------------------------------------------------------|--------|

| Port_Link_Timeout_V alue | 31:8 | RW | 端口建链超时值,GUI 可配<br>(选项 "Port Link Time-out<br>Control")。 | 0xffff |

| Rsv                      | 7:0  | RO | N/A                                                     | 0x0    |

## 3.6.17 Port Response Timeout Control CSR (0x124)

## 表 3-20 Port Response Timeout Control CSR 各个 bit 含义

| 名称                           | 比特位  | 类型 | 描述                                                          | 默认值    |

|------------------------------|------|----|-------------------------------------------------------------|--------|

| Port_Response_Time out_Value | 31:8 | RW | 端口响应超时值,GUI 可配<br>(选项 "Port Response<br>Time-out Control")。 | 0xffff |

| Rsv                          | 7:0  | RO | N/A                                                         | 0x0    |

## 3.6.18 Port General Control CSR (0x13c)

### 表 3-21 Port General Control CSR 各个 bit 含义

| 名称            | 比特位  | 类型 | 描述                                   | 默认值    |

|---------------|------|----|--------------------------------------|--------|

| Host          | 31   | RW | GUI 可配(选项 "Port<br>General Control") | 0xffff |

| Master_Enable | 30   | RW | GUI 可配(选项 "Port<br>General Control") | -      |

| Discovered    | 29   | RW | GUI 可配(选项 "Port<br>General Control") | -      |

| rsv           | 28:0 | RO | N/A                                  | 0x0    |

## 3.6.19 Port n Link Maintenance Request CSR (0x140)

### 表 3-22 Port n Link Maintenance Request CSR 各个 bit 含义

| 名称  | 比特位  | 类型 | 描述  | 默认值 |

|-----|------|----|-----|-----|

| rsv | 31:0 | RO | N/A | 0x0 |

## 3.6.20 Port n Link Maintenance Response CSR (0x144)

#### 表 3-23 Port n Link Maintenance Response CSR 各个 bit 含义

| 名称  | 比特位  | 类型 | 描述  | 默认值 |

|-----|------|----|-----|-----|

| rsv | 31:0 | RO | N/A | 0x0 |

## 3.6.21 Port n Local ackID CSR (0x148)

#### 表 3-24 Port n Local ackID CSR 各个 bit 含义

| 名称  | 比特位  | 类型 | 描述  | 默认值 |

|-----|------|----|-----|-----|

| rsv | 31:0 | RO | N/A | 0x0 |

IPUG1023-1.0 29(50)

## 3.6.22 Port n Control 2 CSR (0x154)

表 3-25 Port n Control 2 CSR 各个 bit 含义

| 名称                           | 比特位   | 类型 | 描述                                                                                                                                                                                                       | 默认值 |

|------------------------------|-------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| rsv                          | 31:16 | RO | N/A                                                                                                                                                                                                      | 0x0 |

| Gbaud_Support_and<br>_Enable | 15:6  | RO | GUI 选择的速率:  1.25Gbps - 10'b0001010111  2.5Gbps - 10'b0001011101  3.125Gbps - 10'b0001110101  5Gbps - 10'b0011010101                                                                                      | N/A |

| rsv                          | 5:4   | RO | N/A                                                                                                                                                                                                      | 0x0 |

| Select_Baudrate              | 3:0   | RO | GUI 选择的速率:      4'b0000 - no rate selected      4'b0001 - 1.25 Gbps      4'b0010 - 2.5 Gbps      4'b0011 - 3.125 Gbps      4'b0100 - 5.0 Gbps      4'b0110 - 6.25 Gbps      4'b0110 - 4'b1111 - Reserved | -   |

## 3.6.23 Port n Error and Status CSR (0x158)

### 表 3-26 Port n Error and Status CSR 各个 bit 含义