# Gowin goConfig JTAG IP

# 用户指南

IPUG1035-1.0,2023-09-28

#### 版权所有 © 2023 广东高云半导体科技股份有限公司

GO<sup>₩</sup>IN高云,₩,Gowin,云源以及高云均为广东高云半导体科技股份有限公司注册商标,本手册中提到的其他任何商标,其所有权利属其拥有者所有。未经本公司书面许可,任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部,并不得以任何形式传播。

#### 免责声明

本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止反言或其它方式授予任何知识产权许可。除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。高云半导体不承诺对这些文档进行适时的更新。

## 版本信息

| 日期         | 版本   | 说明    |

|------------|------|-------|

| 2023-09-28 | V1.0 | 初始版本。 |

# 目录

| 目 | 录                                   | i   |

|---|-------------------------------------|-----|

| 图 | 目录                                  | iii |

| 表 | 目录                                  | iv  |

| 1 | 关于本手册                               | . 1 |

|   | 1.1 手册内容                            | 1   |

|   | 1.2 相关文档                            |     |

|   | 1.3 术语、缩略语                          | 1   |

|   | 1.4 技术支持与反馈                         | 2   |

| 2 | 概述与性能                               | . 3 |

|   | 2.1 升级功能概述                          | 4   |

|   | 2.2 JTAG 接口                         | 5   |

|   | 2.2.1 JTAG 基本特性                     | 5   |

|   | 2.2.2 JTAG 时序特性                     | 5   |

|   | 2.3 IP 特性                           | 6   |

|   | 2.4 资源占用                            | 6   |

| 3 | 功能描述                                | . 7 |

|   | 3.1 goConfig JTAG 结构框图              | 7   |

|   | 3.2 IP 典型应用                         | 8   |

|   | 3.3 Gowin goConfig JTAG IP 背景升级控制指令 | 8   |

| 4 | 信号定义                                | 10  |

| 5 | 使用说明                                | 12  |

|   | 5.1 软件配置                            | 12  |

|   | 5.2 流程说明                            | 14  |

|   | 5.2.1 前期准备                          | 14  |

|   | 5.2.2 擦 Flash                       | 14  |

|   | 5.2.3 写 Flash                       | 15  |

|   | 5.3 注意事项        | . 15 |

|---|-----------------|------|

|   | 5.3.1 IO 约束     | . 15 |

|   | 5.3.2 OSC 输出    |      |

|   | 5.3.3 缓存限制      |      |

| 6 | 界面配置            |      |

| 7 | 参考设计            | 19   |

|   | 7.1 参考设计        | . 19 |

|   | 7.1.1 FPGA 工程说明 | . 19 |

|   | 7.1.2 参考设计文件    | . 20 |

|   |                 |      |

# 图目录

| 图 2-1 JTAG 接口时序                   | 5  |

|-----------------------------------|----|

| 图 3-1 结构框图                        | 7  |

| 图 3-2 擦 Flash 示例                  | 9  |

| 图 3-3 写 Flash 示例                  | 9  |

| 图 5-1 打开 Configuration 选项         | 12 |

| 图 5-2 配置背景升级为 GoConfig(1.9.8.11)  | 13 |

| 图 5-3 配置背景升级为 GoConfig(1.9.9Beta) | 13 |

| 图 6-1 IP Core Generator 选项        | 16 |

| 图 6-2 打开 goConfig JTAG IP 核       | 17 |

| 图 6-3 goConfig JTAG IP 配置界面       | 18 |

| 图 7-1 参考设计-基本结构示意图                | 20 |

# 表目录

| 表 1-1 术语、缩略语                    | 1  |

|---------------------------------|----|

| 表 2-1 Gowin goConfig JTAG IP 概述 | 3  |

| 表 2-2 JTAG 接口时序说明               | 5  |

| 表 2-3 资源消耗参考                    | 6  |

| 表 3-1 指令定义                      | 8  |

| 表 <b>4-1 IO</b> 接口定义            | 10 |

| 表 8-1 参考设计 src 文件夹内容列表          | 20 |

IPUG1035-1.0 iv

1 关于本手册 1.1 手册内容

#

# 1.1 手册内容

Gowin® goConfig JTAG IP 用户指南主要内容包括性能简介、功能描述、信号定义、使用说明、界面配置,用于帮助用户快速了解 goConfig JTAG IP 的产品特性、特点及使用方法。

# 1.2 相关文档

通过登录高云®半导体网站 <u>www.gowinsemi.com</u> 可以下载、查看以下相关文档。

- DS100, GW1N 系列 FPGA 产品数据手册

- DS117, GW1NR 系列 FPGA 产品数据手册

- SUG100, Gowin 云源软件用户指南

- SUG283, Gowin 原语用户指南

# 1.3 术语、缩略语

表 1-1 中列出了本手册中出现的相关术语、缩略语及相关释义。

#### 表 1-1 术语、缩略语

| 术语、缩略语 | 全称                            | 含义       |

|--------|-------------------------------|----------|

| ACK    | Acknowledge                   | 响应       |

| FPGA   | Field Programmable Gate Array | 现场可编程门阵列 |

| JTAG   | Joint Test Action Group       | 联合测试工作组  |

| IP     | Intellectual Property         | 知识产权     |

| SRAM   | Static Random Access Memory   | 静态随机存储器  |

IPUG1035-1.0 1(20)

1 关于本手册 1.4 技术支持与反馈

# 1.4 技术支持与反馈

高云半导体提供全方位技术支持,在使用过程中如有任何疑问或建议,可直接与公司联系:

网址: www.gowinsemi.com

E-mail: <a href="mailto:support@gowinsemi.com">support@gowinsemi.com</a>

Tel: +86 755 8262 0391

IPUG1035-1.0 2(20)

# **2**概述与性能

背景升级是近年来用户需求很高的功能。在使用 Gowin FPGA 产品上存在"功能 A",若用户想将"功能 A"升级或者重新烧录为"功能 B",且在升级或烧录"功能 B"过程中芯片的"功能 A"不会停止工作,升级完成后"功能 B"可以马上加载到芯片上,这就需要背景升级技术。

Gowin goConfig JTAG IP 可实现 JTAG 端口的在线升级功能,用户通过 JTAG 端口对 FPGA 进行烧录,实现对内部存储的数据替换,实现背景升级。

#### 表 2-1 Gowin goConfig JTAG IP 概述

| Gowin goConfig JTAG IP |                              |  |  |

|------------------------|------------------------------|--|--|

| IP核应用                  |                              |  |  |

| 芯片支持                   | ● GW1N(R)-2C系列               |  |  |

| 心月又持                   | ● GW1N-1P5C系列                |  |  |

| 逻辑资源                   | 请参见表2-3。                     |  |  |

| 交付文件                   |                              |  |  |

| 设计文件                   | Verilog (encrypted)          |  |  |

| 参考设计                   | Verilog                      |  |  |

| TestBench              | Verilog                      |  |  |

| 测试设计流程                 |                              |  |  |

| 综合软件                   | GowinSynthesis <sup>®</sup>  |  |  |

| 应用软件                   | Gowin Software(V1.9.8.11及以上) |  |  |

IPUG1035-1.0 3(20)

2.机 升级功能概述

# 2.1 升级功能概述

实现升级功能包括两个过程:编程(Program),配置(Configure)。

● 编程(Program Flash): 将高云半导体云源®软件生成的比特流数据,写入到 Flash 的过程(下文简称"写入 Flash")。

● 配置 (Configure SRAM): 将 Flash 中的比特流数据,加载到 FPGA 的 SRAM 存储区的过程 (下文简称"载入 SRAM")。

#### 注!

- 普通升级:进行编程(Program)时,需要先擦除 SRAM(即停止了正在运行的功能),再"写入 Flash"。

- 背景升级:进行编程(Program)时,不会擦除 SRAM(即不影响正在运行的功能),直接"写入 Flash"。

- 配置(Configure)时,"普通升级"与"背景升级"操作过程一致。

背景升级功能示例如下:

用户一般通过正在运行的"功能 A",将待更新的"功能 B"写入 Flash;然后用户可在需要更新功能时,通过一系列操作,将 Flash 内的"功能 B"载入 SRAM 内,完成功能的更新。

#### 注!

- "功能 A"按照背景升级功能操作时,必须带有背景升级功能的模块。本文中,即 "功能 A"必须带 Gowin goConfig JTAG IP。

- "功能 B"可以不带背景升级功能的模块,但是后续不能通过"功能 B"完成背景升级。

- "写入 Flash"过程,"功能 A"仍然正常运行;"载入 SRAM"过程,"功能 A"会 停止运行。

IPUG1035-1.0 4(20)

2 概述与性能 2.2 JTAG 接口

# 2.2 JTAG 接口

### 2.2.1 JTAG 基本特性

Gowin goConfig JTAG IP 的 JTAG 接口为四线模式,通用名称分别为: TCK、TMS、TDI、TDO。

● TCK:测试时钟输入

● TMS:测试模式选择

● TDI: 测试数据输入

● TDO:测试数据输出

JTAG 端口数据发送/接收方式: 低字节低比特先发送。以发送 0xABCDFE01 为例,字节发送顺序为 0x01>0xFE>0xCD>0xAB;以 0x01 为例,比特发送顺序为 1>0>0>0>0>0。

## 2.2.2 JTAG 时序特性

Gowin goConfig JTAG IP 的时序要求示意图。

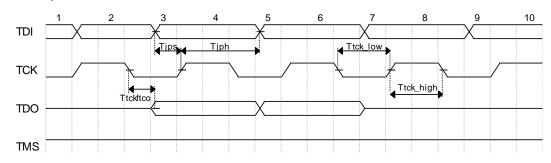

#### 图 2-1 JTAG 接口时序

Gowin goConfig JTAG IP 的接口时序,详细说明如表 2-2 所示。已验证可支持 JTAG-TCK 的速率范围 80KHz~1.5MHz。

表 2-2 JTAG 接口时序说明

| 名称                    | 描述                                   | Min | Max  | Unit | 备注 |

|-----------------------|--------------------------------------|-----|------|------|----|

| F <sub>TCK</sub>      | Clock Frequency                      | 80  | 1500 | KHz  |    |

| T <sub>tck_low</sub>  | LOW period of the TCK                | 250 | 6250 | ns   |    |

| T <sub>tck_high</sub> | HIGH period of the TCK               | 250 | 6250 | ns   |    |

| T <sub>tckftco</sub>  | Time from TCK falling edge to output | -   | 210  | ns   | _  |

| T <sub>jps</sub>      | JTAG Setup Time                      | 10  | -    | ns   |    |

| T <sub>jph</sub>      | JTAG Hold Time                       | 10  | -    | ns   |    |

IPUG1035-1.0 5(20)

2 概述与性能 2.3 IP 特性

# 2.3 IP 特性

Gowin goConfig JTAG IP 特性包括:

- 四线 JTAG 接口

- JTAG-TCK 频率范围 80KHz~1.5MHz

- 支持输出 25 MHz 时钟

注!

JTAG 接口的其他特点可参考 <u>UG290,《Gowin FPGA 产品编程配置手册》</u>。

# 2.4 资源占用

Gowin goConfig JTAG IP,以高云 GW1N-2C 器件为例,其资源利用情况如表 2-3 所示。

#### 表 2-3 资源消耗参考

| 器件      | 编程语言    | LUT | ALU | REG | BSRAM |

|---------|---------|-----|-----|-----|-------|

| GW1N-2C | Verilog | 175 | 49  | 249 | 1     |

IPUG1035-1.0 6(20)

# 3功能描述

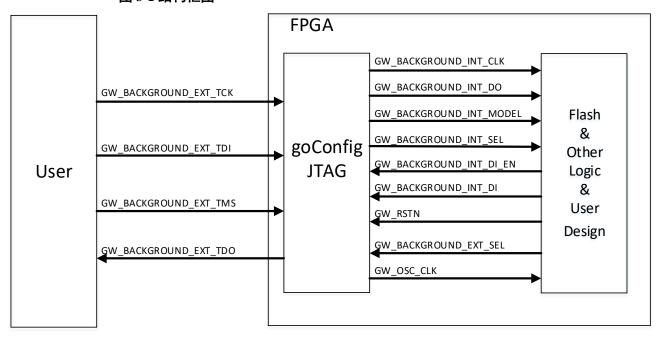

# 3.1 goConfig JTAG 结构框图

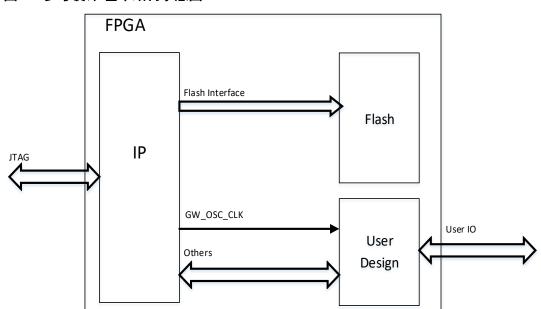

Gowin goConfig JTAG IP 的应用结构可分为用户(User)侧与 FPGA 侧。User 侧用于控制 JTAG 接口,以及其他用户功能。FPGA 侧连接 Flash,以及用户需要在 FPGA 上实现的功能。若仅考虑 IP,User 侧通过 JTAG 接口控制 FPGA 内的 IP,进而控制 Flash,完成背景升级的功能。

#### 注!

文档中主要描述 User 侧接口操作,本文不涉及 Flash 接口的详细操作与时序。

Gowin goConfig JTAG IP 实现框图如图 3-1 所示,User 侧控制 JTAG 信号,其他信号根据实际的功能需求选择控制或使用。

图 3-1 结构框图

IPUG1035-1.0 7(20)

3 功能描述 3.2 IP 典型应用

# 3.2 IP 典型应用

Gowin goConfig JTAG IP 实现将待发送数据通过 JTAG 接口下发到 Flash 控制端的功能。因此 IP 不会完成 JTAG 相关状态机的解析以及跳转。 IP 适用于以下情况:

- 1. User 侧使用较低速(JTAG-TCK: 80KHz~1.5MHz)的 JTAG 接口编程。

- 2. User 侧 JTAG 接口时钟信号(JTAG-TCK)不连续的 Flash 编程。 部分器件编程时,JTAG-TCK 速率较低可能导致 Flash 编程不成功的问题。

JTAG-TCK 信号不连续指:有效数据发送时,JTAG-TCK 可能可以满足器件编程的需求(或满足 IP 的 JTAG-TCK 要求);但存在某些原因导致JTAG 信号暂时不传输信号(一次传输并未完成)并保持当前的状态。当JTAG-TCK 信号不连续时间过长,即保持当前状态的时间过长时,部分器件的编程可能出现问题。

# 3.3 Gowin goConfig JTAG IP 背景升级控制指令

Gowin goConfig JTAG IP 的指令主要用于烧写 Flash(简称写 Flash)与擦除 Flash(简称擦 Flash)。IP 可分为工作与空闲状态。工作状态即执行"写 Flash"过程,或者"擦 Flash"过程。空闲状态,即除了"写 Flash"、"擦 Flash"的其他所有过程。

#### 指令定义

Gowin goConfig JTAG IP 支持的指令如表 3-1 所示;指令通过 JTAG-TCK 与 JTAG-TDI 发送完成。

例如,需要发送"0xABCDFE01",则 JTAG-TCK 作为时钟,JTAG-TDI 发送数据; JTAG-TMS 不关心,但建议保持当前状态。

| # | 0 1 | 北人 | ペーツ |

|---|-----|----|-----|

| 枢 | 3-I | 相  | 〉定义 |

| 序号 | 指令名称    | 指令地址(CMD)  | 描述        | 备注 |

|----|---------|------------|-----------|----|

| 1  | ERASE_S | 0xABCDFE01 | 擦除Flash开始 |    |

| 2  | ERASE_E | 0xABCDFE02 | 擦除Flash结束 |    |

| 3  | PROG_S  | 0xABCDFE03 | 烧写Flash开始 | _  |

| 4  | PROG_E  | 0xABCDFE04 | 烧写Flash结束 |    |

IPUG1035-1.0 8(20)

Gowin goConfig JTAG IP 的"ERASE\_S"与"ERASE\_E"为一组,配合可完成擦除的相关功能;"PROG\_S"与"PROG\_E"为一组,配合可完成写 Flash 功能。

#### 注!

- ERASE S 只能通过 ERASE E 退出; PROG S 只能通过 PROG E 退出。

- 本文中 "FPGA 擦除 Flash" 特指 JTAG 接口 "FPGA 擦除 Flash 流程"的全步骤,需参考 *UG290,《Gowin FPGA 产品编程配置手册》*。

- 本文中"擦 Flash"特指 JTAG 接口"FPGA 擦除 Flash 流程"的步骤中本 IP 会执行的步骤。

#### 擦 Flash 指令

ERASE\_S: 0xABCDFE01

ERASE E: 0xABCDFE02

擦 Flash 过程使用示例如图;其中"Data"指"FPGA 擦除 Flash"过程中发送的 0x15 以及 0x75;"Waiting time"指正常擦除需要等待的时间,发送的值与正常发送的一致。等待时间由用户控制。

#### 图 3-2 擦 Flash 示例

| ERASE_S Da | ta Waiting time | ERASE_E |

|------------|-----------------|---------|

|------------|-----------------|---------|

#### 注!

- 白色底纹:正常操作

- 灰色底纹:使用 IP 时,需要额外发送的数据

- 正常操作: <u>UG290,《Gowin FPGA 产品编程配置手册》</u>内执行"FPGA 擦除Flash"或"FPGA 烧写 Flash"的操作

#### 写 Flash 指令

PROG S: 0xABCDFE01

PROG E: 0xABCDFE02

写 Flash 过程使用示例如图: 其中"Writing data"指需要正常写 Flash 的数据。

#### 图 3-3 写 Flash 示例

| PROG_S | Writing data | PROG_E |

|--------|--------------|--------|

|--------|--------------|--------|

IPUG1035-1.0 9(20)

# 4信号定义

Gowin goConfig JTAG IP IO 接口定义见表 4-1。

#### 表 4-1 IO 接口定义

| 信号名称                        | 方向     | 描述                              | IO分配约束 | 备注           |

|-----------------------------|--------|---------------------------------|--------|--------------|

| goConfig通用接口                |        |                                 |        |              |

| GW_RSTN                     | Input  | IP复位,低有效                        | -      |              |

| GW_OSC_CLK                  | Output | OSC输出时钟,25MHz                   | -      |              |

| goConfig特殊接口                |        |                                 |        |              |

| GW_BACKGROUN<br>D_EXT_SEL   | Input  | 背景升级使能输入<br>1:使能(建议默认)<br>0:不使能 | -      |              |

| goConfig外部接口                |        |                                 |        |              |

| GW_BACKGROUN<br>D_EXT_TCK   | Input  | JTAG-TCK,时钟输入                   | -      | 所有信号<br>输入输出 |

| GW_BACKGROUN<br>D_EXT_TDI   | Input  | JTAG-TDI,数据输入                   | -      | 方向均以<br>IP为参 |

| GW_BACKGROUN<br>D_EXT_TMS   | Input  | JTAG-TMS,模式选择                   | -      | 考。           |

| GW_BACKGROUN<br>D_EXT_TDO   | Output | JTAG-TDO,数据输出                   | -      |              |

| goConfig Flash接口            |        |                                 |        |              |

| GW_BACKGROUN<br>D_INT_CLK   | Output | IP-Flash接口时钟                    | 自动     |              |

| GW_BACKGROUN<br>D_INT_MODEL | Output | IP-Flash接口模式选择                  | 自动     |              |

| GW_BACKGROUN                | Output | IP-Flash接口数据输出                  | 自动     | 10(20)       |

IPUG1035-1.0 10(20)

| 信号名称                        | 方向     | 描述                     | IO分配约束 | 备注 |

|-----------------------------|--------|------------------------|--------|----|

| D_INT_DO                    |        |                        |        |    |

| GW_BACKGROUN<br>D_INT_DI    | Input  | IP-Flash接口数据输入         | 自动     |    |

| GW_BACKGROUN<br>D_INT_DI_EN | Input  | IP-Flash接口输入数据<br>有效信号 | 自动     |    |

| GW_BACKGROUN<br>D_INT_SEL   | Output | 背景升级使能输出               | 自动     |    |

#### 注!

- IO 分配约束各定义如下:

- "-":无限制,一般 IP 接口的使用方式。可以自由命名,可以自由约束位置。

- "自动":自动约束位置。不能自由命名,不能约束位置。即顶层 IO 名字需命名 为特定 IO 名字,且不能约束位置;高云云源软件会自动约束位置。

- "GW\_BACKGROUND\_EXT\_SEL": 在没有使能变化需求时,需要保持输入为"1" (高电平)。

- IO 接口分类定义如下:

- "goConfig 通用接口": 其他 IP 中也能常见的 IO。例如时钟,复位等。

- "goConfig 特殊接口": 背景升级 IP 中可能包含的 IO。其 IO 的功能通常与背景 升级的整个流程相关或某些特定功能。

- "goConfig 外部接口": 背景升级 IP 中主要通讯的 IO。其 IO 的管脚定义、功能等,有比较成熟的规范。例如 I2C、SPI、JTAG等。

- "goConfig Flash 接口": 背景升级 IP 中连接 Flash 的 IO。其 IO 所有都需要定义在顶层,名称必须与 IP 完全一致,且不能约束位置。

IPUG1035-1.0 11(20)

5 使用说明 5.1 软件配置

# **5**使用说明

本章将描述 Gowin goConfig JTAG IP 在使用时云源软件配置、推荐的 IP 流程、注意事项等。

# 5.1 软件配置

在综合(Synthesizes)带背景升级 IP 的工程前,需要先更改云源软件配置,Gowin goConfig JTAG IP 才能正常工作。

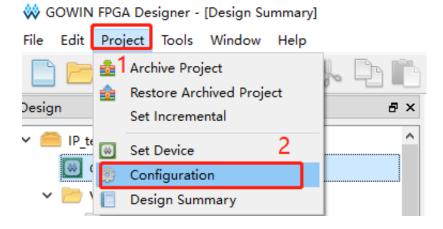

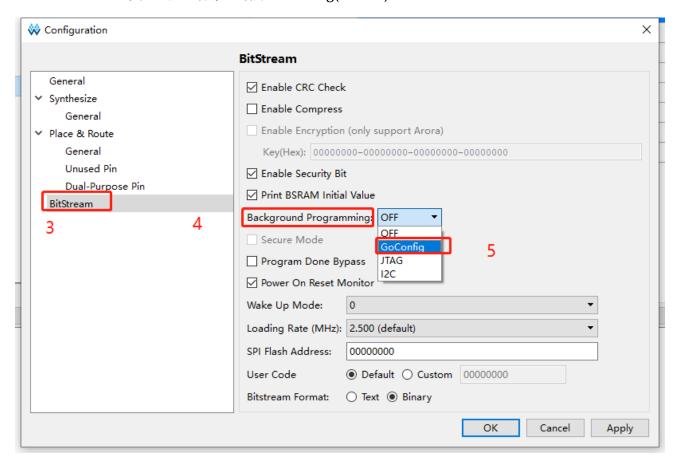

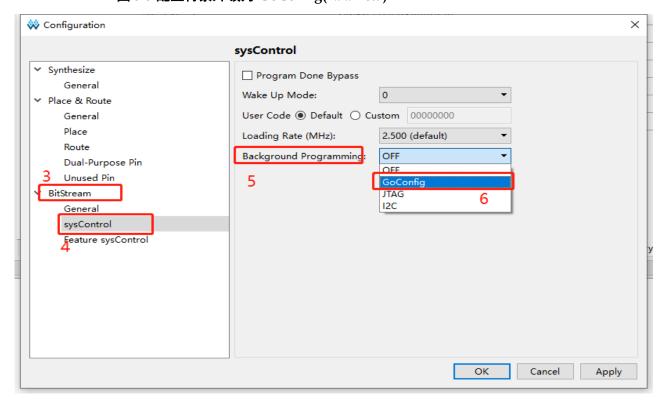

在云源软件(1.9.8.11)中,点击"Project > Configuration > BitStream > Background Programming > GoConfig"如图 5-1、图 5-2 所示。

在云源软件(1.9.9Beta)中,点击"Project > Configuration > BitStream > sysControl > Background Programming > GoConfig"如图 5-1、图 5-3 所示。

#### 图 5-1 打开 Configuration 选项

IPUG1035-1.0 12(20)

**5** 使用说明 **5.1** 软件配置

#### 图 5-2 配置背景升级为 GoConfig(1.9.8.11)

#### 图 5-3 配置背景升级为 GoConfig(1.9.9Beta)

IPUG1035-1.0 13(20)

5 使用说明 5.2 流程说明

## 5.2 流程说明

Gowin goConfig JTAG IP 使用时可分为两个状态:工作状态和空闲状态。

- 工作状态: IP 执行"写 Flash"或"擦 Flash"操作。

- 空闲状态: IP 执行其他操作,或者不执行任何操作。

执行操作:指计划直接通过 JTAG 接口,完成的所有操作。可以执行的操作,可以参考 <u>UG290,《Gowin FPGA产品编程配置手册》</u>的 JTAG 相关章节。

IP 需要通过 "ERASE\_S" 或 "PROG\_S" 指令进入工作状态;通过 "ERASE\_E" 或 "PROG\_E" 退出工作状态。

下文将主要描述工作状态,空闲状态,其他按照 <u>UG290,《Gowin</u> FPGA 产品编程配置手册》JTAG 操作即可。

### 5.2.1 前期准备

IP 的前期准备,用于检验/确保 IP 工作正常。可以按照 <u>UG290,《Gowin FPGA 产品编程配置手册》</u>执行"读取 ID CODE 实例"、"读取 User Code"、"读取 Status Register"三个操作中的一个,或者三个操作都执行。

如果操作结果与预期完全一致,则说明可以开始执行"擦 Flash"。

### 5.2.2 擦 Flash

当确定前期准备正常后,可以开始擦 Flash。"FPGA 擦除 Flash"的详细流程,需参考 <u>UG290,《Gowin FPGA 产品编程配置手册》</u>。IP 可执行的步骤由发送"0x15"、"0x75"开始,一直到"持续产生时钟"完成结束,其他 IP 未进行的操作请参考 <u>UG290,《Gowin FPGA 产品编程配置手册》</u>控制 JTAG 接口完成。针对 IP 实现的过程说明如下:

- 1. JTAG-TCK 与 JTAG-TDI 发送 "ERASE\_S" (0xABCDFE01) 指令

- 2. IP 发送"0x15"、"0x75"

- 3. IP 持续产生时钟,直到用户发送"ERASE\_E"

- 4. JTAG-TCK 与 JTAG-TDI 发送 "ERASE\_E" (0xABCDFE02) 指令

"FPGA 擦除 Flash"的操作完成后,可执行"读取 ID CODE 实例"、 "读取 User Code"、"读取 Status Register"三个操作中的一个,或者三个操作都执行,确认擦除成功。

IPUG1035-1.0 14(20)

5 使用说明 5.3 注意事项

#### 5.2.3 写 Flash

当确定"FPGA 擦除 Flash"正确完成后,可以开始写 Flash 流程。一次写 Flash 一般按照下面的步骤:

- 1. JTAG-TCK 与 JTAG-TDI 发送"PROG\_S"(0xABCDFE03) 指令

- 2. JTAG 接口发送实际数据

- 3. 数据发送完成后, JTAG-TCK 与 JTAG-TDI 发送 "PROG\_E" (0xABCDFE04) 指令

# 5.3 注意事项

Gowin goConfig JTAG IP 在使用时的注意事项如下。

### 5.3.1 IO 约束

如"信号定义"中说明, Gowin goConfig JTAG IP 的 IO 信号可以分为两类:无限制 IO 以及有限制 IO。

- 无限制 IO: 与常规使用相同,可以自由选择名字,是否放置到顶层等。

- 有限制 IO: 限定 IO 名称,且必须通过顶层输入或输出。

注!

云源软件会对此"有限制 IO"进行检测,若选择了背景升级-GoConfig,但 IO 不存在或不对应,软件执行"Place & Route"时会报错。

## 5.3.2 OSC 输出

Gowin goConfig JTAG IP 使用了器件内的 OSC 模块。同时,IP 可以提供 25MHz 的时钟输出,可根据需求选择是否使用。

## 5.3.3 缓存限制

Gowin goConfig JTAG IP 使用了 1 个 BSRAM 进行数据缓存,因此一次传输的数据总量不能超过 1 个 BSRAM。

IPUG1035-1.0 15(20)

# 6界面配置

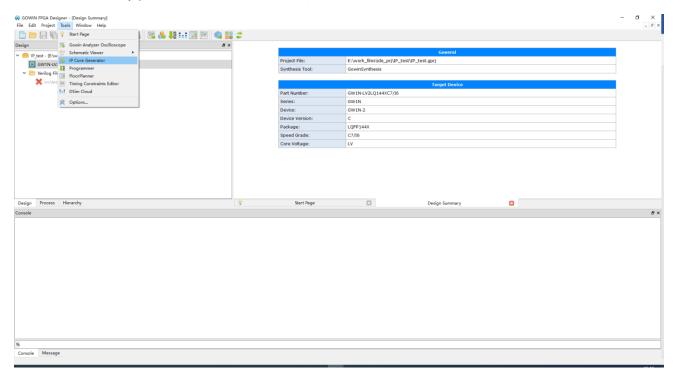

在云源软件界面菜单栏 Tools 下,可启动 IP Core Generator 工具,完成调用并配置 Gowin goConfig JTAG IP。

#### 1. 打开 IP Core Generator

建立工程后,点击左上角"Tools"选项卡,下拉单击"IP Core Generator"选项,就可打开 IP 核产生工具,如图 6-1 所示。

#### 图 6-1 IP Core Generator 选项

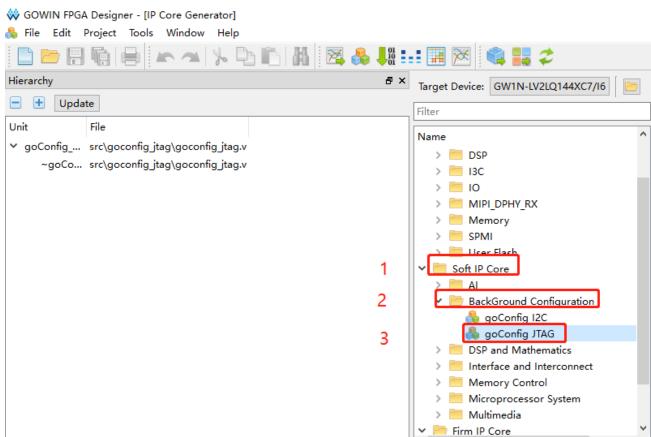

#### 2. 打开 Gowin goConfig JTAG IP 核

选择 "Soft IP Core > BackGround Configuration > goConfig JTAG", 如图 6-2 所示,双击即可打开配置界面。

IPUG1035-1.0 16(20)

Process

Hierarchy

Design

#### 图 6-2 打开 goConfig JTAG IP 核

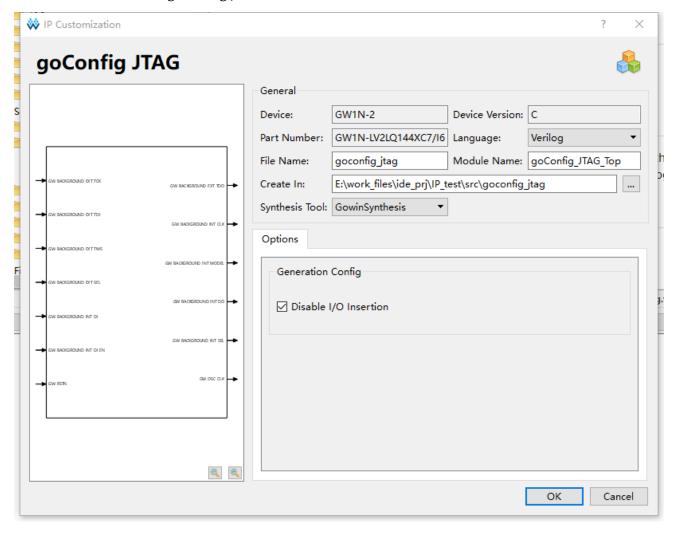

#### 3. Gowin goConfig JTAG IP 核配置界面

Gowin goConfig JTAG IP 核配置界面如图 6-3 所示。配置界面左侧是goConfig JTAG IP 核的接口示意图,右侧为配置选项。

Start Page

- 用户可通过修改 File Name, 配置产生文件名称

- 用户可通过修改 Module Name, 配置产生的顶层模块名称

IPUG1035-1.0 17(20)

### 图 6-3 goConfig JTAG IP 配置界面

IPUG1035-1.0 18(20)

7参考设计 7.1 参考设计

# **7**参考设计

本节主要介绍 Gowin goConfig JTAG IP 参考设计的搭建与使用方法。 详细信息请参见高云半导体官网给出的相关参考设计。

# 7.1 参考设计

### 7.1.1 FPGA 工程说明

Gowin goConfig JTAG IP 的 FPGA 参考设计主要包含两个组成部分 IP 模块以及用户模块。

- IP 模块:调用 IP,并给出了一种使用方法示例。模块说明如下:

- **IP** 的使用需要更改云源软件配置,参考设计中已经包含有对应的示例;详细说明请参考<u>第5章</u>使用说明。

- IP 的部分 IO 使用时存在限制,可模仿参考设计的使用;详细说明请参考第 4 章信号定义以及 5.3 注意事项。

- 用户模块:通过一个简单的 LED 测试,代表用户的设计。

IPUG1035-1.0 19(20)

7参考设计 7.1 参考设计

#### 图 7-1 参考设计-基本结构示意图

## 7.1.2 参考设计文件

Gowin goConfig JTAG IP 参考设计中,文件说明如表 7-1 所示。相关文件如表 7-1 所示。

| 主っ っ | 1 条字沿计 | src 文件夹内容列表      |

|------|--------|------------------|

| 4X / | 1 罗写以1 | 310 人 「一大!」 台グリル |

| 名称                    | 描述              |

|-----------------------|-----------------|

| top.v                 | 顶层模块,包含LED的测试应用 |

| goConfig_JTAG_ref.cst | 工程物理约束文件        |

| goconfig_jtag         | IP文件夹           |

| goconfig_jtag.v       | 生成的IP文件,加密。     |

| goconfig_jtag.vo      | 生成IP的网表文件,仿真使用。 |

# 7.1.3 参考设计注意事项

Gowin goConfig JTAG IP 本次提供的参考设计中,仅包含 FPGA 的工程,以及部分说明文档;不提供仿真环境,以及 JTAG 的驱动示例。

"JTAG 的驱动示例"请联系 FAE 获取。

IPUG1035-1.0 20(20)