# Gowin MIPI DSI/CSI-2 Receiver IP 用户指南

IPUG1036-1.0,2023-09-28

### 版权所有 © 2023 广东高云半导体科技股份有限公司

**GO**₩IN高云、₩、Gowin、GowinSynthesis、云源以及高云均为广东高云半导体科技股份有限公司注册商标,本手册中提到的其他任何商标,其所有权利属其拥有者所有。未经本公司书面许可,任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部,并不得以任何形式传播。

### 免责声明

本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止反言或其它方式授予任何知识产权许可。除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。高云半导体不承诺对这些文档进行适时的更新。

### 版本信息

| 日期         | 版本  | 说明    |

|------------|-----|-------|

| 2023/09/28 | 1.0 | 初始版本。 |

i

# 目录

| 目 | 录…  |         | . <b>i</b> |

|---|-----|---------|------------|

| 图 | 目录  |         | ii         |

| 表 | 目录  | ;i      | ii         |

| 1 | 关于  | 本手册     | 1          |

|   | 1.1 | 手册内容    | 1          |

|   | 1.2 | 相关文档    | 1          |

|   | 1.3 | 术语与缩略语  | 2          |

|   | 1.4 | 技术支持与反馈 | 2          |

| 2 | 产品  | 概述      | 3          |

|   | 2.1 | 产品概述    | 3          |

|   | 2.2 | 主要特征    | 3          |

|   | 2.3 | 资源占用    | 4          |

| 3 | 功能  | 描述      | 5          |

|   | 3.1 | 顶层框图    | 5          |

|   | 3.2 | 端口介绍    | 6          |

|   | 3.3 | 时序说明    | 7          |

|   | 3.4 | 配置参数    | 9          |

| 4 | 界面  | 配置1     | 0          |

# 图目录

| 图 3-1 Gowin MIPI DSI/CSI-2 Receiver IP 项层框图 | 5  |

|---------------------------------------------|----|

| 图 3-2 输出时序图                                 | 7  |

| 图 3-3 O_PAYLOAD_DV 时序例图                     | 8  |

| 图 3-4 两套包信息输出时序例图                           | 8  |

| 图 4-1 IP Core Generator 工具                  | 10 |

| 图 4-2 MIPI DSI/CSI-2 Receiver IP 配置界面       | 11 |

| 图 4-3 MIPI DSI/CSI-2 Receiver IP 例化         | 11 |

IPUG1036-1.0 ii

# 表目录

| 表 1-1 术语与缩略语                                       | 2 |

|----------------------------------------------------|---|

| 表 2-1 Gowin MIPI DSI/CSI-2 Receiver IP 概述          | 3 |

| 表 2-2 基于 GW2A-18 的 MIPI DSI/CSI-2 Receiver IP 资源占用 | 4 |

| 表 3-1 Gowin MIPI DSI/CSI-2 Receiver IP 端口列表        | 6 |

| 表 3-2 Gowin DSI/CSI-2 Receiver IP 参数               | 9 |

IPUG1036-1.0 iii

1 关于本手册 1.1 手册内容

## 1.1 手册内容

Gowin<sup>®</sup> MIPI DSI/CSI-2 Receiver IP 用户指南主要内容包括产品概述、功能描述、界面配置等,旨在用于帮助用户快速了解 Gowin MIPI DSI/CSI-2 Receiver IP 的产品特性、特点及使用方法

## 1.2 相关文档

- 1. 通过登录高云®半导体网站 <u>www.gowinsemi.com</u> 可以下载、查看以下相关文档:

- IPUG948, Gowin MIPI D-PHY RX TX Advance IP 用户指南

- <u>DS100, GW1N 系列 FPGA 产品数据手册</u>

- DS102, GW2A 系列 FPGA 产品数据手册

- DS226, GW2AR 系列 FPGA 产品数据手册

- DS961, GW2ANR 系列 FPGA 产品数据手册

- DS976, GW2AN-55 器件数据手册

- SUG100, Gowin 云源软件用户指南

- MIPI Alliance Specification for D-PHY, Version 1.1 November 7, 2011, www.mipi.org

- 3. MIPI Alliance Specification for Display Serial Interface, Version 1.1 November 22, 2011, <a href="https://www.mipi.org">www.mipi.org</a>

- 4. MIPI Alliance Specification for Camera Serial Interface 2 (CSI-2), Version 1.1, July 18, 2012, <a href="https://www.mipi.org">www.mipi.org</a>

IPUG1036-1.0 1(11)

1 关于本手册 1.3 术语与缩略语

# 1.3 术语与缩略语

本手册中出现的相关术语、缩略语及相关释义如表 1-1 所示。

### 表 1-1 术语与缩略语

| 术语与缩略语 | 全称                                  | 含义        |

|--------|-------------------------------------|-----------|

| CSI    | Camera Serial Interface             | 串行摄像头接口   |

| DSI    | Display Serial Interface            | 串行显示接口    |

| ECC    | Error Correction Code               | 纠错码       |

| EoTP   | End of Transmission Packet          | 传输结束包     |

| IP     | Intellectual Property               | 知识产权      |

| LUT    | Look-up Table                       | 查找表       |

| MIPI   | Mobile Industry Processor Interface | 移动行业处理器接口 |

| NC     | No Connect                          | 不连接       |

| WC     | Word Count                          | 负载字节数     |

## 1.4 技术支持与反馈

高云半导体提供全方位技术支持,在使用过程中如有任何疑问或建议,可直接与公司联系:

网址: www.gowinsemi.com.cn

E-mail: support@gowinsemi.com

Tel: +86 755 8262 0391

IPUG1036-1.0 2(11)

2产品概述 2.1产品概述

# 2产品概述

## 2.1 产品概述

Gowin MIPI DSI/CSI-2 Receiver IP 用于从 Gowin MIPI D-PHY RX Advance IP 输出的、经过通道对齐处理后的 MIPI 字节数据流中解析分离出包头(Packet Header)信息和负载数据。包头信息包括: ECC,Data Type 和 Word Count 三部分。

### 表 2-1 Gowin MIPI DSI/CSI-2 Receiver IP 概述

| Gowin MIPI DSI/CSI-2 Receiver IP |                                  |  |

|----------------------------------|----------------------------------|--|

| 逻辑资源                             | 参见表2-2                           |  |

| 交付文件                             |                                  |  |

| 设计文件                             | Verilog(encrypted)               |  |

| 参考设计                             | Verilog                          |  |

| TestBench                        | Verilog                          |  |

| 测试设计流程                           |                                  |  |

| 综合软件                             | GowinSynthesis <sup>®</sup>      |  |

| 应用软件                             | Gowin Software(V1.9.9.Beta-3及以上) |  |

#### 注!

可登录高云半导体网站查看芯片支持信息。

## 2.2 主要特征

- 符合 MIPI DSI V1.1 和 MIPI CSI-2 V1.1 标准

- 支持 1、2、3 或 4 数据通道的 MIPI D-PHY RX 输入

- 支持 1:8 或 1:16 两种数据组织模式的 MIPI D-PHY RX 输入

- 支持 MIPI CSI-2 标准中定义的四种同步短包类型

- 支持 MIPI CSI-2 标准中定义的数据长包类型

IPUG1036-1.0 3(11)

2 产品概述 2.3 资源占用

- 支持 MIPI DSI 标准中定义的四种同步短包类型

- 支持 MIPI DSI 标准中定义的数据长包类型

- 支持 MIPI DSI 标准中定义的 EoTP 短包类型

- 支持 MIPI DSI 标准中定义的三种视频模式

- Non-burst mode with sync pulses

- Non-burst mode with sync events

- Burst mode

## 2.3 资源占用

以高云 GW2A-18 为例,Gowin MIPI DSI/CSI-2 Receiver IP 资源占用情况如表 2-2 所示。实际应用中,因使用的器件密度、速度等级的不同,实际的资源占用情况会有所不同。

表 2-2 基于 GW2A-18 的 MIPI DSI/CSI-2 Receiver IP 资源占用

| 参数配置         | 资源占用 |      |

|--------------|------|------|

| <b>多</b> 奴癿且 | LUTs | REGs |

| 1:8, 1-Lane  | 150  | 149  |

| 1:8, 2-Lane  | 199  | 175  |

| 1:8, 3-Lane  | 244  | 201  |

| 1:8, 4-Lane  | 278  | 227  |

| 1:16, 1-Lane | 218  | 184  |

| 1:16, 2-Lane | 310  | 244  |

| 1:16, 3-Lane | 1052 | 630  |

| 1:16, 4-Lane | 1328 | 722  |

IPUG1036-1.0 4(11)

3 功能描述 3.1 顶层框图

# 3功能描述

## 3.1 顶层框图

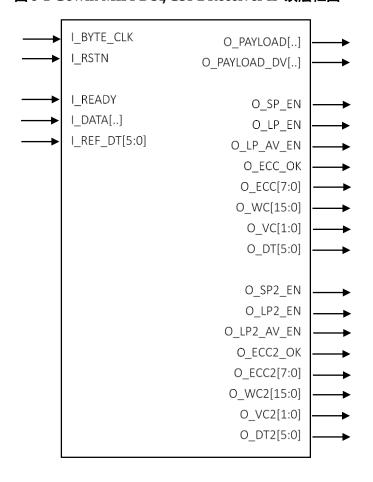

图 3-1 Gowin MIPI DSI/CSI-2 Receiver IP 顶层框图

Gowin MIPI DSI/CSI-2 Receiver IP 的基本功能是从 D-PHY 字节数据 流中解析分离出控制信号(包头,Packet Header)和负载数据。3-Lane 或 4-Lane 在 1:16 的数据组织模式下,一个时钟周期可能解析出两套控制信号,所以输出端口包含了第二套控制信号,其他情况,第二套控制信号不会引出。

IPUG1036-1.0 5(11)

3.2 端口介绍

# 3.2 端口介绍

表 3-1 Gowin MIPI DSI/CSI-2 Receiver IP 端口列表

| 信号             | 方向     | 描述                                                                                       |               |           |

|----------------|--------|------------------------------------------------------------------------------------------|---------------|-----------|

| I_BYTE_CLK     | Input  | 工作时钟                                                                                     |               |           |

| I_RSTN         | Input  | 异步复位信号,低电平有效                                                                             |               |           |

| I_READY        | Input  | Gowin MIPI D-PHY RX Advance IP输出的并行数据<br>对齐标识信号                                          |               |           |

| I_DATA0[]      | Input  | #n通道的并行数据                                                                                | 握. 0 < n < 3. |           |

| I_DATA1[]      | Input  |                                                                                          |               | 时, 位宽为8:  |

| I_DATA2[]      | Input  | 当"MIPI D-PHY RX Mode"为1:8时,位宽为8;<br>1:16时,位宽为16;                                         |               |           |

| I_DATA3[]      | Input  | 当 "Number of F                                                                           | RX Lanes"为4时, | I_DATA0~  |

| I_DATAS[]      | input  | I_DATA3端口都存在;为3时,只存在I_DATA0~<br>I_DATA2端口;为2时,只存在I_DATA0、I_DATA1<br>端口;为1时,只存在I_DATA0端口。 |               |           |

| I_REF_DT[5:0]  | Input  | 参考数据类型                                                                                   |               |           |

| O_PAYLOAD[]    | Output | 负载数据,位宽视D-PHY通道数和模式(1:8/1:16)<br>而定                                                      |               |           |

|                |        | 通道数                                                                                      | 1:8模式位宽       | 1: 16模式位宽 |

|                |        | 1                                                                                        | 8             | 16        |

|                |        | 2                                                                                        | 16            | 32        |

|                |        | 3                                                                                        | 24            | 48        |

|                |        | 4                                                                                        | 32            | 64        |

| O_PAYLOAD_DV[] | Output | 负载数据,字节有效标识,位宽为O_PAYLOAD[]<br>位宽除以8                                                      |               |           |

| O_SP_EN        | Output |                                                                                          |               |           |

| O_LP_EN        | Output | 长包标识,高电 <sup>3</sup>                                                                     | 平有效           |           |

| O_LP_AV_EN     | Output | 数据类型匹配标识,高电平有效;指示当前数据类型与参考数据类型(I_REF_DT)一致                                               |               |           |

| O_VC[1:0]      | Output | 虚通道ID,对应包头(Packet Header)中的<br>Byte0[7:6]                                                |               |           |

| O_DT[5:0]      | Output | 数据类型,对应包头(Packet Header)中的<br>Byte0[5:0]                                                 |               |           |

| O_WC[15:0]     | Output | 负载字节数,对应包头(Packet Header)中的<br>Byte1和Byte2                                               |               |           |

| O_ECC[7:0]     | Output | 纠错码,对应包头(Packet Header)中的Byte3                                                           |               |           |

| O_ECC_OK       | Output | ECC校验通过标识,高电平有效                                                                          |               |           |

IPUG1036-1.0 6(11)

3 功能描述 3.3 时序说明

| 信号          | 方向     | 描述                 |  |

|-------------|--------|--------------------|--|

| O_SP2_EN    | Output | 第二套短包标识,高电平有效      |  |

| O_LP2_EN    | Output | 第二套长包标识,高电平有效      |  |

| O_LP2_AV_EN | Output | 第二套数据类型匹配标识,高电平有效  |  |

| O_VC2[1:0]  | Output | 第二套虚通道ID           |  |

| O_DT2[5:0]  | Output | 第二套数据类型            |  |

| O_WC2[15:0] | Output | 第二套负载字节数           |  |

| O_ECC2[7:0] | Output | 第二套纠错码             |  |

| O_ECC2_OK   | Output | 第二套ECC校验通过标识,高电平有效 |  |

### 3.3 时序说明

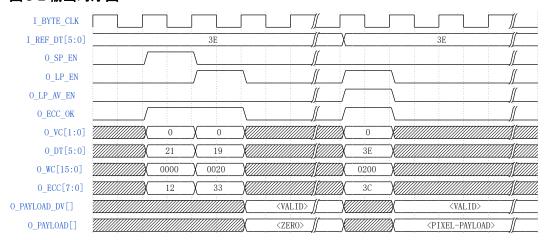

### 图 3-2 输出时序图

当解析到有效的数据类型时,O\_SP\_EN 或 O\_LP\_EN 会被置起,同时输出包头的完整信息: 虚通道 ID(Virtual Channel ID)、数据类型(Data Type)、负载字节数(Word Count)和纠错码(ECC)。

仅当解析出的长包的数据类型与输入的参考数据类型

(I\_REF\_DT[5:0])一致时,O\_LP\_AV\_EN 会被置起,目的是为了将指定的视频负载数据与其他长包数据,如空数据、消影数据等区分开。如果解析出了与参考数据类型不一致的视频负载数据类型,O\_LP\_AV\_EN 同样不会被置起。

当使用解析出的包头信息的{O\_WC, O\_VC, O\_DT}部分计算所得纠错码与解析出的 O\_ECC 一致时,O\_ECC\_OK 会被置起。暂不支持对包头做纠错处理。

IPUG1036-1.0 7(11)

**3** 功能描述 **3.3** 时序说明

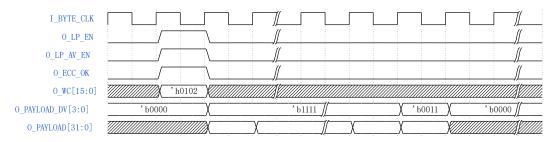

### 图 3-3 O\_PAYLOAD\_DV 时序例图

O\_PAYLOAD\_DV 输出负载数据字节有效标识,每一位对应 O\_PAYLOAD 的每一字节。O\_PAYLOAD 总是向前对齐。除了负载数据有效的最后一个周期外,O\_PAYLOAD\_DV 的所有位必须全为'1';最后一个周期,允许出现高位为连续'0',低位为连续'1',或全为'1'。如图 3-3 所示,负载字节数为'h0102,最后一周期将剩 2 字节,此时 O\_PAYLOAD\_DV为'b0011,标识 O\_PAYLOAD 低位 2 字节为有效。

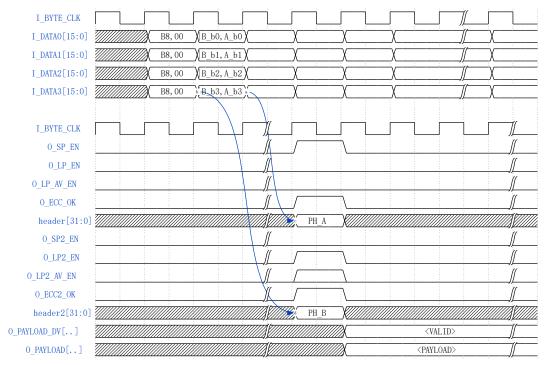

### 图 3-4 两套包信息输出时序例图

$\label{eq:condition} \\ \text{header}[31:0] = \{0\_\texttt{ECC}, \ 0\_\texttt{WC}, \ 0\_\texttt{VC}, \ 0\_\texttt{DT}\}, \ \\ \text{header}[2]:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{DT2}\} \\ \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{DT2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{DT2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{DT2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{DT2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{DT2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{DT2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{DT2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{DT2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{DT2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{DT2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{DT2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{DT2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{DT2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{DT2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{DT2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{DT2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{DT2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{VC2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{VC2}\} \\ \text{header}[31:0] = \{0\_\texttt{ECC2}, \ 0\_\texttt{WC2}, \ 0\_\texttt{VC2}, \ 0\_\texttt{VC2}$

当配置成输入字节数据大于 4 字节(3-Lane/4-Lane@1:16)的 DSI 模式时,图 3-1 顶层框图中的 O\_SP2\_EN 等第二套包头信息信号,才会有效。如图 3-4 所示,在 4-Lane,1:16 的配置条件下,同时输出了两套包头信息 PH A 与 PH B。不会单独出现第二套包头信息有效的情况。

包头信息输出有效与输入的数据的间隔不是固定的,与通道数目及数据组织方式有关。

IPUG1036-1.0 8(11)

3 功能描述 3.4 配置参数

# 3.4 配置参数

### 表 3-2 Gowin DSI/CSI-2 Receiver IP 参数

| 参数名称                | 允许范围      | 描述                |

|---------------------|-----------|-------------------|

| MIPI Interface Type | DSI/CSI-2 | 指定MIPI接口类型        |

| MIPI D-PHY RX Mode  | 1:8或1:16  | 指定D-PHY RX的数据组织模式 |

| Number of RX Lanes  | 1,2,3或4   | 指定D-PHY RX的通道数    |

IPUG1036-1.0 9(11)

# **4** 果面配置

用户可通过高云®半导体云源软件界面的"Tools"菜单启动 IP Core Generator 工具,完成调用并配置 MIPI DSI/CSI-2 Receiver IP。

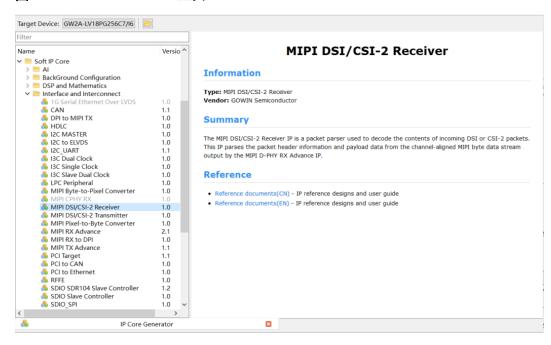

### 1. 打开 IP Core Generator

用户建立工程后,单击"Tools"菜单栏,单击下拉列表中的"IP Core Generator"选项,即可打开 IP Core Generator 工具界面。点击"Soft IP Core > Interface and Interconnect > MIPI DSI/CSI-2 Receiver",在"Filter"栏中输入"DSI/CSI-2 Receiver",可快速定位。

### 图 4-1 IP Core Generator 工具

IPUG1036-1.0 10(11)

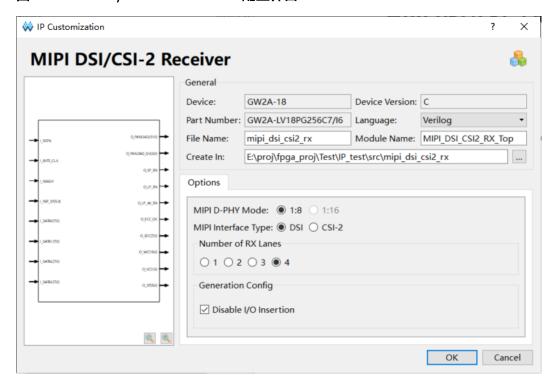

### 2. MIPI DSI/CSI-2 Receiver IP 配置界面

用户在"IP Core Generator"工具界面双击"MIPI DSI/CSI-2 Receiver"项,即可打开 MIPI DSI/CSI-2 Receiver IP 配置界面。界面左侧是接口示意图,右侧是 IP 的配置参数选项(参见 <u>3.4 配置参数</u>),如图 4-2 所示。

### 图 4-2 MIPI DSI/CSI-2 Receiver IP 配置界面

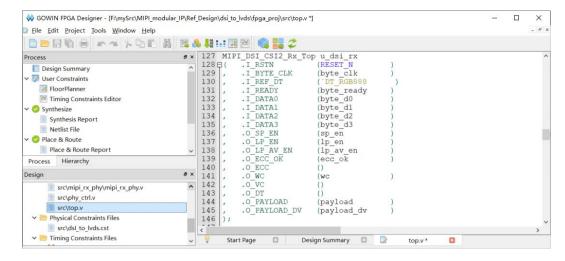

### 3. 生成与例化

根据工程实际需求配置好各参数后,单击"OK"按钮,即可生成 MIPI DSI/CSI-2 Receiver IP。如图 4-3 所示,是在用户 Verilog 程序中 IP 例化的例子。

### 图 4-3 MIPI DSI/CSI-2 Receiver IP 例化

IPUG1036-1.0 11(11)