# Gowin DC-SCM LTPI IP 用户指南

IPUG1086-1.0,2024-02-08

### 版权所有 © 2024 广东高云半导体科技股份有限公司

**GO◇◆IN高云**, **◇◆**, Gowin以及高云均为广东高云半导体科技股份有限公司注册商标, 本手册中提到的其他任何商标, 其所有权利属其拥有者所有。未经本公司书面许可, 任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部, 并不得以任何形式传播。

### 免责声明

本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止反言或其它方式授予任何知识产权许可。除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。高云半导体不承诺对这些文档进行适时的更新。

### 版本信息

| 日期         | 版本  | 说明    |

|------------|-----|-------|

| 2024/02/08 | 1.0 | 初始版本。 |

i

# 目录

| 目 | 录                        | i     |

|---|--------------------------|-------|

| 图 | ]目录                      | . iii |

| 表 | 是目录                      | . iv  |

| 1 | 关于本手册                    | 1     |

|   | 1.1 手册内容                 |       |

|   | 1.2 相关文档                 |       |

|   | 1.3 术语、缩略语               | 1     |

|   | 1.4 技术支持与反馈              | 2     |

| 2 | 功能简介                     | 3     |

|   | 2.1 概述                   |       |

|   | 2.2 主要特征                 | 4     |

|   | 2.3 资源利用                 |       |

| 3 | 功能描述                     | 5     |

|   | 3.1 系统框图                 |       |

|   | 3.1.1 DC-SCM 2.0 LTPI 结构 | 5     |

|   | 3.1.2 IP 实现框图            | 6     |

|   | 3.2 端口列表                 | 8     |

|   | 3.3 接口时序                 | . 11  |

|   | 3.3.1 配置接口时序             | . 11  |

|   | 3.3.2 数据接口时序             | . 11  |

|   | 3.3.3 GPIO 接口时序          | . 11  |

|   | 3.3.4 UART 接口时序          | . 11  |

|   | 3.3.5 IIC/SMBus 接口时序     | . 11  |

|   | 3.4 寄存器描述                | . 12  |

| 4 | 设计说明                     | 17    |

|   | 4.1 线速率                  | . 17  |

|   | 4.2 时钟                   | . 17  |

|   | 4.2.1 系统时钟               | . 17  |

|   | 4.2.2 参考时钟          | 17 |

|---|---------------------|----|

|   | 4.2.3 配置时钟(cfg clk) | 17 |

|   | 4.2.4 LVDS 时钟       | 17 |

|   | 4.2.5 RX/TX DIV5 时钟 | 17 |

|   | 4.2.6 时钟结构          | 18 |

|   | 4.3 外部通道接口处理        | 18 |

|   | 4.3.1 GPIO 通道       | 19 |

|   | 4.3.2 UART 通道       | 20 |

|   | 4.3.3 IIC/SMBus 通道  | 21 |

|   | 4.3.4 OEM 通道        | 25 |

|   | 4.3.5 数据通道          | 25 |

|   | 4.4 LTPI 帧格式        | 26 |

|   | 4.4.1 帧格式           | 26 |

|   | 4.4.2 具体帧定义         | 27 |

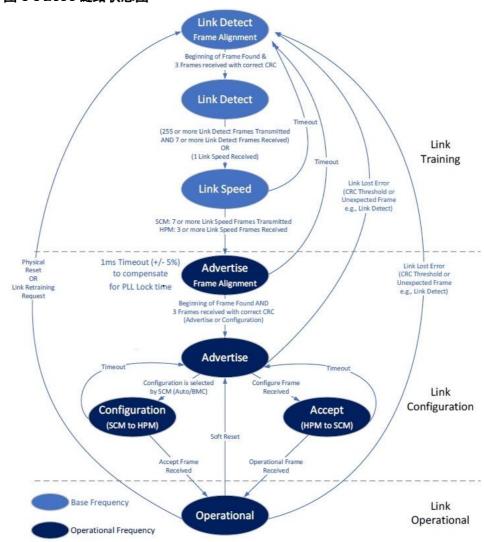

|   | 4.5 链路初始化以及运行流程     | 31 |

|   | 4.5.1 状态图           | 31 |

|   | 4.5.2 链路训练          | 32 |

|   | 4.5.3 链路配置          | 33 |

|   | 4.5.4 链路运行          | 34 |

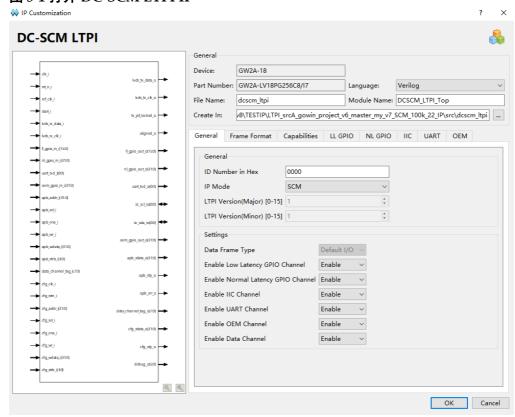

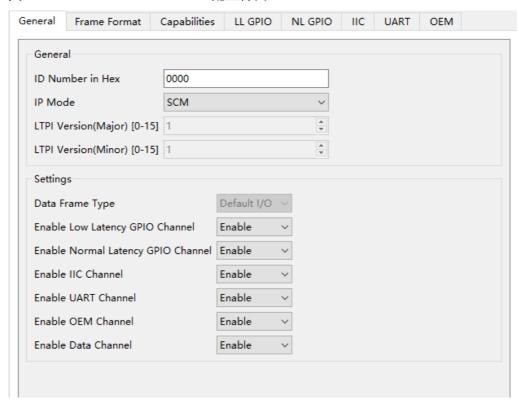

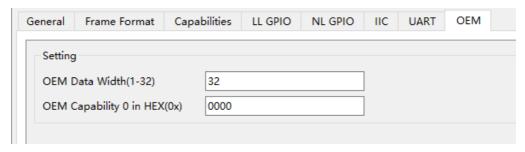

| 5 | 界面配置                | 35 |

| 3 | 参考设计                | 40 |

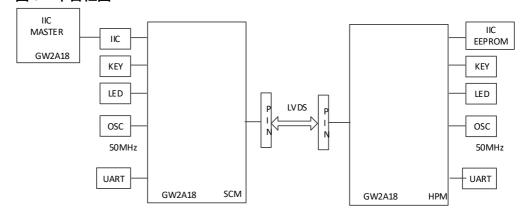

|   | 6.1 应用              | 40 |

|   | 6.2 参考设计            | 40 |

|   | 6.2.1 硬件平台          | 40 |

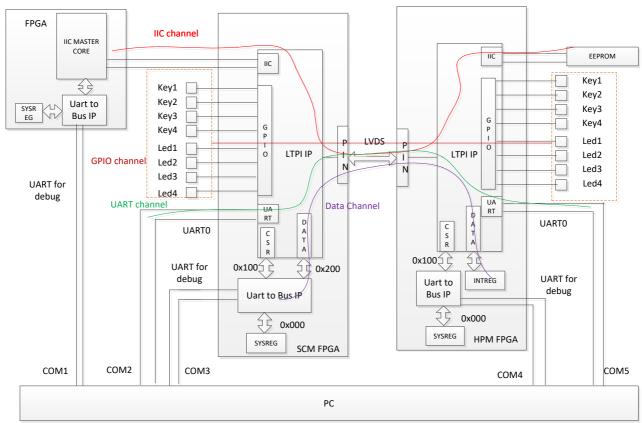

|   | 6.2.2 实现框图          | 41 |

|   | 6.2.3 总线协议与地址规划     | 42 |

|   | 6.3 板级测试            | 43 |

|   | 6.3.1 操作说明          | 43 |

|   | 6.3.2 操作步骤          | 43 |

| 7 | 文件交付                | 46 |

|   | 7.1 文档              |    |

|   | 7.2 设计源代码(加密)       |    |

|   | 7.3 参考设计            |    |

# 图目录

| 冬 | 3-1 LTPI 结构图                    | 5    |

|---|---------------------------------|------|

| 图 | 3-2 LTPI 各个通道传输示意图              | . 6  |

| 图 | 3-3 DC-SCM LTPI IP 实现框图         | . 6  |

| 图 | 3-4 Gowin DC-SCM LTPI IP 端口示意图  | . 8  |

| 图 | 3-5 配置接口写时序图                    | . 11 |

| 图 | 3-6 配置接口读时序图                    | . 11 |

| 图 | 4-1 典型时钟方案                      | . 18 |

| 图 | 4-2 UART 采样与恢复示意图               | . 20 |

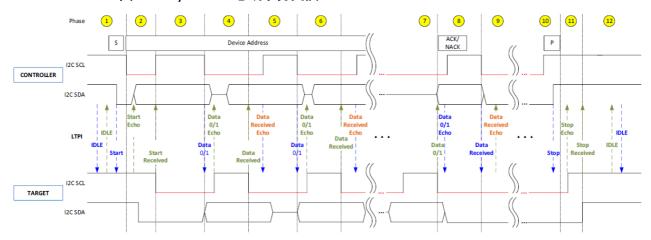

| 图 | 4-3 IIC 总线事务交换                  | . 22 |

| 图 | 4-4 LTPI 链路状态图                  | . 31 |

| 图 | 5-1 打开 DC-SCM LTPI IP           | . 35 |

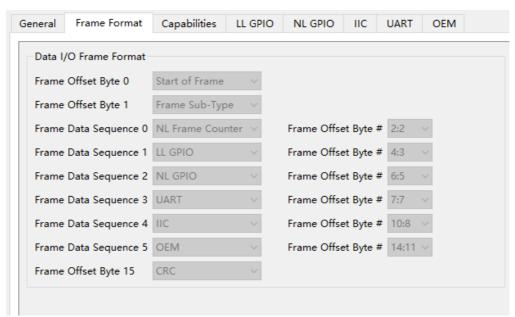

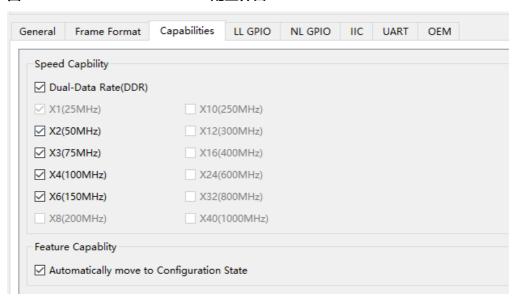

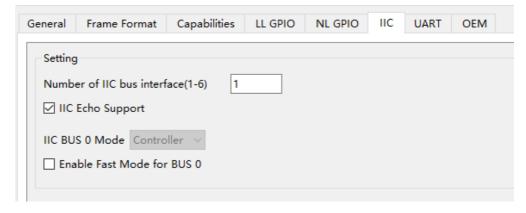

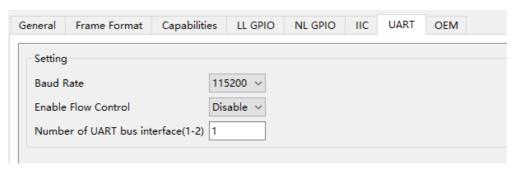

| 图 | 5-2 Gowin DC-SCM LTPI IP 配置界面 1 | . 36 |

| 图 | 5-3 Gowin DC-SCM LTPI IP 配置界面 2 | . 37 |

| 图 | 5-4 Gowin DC-SCM LTPI IP 配置界面 3 | . 37 |

| 图 | 5-5 Gowin DC-SCM LTPI IP 配置界面 4 | . 38 |

| 图 | 5-6 Gowin DC-SCM LTPI IP 配置界面 5 | . 38 |

| 图 | 5-7 Gowin DC-SCM LTPI IP 配置界面 6 | . 38 |

| 图 | 5-8 Gowin DC-SCM LTPI IP 配置界面 7 | . 39 |

| 图 | 5-9 Gowin DC-SCM LTPI IP 配置界面 8 | . 39 |

| 图 | 6-1 HPM 和 SCM 的连接               | . 40 |

| 图 | 6-2 平台框图                        | . 40 |

| 图 | 6-3 参考设计实现框图                    | . 41 |

# 表目录

| 表 1-1 术语、缩略语                    | 1  |

|---------------------------------|----|

| 表 2-1 Gowin DC-SCM LTPI IP 概述   | 3  |

| 表 2-2 Gowin DC-SCM LTPI IP 占用资源 | 4  |

| 表 3-1 端口定义                      | 9  |

| 表 3-2 Gowin DC-SCM LTPI IP 寄存器  | 12 |

| 表 3-3 速度描述                      | 15 |

| 表 3-4 通告帧能力描述                   | 15 |

| 表 3-5 串口通道最大波特率定义表              | 16 |

| 表 4-1 外部通道接口处理                  | 18 |

| 表 4-2 GPIO 字段配置                 | 19 |

| 表 4-3 UART 字段配置                 | 21 |

| 表 4-4 IIC/SMBus 通道事务定义          | 21 |

| 表 4-5 IIC/SMBus 字段配置            | 22 |

| 表 4-6 IIC/SMBus 事务流程            | 23 |

| 表 4-7 数据通道事务定义                  | 25 |

| 表 4-8 数据通道字段配置                  | 25 |

| 表 4-9 帧格式说明                     | 26 |

| 表 4-10 链路训练阶段帧类型                | 27 |

| 表 4-11 Link Detect 帧定义          | 27 |

| 表 4-12 Link Speed 帧定义           | 27 |

| 表 4-13 链路配置阶段帧类型                | 28 |

| 表 4-14 Advertise 帧定义            | 28 |

| 表 4-15 Configure 帧定义            | 28 |

| 表 4-16 Accept 帧定义               | 29 |

| 表 4-17 运行阶段帧类型                  | 30 |

| 表 4-18 Default I/O 帧定义          | 30 |

| 表 4-19 Default Data 帧定义         | 31 |

| 表 6-1 KEY 和 LED 的映射路线表          | 42 |

| 表 6-2 寄存器地址定义                   | 42 |

| 表 7-1 文档列表                                   | 46 |

|----------------------------------------------|----|

| 表 7-2 Gowin DC-SCM LTPI IP 设计源代码列表           | 46 |

| 表 7-3 Gowin DC-SCM LTPI IP RefDesign 文件夹内容列表 | 46 |

IPUG1086-1.0 v

1 关于本手册 1.1 手册内容

### 1.1 手册内容

Gowin® DC-SCM LTPI IP 用户指南主要包括功能简介、功能描述、GUI 调用参考设计等,旨在帮助用户快速了解 Gowin DC-SCM LTPI IP 的产品特性、特点及使用方法。本手册中的软件界面截图参考的是 1.9.9.01 (64-bit) 版本,因软件版本升级,部分信息可能会略有差异,具体以用户软件版本的信息为准。

### 1.2 相关文档

通过登录高云<sup>®</sup>半导体网站 <u>www.gowinsemi.com.cn</u> 可以下载、查看 FPGA 产品相关文档:

- SUG100, Gowin 云源软件用户指南

- DS961, GW2ANR 系列 FPGA 产品数据手册

- DS102, GW2A 系列 FPGA 产品数据手册

- DS226, GW2AR 系列 FPGA 产品数据手册

- DS971, GW2AN-18X & 9X 器件数据手册

- DS976, GW2AN-55 器件数据手册

### 1.3 术语、缩略语

本手册中出现的相关术语、缩略语及相关释义如表 1-1 所示。

### 表 1-1 术语、缩略语

| 术语、缩略语 | 全称                                        | 含义            |

|--------|-------------------------------------------|---------------|

| APB    | Advanced Peripheral Bus                   | 外围总线          |

| CRC    | Cycle Redundancy Check                    | 循环冗余检查        |

| CSR    | Control and Status Register               | 控制和状态寄存器      |

| DC-SCI | Datacenter-ready Secure Control Interface | 数据中心就绪的安全控制接口 |

| DC-SCM | Datacenter-ready Secure Control Module    | 数据中心就绪的安全控制模块 |

IPUG1086-1.0 1(46)

1.4 技术支持与反馈

| 术语、缩略语 | 全称                                             | 含义           |

|--------|------------------------------------------------|--------------|

| FPGA   | Field Programmable Gate Array                  | 现场可编程门阵列     |

| GPIO   | Gowin Programmable I/O                         | Gowin可编程通用管脚 |

| HPM    | Host Processor Module                          | 主机处理器模块      |

| IIC    | Inter-Integrated Circuit                       | 内部集成电路       |

| IP     | Intellectual Property                          | 知识产权         |

| LPTI   | LVDS Tunneling Protocol and Interface          | LVDS隧道协议和接口  |

| LVDS   | Low Voltage Differential Signaling             | 低压差分信号       |

| MCSI   | Multi-Channel Serial Interface                 | 多通道串行接口      |

| OEM    | Original Equipment Manufacturer                | 原始设备制造商      |

| SCM    | Secure Control Module                          | 安全控制模块       |

| SerDes | Serializer/Deserializer                        | 串行器和解串器      |

| SMBus  | System Management Bus                          | 系统管理总线       |

| TDM    | Time Division Multiplexing                     | 时分复用         |

| UART   | Universal Asynchronous<br>Receiver/Transmitter | 通用异步接收器/发送器  |

## 1.4 技术支持与反馈

高云半导体提供全方位技术支持,在使用过程中如有任何疑问或建议,可直接与公司联系:

网址: www.gowinsemi.com.cn

E-mail: support@gowinsemi.com

Tel: +86 755 8262 0391

IPUG1086-1.0 2(46)

2 功能简介 2.1 概述

# 2 功能简介

### 2.1 概述

LTPI (LVDS Tunneling Protocol & Interface, LVDS 隧道协议和接口)是一种协议和接口,设计用于在主机处理器模块(Host Processor Module,HPM)和安全控制模块(Secure Control Module,SCM)之间传输各种低速信号。它不仅支持 GPIO 的隧道传输,还支持 IIC、UART 等低速串行接口的隧道传输。它还可以通过额外的专有 OEM 接口进行扩展,并为 HPM FPGA和 SCM FPGA之间的原始数据隧道提供支持。Gowin DC-SCM LTPI IP 符合数据中心就绪安全控制模块 DC-SCM 2.0 LTPI 规范,并具有标准化的数据中心就绪安全控制接口(DC-SCI),聚合多个数据通道,例如 IIC/SMBbus、GPIO和 UART,为客户的系统和电路板设计增加更多灵活性。

### 表 2-1 Gowin DC-SCM LTPI IP 概述

| Gowin DC-SCM LTPI IP |                                   |  |  |

|----------------------|-----------------------------------|--|--|

| 逻辑资源                 | 参见表 2-2                           |  |  |

| 交付文件                 | 交付文件                              |  |  |

| 设计文件                 | Verilog(encrypted)                |  |  |

| 参考设计                 | Verilog                           |  |  |

| TestBench            | Verilog                           |  |  |

| 测试设计流程               | 测试设计流程                            |  |  |

| 综合软件                 | GowinSynthesis®                   |  |  |

| 应用软件                 | Gowin Software(V1.9.9.Beta-1 及以上) |  |  |

### 注!

可登录高云半导体网站查看芯片支持信息。

IPUG1086-1.0 3(46)

### 2.2 主要特征

- 符合 DC-SCM2.0 协议规范

- 链路初始化、发现和协商

- 支持多通道串行接口

- 支持 GPIO、IIC/SMBus、UART、OEM 和数据通道聚合

- 一共支持多达 5 个通道的聚合/分解

- 支持多达 1023 个正常延迟 GPIO

- IIC/SMBus 的每个通道都可以选择切换 Controller 或者 Target

- OEM 通道扩展为类似低延迟 GPIO 接口

- 支持 AMBA 3 APB 协议 v1.0,用于软 IP 和数据通道的寄存器访问

- 支持 PREADY, 指示 APB 传输完成的就绪信号

- PSLVERR 仅在与数据通道相关的访问中受支持(传输失败的错误指示信号)

- 在 GW2A 器件上支持 LVDS 数据速率最高为 300Mbps (暂定)。

### 2.3 资源利用

通过 Verilog 语言实现 DC-SCM LTPI IP。因使用器件的密度、速度和等级不同,其性能和资源利用情况可能不同。以高云 GW2A 系列 FPGA 为例,DC-SCM LTPI IP 资源利用情况如表 2-2 所示。

表 2-2 Gowin DC-SCM LTPI IP 占用资源

| 配置                | 占用资源     |      |     |       |       |     |

|-------------------|----------|------|-----|-------|-------|-----|

| 用山里。              | Register | LUT  | ALU | BSRAM | SSRAM | PLL |

| 配置为 SCM           |          |      |     |       |       |     |

| 使能 GPIO、IIC、UART、 |          |      |     |       |       |     |

| OEM、Data 通道       |          |      |     |       |       |     |

| LLGPIO 设置为 16     | 2535     | 2708 | 581 | 0     | 0     | 1   |

| NLGPIO 设置为 32     |          |      |     |       |       |     |

| UART接口设置为1        |          |      |     |       |       |     |

| IIC接口设置为1         |          |      |     |       |       |     |

| OEM GPIO 设置为 32   |          |      |     |       |       |     |

| 配置为 HPM           |          |      |     |       |       |     |

| 使能 GPIO、IIC、UART、 |          |      |     |       |       |     |

| OEM、Data 通道       |          |      |     |       |       |     |

| LLGPIO 设置为 16     | 0044     | 0704 | 500 | _     | 4     | ,   |

| NLGPIO 设置为 32     | 2611     | 2794 | 596 | 0     | 1     | 1   |

| UART接口设置为1        |          |      |     |       |       |     |

| IIC接口设置为1         |          |      |     |       |       |     |

| OEM GPIO 设置为 32   |          |      |     |       |       |     |

IPUG1086-1.0 4(46)

3 功能描述 3.1 系统框图

# 3功能描述

### 3.1 系统框图

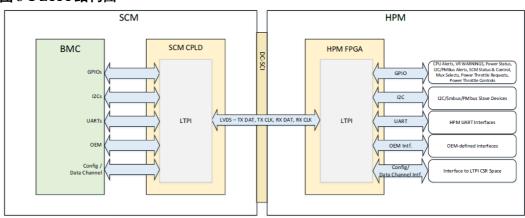

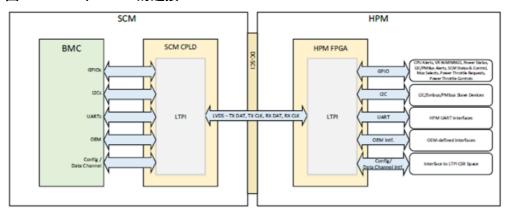

### 3.1.1 DC-SCM 2.0 LTPI 结构

LTPI 接口可以通过两个 FPGA 器件来实现,以便与典型的 BMC 器件进行配置:

● HPM FPGA: 提供本地 HPM 接口与 LTPI 的桥接

● SCM FPGA: 提供到本地 SCM 接口的 LTPI 桥接

### 图 3-1 LTPI 结构图

DC-SCM LTPI接口实现了通道的概念,其中每个通道都映射到 DC-SCM 和 HPM 上的特定类型的物理接口。LTPI接口定义了以下通道:

- GPIO 通道

- IIC/SMBus 通道

- UART 通道

- OEM 渠道

- 数据通道

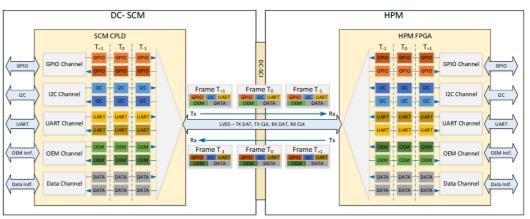

LTPI 使用高速 LVDS 全双工链路的时分复用(TDM)在 SCM 和 HPM 之间发送和接收 LTPI 信道。如图 3-2 所示,在 LVDS 链路上的每个相等时隙

IPUG1086-1.0 5(46)

3 功能描述 3.1 系统框图

中,都有一个LTPI 帧正在传输。在通过LTPI 接口发送的每个帧中,分配给特定信道的比特数与专用于每个信道的LTPI 带宽成正比。为了最大限度地减少对LTPI 信道的延迟影响,假设LTPI 帧是没有任何帧间间隙的。在无法避免帧间间隙的实现中,建议帧间间隙时间保持恒定,以最小化延迟变化并简化实现。

### 图 3-2 LTPI 各个通道传输示意图

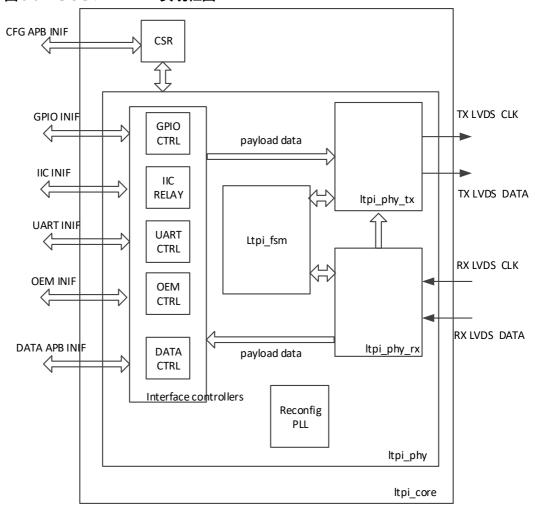

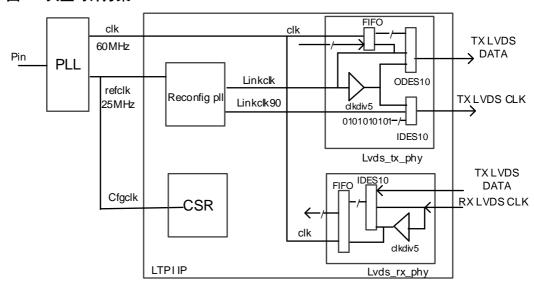

### 3.1.2 IP 实现框图

### 图 3-3 DC-SCM LTPI IP 实现框图

IPUG1086-1.0 6(46)

**3** 功能描述 **3.1** 系统框图

### DC-SCM LTPI IP 包含:

- interface controllers 模块:接收来自于外部接口的信号,通过内部的各个控制器/中继器来采集或者事务编码,将采集数据和编码数据发送到 ltpi\_phy\_tx 模块中组帧;接收来自于 LTPI 运行帧的内容,将其还原为外部接口的信号时序。包含以下接口:

- IIC/SMBus 中继器 IIC/SMBus 接口

- GPIO 控制器-GPIO 接口

- UART 控制器-UART 接口

- OEM 控制器-OEM 接口

- 数据总线控制器-数据通道桥接至外部接口

- Itpi\_phy\_tx 模块功能

- 每个 LTPI 信道都在 LTPI 帧内的专用位字段上编码

- 计算每帧的 CRC,并放与帧尾

- 然后使用 8b/10b 编码对帧进行编码

- 帧标志用帧逗点符号扩展(K码)

- 10b 编码帧在 LVDS TX 链路上串行化

- Itpi phy rx 模块功能

- LVDS 流量被捕获并反序列化到 10b 编码的 FIFO 缓冲器中

- 在 10b 数据流中, 帧 K 码被捕获为 LTPI 帧的开始

- 该帧被解码为 8b 编码

- 再次检查帧的 CRC 校验和,并将其分解为 LTPI 信道

- 使用信道控制器/中继器在各个信道上重建信道状态

- Itpi fsm 模块功能

- 链路初始化以及运行流程状态机

- Reconfig PLL 模块功能

- 根据 SCM 和 HPM 的速率协商结果,通过改变 PLL 的参数来生成对 应的 LVDS 速率。

IPUG1086-1.0 7(46)

3 功能描述 3.2 端口列表

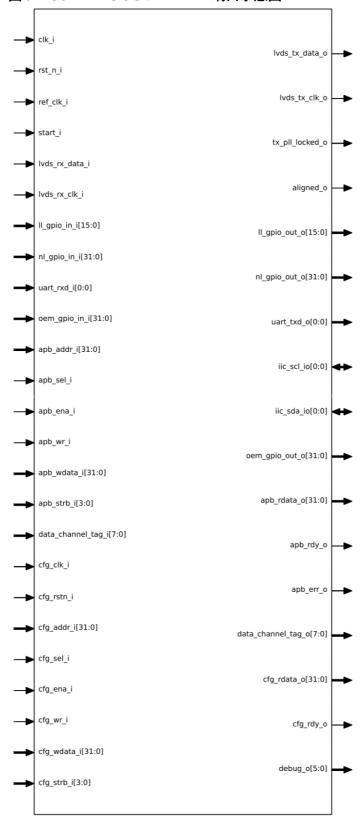

### 3.2 端口列表

Gowin DC-SCM LTPI IP 核的 IO 端口如图 3-4 所示,详细介绍如表 3-1 所示。

### 图 3-4 Gowin DC-SCM LTPI IP 端口示意图

IPUG1086-1.0 8(46)

3.2 端口列表

表 3-1 端口定义

| 名称                                 | I/O         | 位宽                      | 说明                                        |  |

|------------------------------------|-------------|-------------------------|-------------------------------------------|--|

| clk_i                              | input       | 1                       | 系统时钟,必须为 60MHz 输入                         |  |

| rst_n_i                            | input       | 1                       | 系统复位                                      |  |

| ref_clk_i                          | input       | 1                       | 参考时钟,必须为 25MHz 输入                         |  |

| start i                            | input       | 1                       | IP 核开始工作信号。                               |  |

| Start_i                            | input       | 1                       | 为高的时候开始 IP 开始运行                           |  |

| lvds_tx_data_o                     | output      | 1                       | LTPI 串行输出数据                               |  |

| lvds_tx_clk_o                      | output      | 1                       | LTPI 串行输出时钟                               |  |

| lvds_rx_data_i                     | input       | 1                       | LTPI 串行输入数据                               |  |

| lvds_rx_clk_i                      | input       | 1                       | LTPI 串行输入时钟                               |  |

| tx_pll_locked_o                    | output      | 1                       | 内部 PLL 锁定标志,该 PLL 用于驱动 TX 差分时钟和驱动 TX 差分数据 |  |

| aligned_o                          | output      | 1                       | 字节对齐标志                                    |  |

| 低延迟 GPIO 通道((                      | GPIO 接口使能后  | 有效)                     |                                           |  |

| Il_gpio_in_i                       | input       | [N <sup>[1]</sup> -1:0] | 低延迟 GPIO 输入管脚                             |  |

| Il_gpio_out_o                      | output      | [N-1:0]                 | 低延迟 GPIO 输出管脚                             |  |

| 正常延迟 GPIO 通道                       | (GPIO 接口使能  | 后有效)                    |                                           |  |

| nl_gpio_in_i                       | input       | [M <sup>[2]</sup> -1:0] | 正常延迟 GPIO 输入管脚                            |  |

| nl_gpio_out_o                      | output      | [M-1:0]                 | 正常延迟 GPIO 输出管脚                            |  |

| UART 通道(UART 技                     | 妾口使能后有效)    |                         |                                           |  |

| uart_rxd_i                         | input       | [L <sup>[3]</sup> -1:0] | UART 输入管脚                                 |  |

| uart_cts_i                         | input       | [L-1:0]                 | UART 流控管脚                                 |  |

| uart_txd_o                         | output      | [L-1:0]                 | UART 输出管脚                                 |  |

| uart_rts_o                         | output      | [L-1:0]                 | UART 流控管脚                                 |  |

| IIC/SMBus 通道(IIC                   | /SMBus 接口使能 | (后有效)                   |                                           |  |

| iic_scl_io                         | inout       | [K <sup>[4]</sup> -1:0] | IIC/SMBus SCL 管脚                          |  |

| iic_ssda_io                        | inout       | [K-1:0]                 | IIC/SMBus SDA 管脚                          |  |

| OEM 通道(OEM 接                       | 口使能后有效)     |                         |                                           |  |

| oem_gpio_in_i                      | input       | [P <sup>[5]</sup> -1:0] | OEM 输入管脚                                  |  |

| oem_gpio_out_o                     | output      | [P-1:0]                 | OEM 输出管脚                                  |  |

| Data 通道(Data 接口使能后有效)              |             |                         |                                           |  |

| data_channel_tag_i                 | input       | [7:0]                   | 数据通道数据帧的 Tag 字段内容输入                       |  |

| data_channel_tag_<br>o             | output      | [7:0]                   | 数据通道数据帧的 Tag 字段内容输出                       |  |

| Data 通道 APB 从端(SCM),(Data 接口使能后有效) |             |                         |                                           |  |

| apb_addr_i                         | input       | [31:0]                  | 总线配置地址                                    |  |

| apb_sel_i                          | input       | 1                       | 总线配置选择                                    |  |

| apb_ena_i                          | input       | 1                       | 总线配置使能                                    |  |

IPUG1086-1.0 9(46)

3 功能描述 3.2 端口列表

| 名称             | I/O            | 位宽       | 说明                                        |  |

|----------------|----------------|----------|-------------------------------------------|--|

|                |                |          | 总线方向信号                                    |  |

| apb_wr_i       | input          | 1        | 1: 写                                      |  |

|                |                |          | 0: 读                                      |  |

| apb_rdata_o    | output         | [31:0]   | 读取的数据                                     |  |

| apb_wdata_i    | input          | [31:0]   | 写入的数据                                     |  |

| apb_rdy_o      | output         | 1        | 准备好信号                                     |  |

| apb_err_o      | output         | 1        | 错误指示                                      |  |

| apb_strb_i     | input          | [3 :0]   | 写选通信号                                     |  |

| Data 通道 APB 主端 | (HPM), (Data 持 | 妾口使能后有效) |                                           |  |

| apb_addr_o     | output         | [31:0]   | 总线配置地址                                    |  |

| apb_sel_o      | output         | 1        | 总线配置选择                                    |  |

| apb_ena_o      | output         | 1        | 总线配置使能                                    |  |

|                |                |          | 总线方向信号                                    |  |

| apb_wr_o       | output         | 1        | 1. 写                                      |  |

|                |                |          | 0: 读                                      |  |

| apb_rdata_i    | input          | [31:0]   | 读取的数据                                     |  |

| apb_wdata_o    | output         | [31:0]   | 写入的数据                                     |  |

| apb_rdy_i      | input          | 1        | 准备好信号                                     |  |

| apb_err_i      | input          | 1        | 错误指示                                      |  |

| apb_strb_o     | output         | [3 :0]   | 写选通信号                                     |  |

| CSR 接口         |                |          |                                           |  |

| cfg_clk_i      | input          | 1        | CSR接口时钟,CSR接口也是APB接口,当数据通道启用时,这个时钟被用于数据通道 |  |

| cfg_rstn_i     | input          | 1        | 配置复位                                      |  |

| cfg_addr_i     | input          | [31:0]   | 总线配置地址                                    |  |

| cfg_sel_i      | input          | 1        | 总线配置选择                                    |  |

| cfg_ena_i      | input          | 1        | 总线配置使能                                    |  |

|                |                |          | 总线方向信号                                    |  |

| cfg_wr_i       | input          | 1        | 1: 写                                      |  |

|                |                |          | 0: 读                                      |  |

| cfg_rdata_o    | output         | [31:0]   | 读取的数据                                     |  |

| cfg_wdata_i    | input          | [31:0]   | 写入的数据                                     |  |

| cfg_rdy_o      | output         | 1        | 准备好信号                                     |  |

| cfg_strb_i     | input          | [3 :0]   | 写选通信号,内部固定为 4'hf                          |  |

| Debug 接口       |                |          |                                           |  |

| debug_o        | output         | [5:0]    | -                                         |  |

### 注!

- [<sup>1]</sup>表中 N 是 LL GPIO 数量,通过 GUI 设置。

- [2]表中 M 是 NL GPIO 数量,通过 GUI 设置。

IPUG1086-1.0 10(46)

3 功能描述 3.3 接口时序

- [3]表中 L 是 UART 数量,通过 GUI 设置。

- [4]表中 K 是 IIC/SMBus 数量,通过 GUI 设置。

- [5]表中 P 是 OEM 数量,通过 GUI 设置。

### 3.3 接口时序

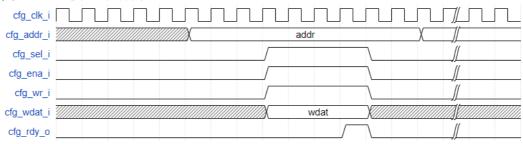

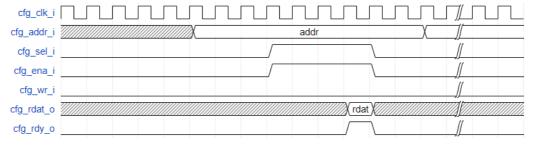

### 3.3.1 配置接口时序

内部寄存器通过总线进行配置。图 3-5 和图 3-6 是总线配置写时序图和读时序图,该接口与 APB slave 时序一致,可以直接接 APB master 模块。

### 图 3-5 配置接口写时序图

### 图 3-6 配置接口读时序图

### 3.3.2 数据接口时序

同配置接口时序,也是 APB 接口。

### 3.3.3 GPIO 接口时序

GPIO 接口直连即可。

### 3.3.4 UART 接口时序

标准 UART 接口时序。

### 3.3.5 IIC/SMBus 接口时序

标准 IIC/SMBus 总线时序。

IPUG1086-1.0 11(46)

### 3.4 寄存器描述

Gowin DC-SCM LTPI IP 中包含 LTPI 控制和状态寄存器(CSR),通过总线接口进行配置,地址以字节为单位。

表 3-2 Gowin DC-SCM LTPI IP 寄存器

| 地址偏移 | 比特    | 默认值 | W/R | 描述                                                                                                                                                           |

|------|-------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 31:24 | _   | _   | Reserved                                                                                                                                                     |

|      | 19:16 | _   | R   | 本地 LTPI 链路状态 0: 链路检测阶段 1: 速率协商阶段 2: 通告阶段 3: 配置阶段(SCM)、接受阶段(HPM) 4: 运行状态 5-7: 保留                                                                              |

|      | 15:12 | _   | R   | 对端 LTPI 链路状态 0: 链路检测阶段 1: 速率协商阶段 2: 通告阶段 3: 配置阶段 (SCM)、接受阶段 (HPM) 4: 运行状态 5-7: 保留                                                                            |

| 0x00 | 11:8  | _   | R   | LTPI 速度等级(LVDS 时钟频率) 0: 基频 X1 1: 基频 X2 2: 基频 X3 3: 基频 X4 4: 基频 X6 5: 基频 X8 6: 基频 X10 7: 基频 X12 8: 基频 X16 9: 基频 X24 10: 基频 X32 11: 基频 X40 12-15: 保留 基频为 25MHz |

|      | 7     | _   | R   | DDR 模式<br>0: SDR 模式<br>1: DDR 模式                                                                                                                             |

|      | 6     | _   | _   | 保留                                                                                                                                                           |

|      | 5     | _   | R   | 链路配置/接受握手超时错误                                                                                                                                                |

|      | 4     | _   | R   | 链路速率协商超时错误                                                                                                                                                   |

|      | 3     | _   | R   | 非法逗点符号错误                                                                                                                                                     |

IPUG1086-1.0 12(46)

| 地址偏移  | 比特    | 默认值                                    | W/R             | 描述                                                                            |

|-------|-------|----------------------------------------|-----------------|-------------------------------------------------------------------------------|

|       | 2     | _                                      | R               | 帧 CRC 错误                                                                      |

|       | 1     | _                                      | R               | LTPI 链路丢失错误                                                                   |

|       |       |                                        |                 | 链路对齐状态                                                                        |

|       | 0     | _                                      | R               | 0: 链路没对齐                                                                      |

|       |       |                                        |                 | 1: 链路对齐                                                                       |

|       | 31:24 | _                                      | _               | Reserved                                                                      |

|       | 23:8  | GUI 配置                                 | RW              | 本地链路速度能力,详细信息见表 3-3                                                           |

| 0x04  | 7:4   | GUI 配置                                 | R               | 本地LTPI Major版本<br>使用 BCD 编码                                                   |

|       | 3:0   | GUI 配置                                 | R               | 本地LTPI Minor版本<br>使用 BCD 编码                                                   |

|       | 31:24 | _                                      | _               | Reserved                                                                      |

|       | 23:8  | _                                      | R               | 对端链路速度能力,见表 3-4                                                               |

| 000   | 7.4   |                                        | <b>D</b>        | 对端LTPI Major版本                                                                |

| 0x08  | 7:4   | _                                      | R               | 使用 BCD 编码                                                                     |

|       | 2.0   |                                        | В               | 对端LTPI Minor版本                                                                |

|       | 3:0   | _                                      | R               | 使用 BCD 编码                                                                     |

| 0x0C  | 31:16 | _                                      | _               | Reserved                                                                      |

| UXUC  | 15:0  | 0x0                                    | RW              | LTPI 本地 Platform ID                                                           |

| 0x10  | 31:16 | _                                      | _               | Reserved                                                                      |

| OX 10 | 15:0  | _                                      | R               | LTPI 远端 Platform ID                                                           |

| 0x14  | 31:0  | GUI 配置                                 | RW              | 本地能力通告帧内容低 32bit,详细约定见表 3-4                                                   |

| 0x18  | 31:0  | GUI 配置                                 | RW              | 本地能力通告帧内容高 32bit,详细约定见表 3-4                                                   |

| 0x1C  | 31:0  | _                                      | R               | 对端能力通告帧内容低 32bit,详细约定见表 3-4                                                   |

| 0x20  | 31:0  | _                                      | R               | 对端能力通告帧内容高 32bit,详细约定见表 3-4                                                   |

| 0x24  | 31:0  | SCM:GUI<br>配置时默<br>认与本地<br>能力通告<br>帧相同 | SCM:RW<br>HPM:R | SCM:<br>LTPI 默认能力配置(低32bits)<br>HPM:<br>LTPI 接受并生效的配置(低 32bits)<br>详细约定见表 3-4 |

| 0x28  | 31:0  | SCM:GUI<br>配置时默<br>认与本地<br>能力通告<br>帧相同 | SCM:RW<br>HPM:R | SCM:<br>LTPI 默认能力配置(高32bits)<br>HPM:<br>LTPI 接受并生效的配置(高 32bits)<br>详细约定见表 3-4 |

| 0x2C  | 31:0  | 0x0                                    | RWC             | LTPI 链路对齐错误计数器                                                                |

| 0x30  | 31:0  | 0x0                                    | RWC             | LTPI 链路丢失错误计数器                                                                |

IPUG1086-1.0 13(46)

| 地址偏移 | 比特    | 默认值 | W/R | 描述                                                  |  |  |  |

|------|-------|-----|-----|-----------------------------------------------------|--|--|--|

| 0x34 | 31:0  | 0x0 | RWC | LTPI CRC 错误计数器                                      |  |  |  |

| 0x38 | 31:0  | 0x0 | RWC | 非法 Comma 错误计数器<br>链路速度协商超时错误计数器                     |  |  |  |

| 0x3C | 31:0  | 0x0 | RWC | 链路速度协商超时错误计数器                                       |  |  |  |

| 0x40 | 31:0  | 0x0 | RWC | SCM:<br>链路配置超时错误计数器<br>HPM:<br>链路接受超时错误计数器          |  |  |  |

|      | 31:24 | 0x0 | RWC | 配置帧(Configure Frame)接收计数器(仅 HPM)                    |  |  |  |

| 0x44 | 23:16 | 0x0 | RWC | 速度帧(Speed Frame)接收计数器                               |  |  |  |

|      | 15:0  | 0x0 | RWC | 检测帧(Detect Frame)接收计数器                              |  |  |  |

| 0x48 | 31:0  | 0x0 | RWC | 通告帧 (Advertise Frame) 接收计数器                         |  |  |  |

|      | 31:24 | 0x0 | RWC | 配置帧(Configure Frame)发送计数器(仅 HPM)                    |  |  |  |

| 0x4C | 23:16 | 0x0 | RWC | 速度帧(Speed Frame)发送计数器                               |  |  |  |

|      | 15:0  | 0x0 | RWC | 检测帧(Detect Frame)发送计数器                              |  |  |  |

| 0x50 | 31:0  | 0x0 | RWC | 运行帧 (Operational Frame) 接收计数器                       |  |  |  |

| 0x54 | 31:0  | 0x0 | RWC | 运行帧 (Operational Frame) 发送计数器                       |  |  |  |

|      | 31:12 | _   |     | 保留                                                  |  |  |  |

|      | 10    | 0x0 | RW  | 触发配置状态                                              |  |  |  |

|      | 9     | 0x0 | RW  | 自动跳转到配置状态<br>1: 自动跳转<br>0: 需要触发                     |  |  |  |

| 0x80 | 8     | 0x0 | RW  | 数据通道复位<br>1:表示复位<br>0:表示工作                          |  |  |  |

|      | 7:2   | 0x0 | RW  | LTPI IIC通道复位,每个bit表示每个IIC<br>通道<br>1:表示复位<br>0:表示工作 |  |  |  |

|      | 1     | 0x0 | RW  | LTPI 链路重新训练请求<br>上升沿会进行重新训练请求                       |  |  |  |

|      | 0     | 0x0 | RW  | LTPI 链路软复位<br>上升沿会进行软复位                             |  |  |  |

### 注!

R表示读,W表示写,WC表示写清除

IPUG1086-1.0 14(46)

### 表 3-3 速度描述

| 字节 | Bit 定义           |                  |                 |                 |                 |                  |                 |                  |  |  |

|----|------------------|------------------|-----------------|-----------------|-----------------|------------------|-----------------|------------------|--|--|

| 子巾 | 7                | 6                | 5               | 4               | 3               | 2                | 1               | 0                |  |  |

| 0  | 基频 x12<br>300MHz | 基频 x10<br>250MHz | 基频 x8<br>200MHz | 基频 x6<br>150MHz | 基频 x4<br>100MHz | 基频 x3<br>75MHz   | 基频 x2<br>50MHz  | 基频 x1<br>25MHz   |  |  |

| 1  | 0: SDR<br>1:DDR  | 保留               | 保留              | 保留              | 基频 x40<br>1GHz  | 基频 x32<br>800MHz | 基频 x24<br>50MHz | 基频 x16<br>400MHz |  |  |

### 表 3-4 通告帧能力描述

|        | 22 Carl Management                |                                         |                                    |                                    |                                    |                                    |                                    |                                    |  |  |

|--------|-----------------------------------|-----------------------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|--|--|

| 字节     | bit 定义                            | bit 定义                                  |                                    |                                    |                                    |                                    |                                    |                                    |  |  |

| 1 14   | 7                                 | 6                                       | 5                                  | 4                                  | 3                                  | 2                                  | 1                                  | 0                                  |  |  |

|        | Suppo                             | rted Channels                           |                                    |                                    |                                    |                                    |                                    |                                    |  |  |

| 0      | Reserv                            | ved                                     |                                    | OEM<br>channel                     | Data<br>channel                    | UART<br>channel                    | IIC<br>channel                     | GPIO<br>channel                    |  |  |

| 1      | GPIO                              | Channel Capabil                         | ities                              | ı                                  |                                    |                                    |                                    | 1                                  |  |  |

| I      | Numbe                             | er of NL GPIOs[7                        | [0:                                |                                    |                                    |                                    |                                    |                                    |  |  |

| 2      | Reserv                            | ved                                     |                                    |                                    |                                    |                                    | Number of<br>GPIOs[9:8]            |                                    |  |  |

|        | IIC Ch                            | IIC Channel Capabilities                |                                    |                                    |                                    |                                    |                                    |                                    |  |  |

| 3      | Rese<br>rved                      | EchoSupport 1: support 0: no support    | IIC5 En<br>1: enable<br>0: disable | IIC4 En<br>1: enable<br>0: disable | IIC3 En<br>1: enable<br>0: disable | IIC2 En<br>1: enable<br>0: disable | IIC1 En<br>1: enable<br>0: disable | IIC0 En<br>1: enable<br>0: disable |  |  |

| 4      | Reserved IIC5Spee d 1:400K 0:100K |                                         | IIC4Spee<br>d<br>1:400K<br>0:100K  | IIC3Spee<br>d<br>1:400K<br>0:100K  | IIC2Spee<br>d<br>1:400K<br>0:100K  | IIC1Spee<br>d<br>1:400K<br>0:100K  | IIC0Speed<br>1:400K<br>0:100K      |                                    |  |  |

|        | IIC Ch                            | annel Capabilitie                       | S                                  | l                                  | I                                  |                                    |                                    | I                                  |  |  |

| 5      | Rese<br>rved                      | UART1 En En Flow Max Baud Rate 定义见表 3-5 |                                    |                                    |                                    |                                    |                                    |                                    |  |  |

| 6<br>7 | OEM (                             | Capabilities                            |                                    |                                    |                                    |                                    |                                    |                                    |  |  |

IPUG1086-1.0 15(46)

表 3-5 串口通道最大波特率定义表

| Baud rate(bps) | Max baud rate encoding |

|----------------|------------------------|

| 300            | 0h00                   |

| 600            | 0h01                   |

| 1200           | 0h02                   |

| 1800           | 0h03                   |

| 2400           | 0h04                   |

| 4800           | 0h05                   |

| 9600           | 0h06                   |

| 19200          | 0h07                   |

| 38400          | 0h08                   |

| 57600          | 0h09                   |

| 115200         | 0h0A                   |

| 230400         | 0h0B                   |

| 460800         | 0h0C                   |

| 576000         | 0h0D                   |

| 921600         | 0h0E                   |

| Reserved       | 0h0F                   |

寄存器设置举例如下:

假如本端速度支持 X1、X2、X3、X4、X6、DDR;通道支持 GPIO、IIC/SMBus、UART、OEM、Data 通道,且

- LLGPIO 有 16 个

- NLGPIO 有 32 个

- IIC 有 1 个, 100K 速率, 支持 Echo

- OEM的 GPIO有32个

- Data 通道支持

- UART 有 1 个,不支持流控,支持 115200bps 的最大波特率 则寄存器设定为: 0x04[23:8] = 16h801f, 0x14[31:0] = 32h4100201f, 0x18[31:0] = 32h00002A00。

IPUG1086-1.0 16(46)

4 设计说明 4.1 线速率

# **4** 设计说明

### 4.1 线速率

DC-SCM 2.0 LTPI 规范定义了 12 种 LVDS 时钟,包括 X1(25MHz)、X2(50MHz)、X3(75MHz)、X4(100MHz)、X6(150MHz)、X8(200MHz)、X10(250MHz)、X12(300MHz)、X16(400MHz)、X24(600MHz)、X32(800MHz)、X40(1000MHz)。模式有 SDR 和 DDR 模式,如果是 SDR 模式,那么线速率就和时钟频率相同,例如工作在 X6(150MHz)下的 SDR 模式,那么线速率为 150Mbps,工作在 X6(150MHz)下的 DDR 模式,那么线速率为 300Mbps。

### 4.2 时钟

### 4.2.1 系统时钟

必须为固定为 60MHz。

### 4.2.2 参考时钟

必须固定为 25MHz, 且参考时钟需要与系统时钟同源。

### 4.2.3 配置时钟(cfg clk)

该内核通过配置接口进行寄存器的读写,同时如果使能了数据通道,则该时钟也作用于数据通道的 APB 接口。该接口的时钟是独立于系统时钟或参考时钟的时钟,此时钟与系统时钟或参考时钟之间没有依赖关系。

### 4.2.4 LVDS 时钟

IP 核内部存在动态可配置 PLL 模块,该 PLL 模块默认生成两个相位差90°(此相位差可以通过寄存器调整)的时钟 LINKCLK 和 LINKCLK90,根据速率协商的结果,进行 LVDS 频率动态配置,用于驱动 TX LVDS CLK 和 TX LVDS Data 信号的产生

### 4.2.5 RX/TX DIV5 时钟

IP 核内部存在串并转换原语 ISER10/OSER10,并行数据的时钟为LVDS CLK 的 5 分频。在发送部分,TXDIV5 由时钟 LINKCLK 通过原语 CLKDIV 进行 5 分频,在接收部分,RXDIV5 由接收的 LVDS CLK 通过原语 CLKDIV

IPUG1086-1.0 17(46)

4 设计说明 4.3 外部通道接口处理

进行5分频。

### 4.2.6 时钟结构

图 4-1 典型时钟方案

图 4-1 显示了一种时钟方案,基于同一个时钟源生成了系统时钟 clk,为60MHz;参考时钟 refclk,为25MHz;同时配置时钟 cfgclk 也可与参考时钟相同。

### 4.3 外部通道接口处理

LTPI 使用以下通用方法来采集和传输各种 LTPI 通道:

- **采样**: I/O 状态由 LTPI 进行采样,采样在 LTPI 帧中进行隧道传输。

- **事件/状态检测**:根据接口状态,为通道定义一组事件/状态,并在 LTPI 帧中进行隧道传输。

- **随机存取读/写请求**:外部接口触发随机存取内存映射通道。

LTPI 支持的接口也可以根据给定接口的 RX 和 TX 方向的同步来分类,即接口的隧道传输是否需要 TX 和 RX 方向在彼此之间同步:

- 异步:对于给定的信道和接口/链路,LTPITX和RX路径是独立的。

- **同步**:对于给定的信道和接口/链路,LTPI TX 和 RX 路径需要同步,以 允许接口在隧道传输后正确工作。

表 4-1 外部通道接口处理

| 直接采集信号电平低延迟 GPIO 每个 LPTI 帧都更新正常延迟 GPIO 可以设置数量更多,但由于 LPTI 帧给定的正常延迟 GPIO 的位置有限,因此可能会隔多个帧才更新 | 通道类型 | 采集方式 | TX 和 RX 同步方式 | 通道特性                                                                     |

|-------------------------------------------------------------------------------------------|------|------|--------------|--------------------------------------------------------------------------|

|                                                                                           | GPIO | 采样   | 异步           | 低延迟 GPIO 每个 LPTI 帧都更新<br>正常延迟 GPIO 可以设置数量更多,但<br>由于 LPTI 帧给定的正常延迟 GPIO 的 |

IPUG1086-1.0 18(46)

4 设计说明 4.3 外部通道接口处理

| 通道类型      | 采集方式    | TX 和 RX 同步方式 | 通道特性                                                                                                                      |

|-----------|---------|--------------|---------------------------------------------------------------------------------------------------------------------------|

|           |         |              | 标志用于识别正常延迟 GPIO 的位置                                                                                                       |

|           |         |              | 直接采集信号电平                                                                                                                  |

| UART      |         |              | UART 信号进行过采样                                                                                                              |

|           |         |              | 每个 LTPI 帧包含多个采样值                                                                                                          |

| IIC/SMBus | 事务/状态检测 | 同步           | IIC/SMBus 由于需要来回交互,因此IIC/SMBus 状态被编码成 LTPI 事务通过 LTPI 传输在 LTPI 事务发送之后,需要等待另一端的 LTPI 接口的事务回应,因此需要使用 IIC/SMBus 时钟扩展功能来等待同步完成 |

| Data Bus  | 随机访问    |              | 数据总线传输如数据读和写被编码为<br>LTPI 事务<br>总线操作完成指示用于同步对数据总<br>线的访问                                                                   |

### 4.3.1 GPIO 通道

对于 GPIO 通道,GPIO 逻辑状态(高和低)直接编码在 LTPI 帧位上。低延迟(LL)GPIO 在每个 LTPI 帧被刷新,并且在发送的每个帧中具有用于每个 GPIO 的专用位。每 N 个帧刷新一次正常延迟(NL)GPIO,其中 N 定义为:

$$N = (\frac{Total\ Number\ of\ NL\ GPIOs\ tunneled\ over\ LTPI}{Number\ of\ NL\ GPIO\ bits\ per\ LTPI\ IO\ Frame})$$

N = 需要传递的 GPIO 总数/每个 IO 帧的 NL GPIO 比特数

为了解码在给定帧中隧道传输的 NL GPIO,使用在每个帧中递增的帧计数器来解码来自 LTPI 帧的 NL GPIO 索引。LTPI 帧中 LTPI GPIO 通道的编码如下表所示,其中 LL 和 NL GPIO 分别定义在 1 个字节上。对于 LL GPIO,一个字节中的每一位都被定义为数字为 0 到 7 的 GPIO。对于 NL GPIO,为了解码每个位位置 0 到 7 的 GPIO 编号,需要添加偏移 X,其中 X 定义为:

X = (Frame Counter%N)

\* (Number of NL GPIO bits per LTPI Frame)

### 表 4-2 GPIO 字段配置

| 名称                    | Bit 定义                           | Bit 定义                           |                                     |                                     |                                     |                                     |                                     |                                   |  |

|-----------------------|----------------------------------|----------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-----------------------------------|--|

| 石柳                    | 7                                | 6                                | 5                                   | 4                                   | 3                                   | 2                                   | 1                                   | 0                                 |  |

| 低延迟 GPIO<br>(LLGPIO)  | LL<br>GPIO7<br>0: 低<br>1: 高      | LL<br>GPIO6<br>0: 低<br>1: 高      | LL<br>GPIO5<br>0: 低<br>1: 高         | LL<br>GPIO4<br>0: 低<br>1: 高         | LL<br>GPIO3<br>0: 低<br>1: 高         | LL<br>GPIO2<br>0: 低<br>1: 高         | LL<br>GPIO1<br>0: 低<br>1: 高         | LL<br>GPIO0<br>0: 低<br>1: 高       |  |

| 正常延迟 GPIO<br>(NLGPIO) | NL GPIO<br>[X+7]<br>0: 低<br>1: 高 | NL GPIO<br>[X+6]<br>0: 低<br>1: 高 | NL<br>GPIO<br>[X+5]<br>0: 低<br>1: 高 | NL<br>GPIO<br>[X+4]<br>0: 低<br>1: 高 | NL<br>GPIO<br>[X+3]<br>0: 低<br>1: 高 | NL<br>GPIO<br>[X+2]<br>0: 低<br>1: 高 | NL<br>GPIO<br>[X+1]<br>0: 低<br>1: 高 | NL<br>GPIO<br>[X]<br>0: 低<br>1: 高 |  |

IPUG1086-1.0 19(46)

4.3 外部通道接口处理

默认 I/O 帧为低延迟 GPIO 分配 2 个字节,为正常延迟 GPIO 配置 2 个字节。这意味着每个 IO 帧中可以发送 16 个 NL GPIO,并且传输所有 NL GPIO需要 N 个帧。如果某个实现需要在单个 IO 帧中定义更多 LL 或 NL GPIO,则可以使用 OEM 字段来扩展默认 I/O 帧。

正常延迟 GPIO 的总数在"NL GPIO 数量"字段的能力帧中定义。能力在LTPI 训练阶段进行交换。通过这种方式,SCM 中的 LTPI 和 HPM 中的 LTPI 能够基于上面定义的帧计数器和 N 参数来正确地解码给定帧中的 NL GPIO的索引。

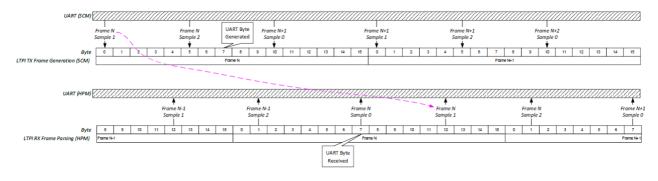

### 4.3.2 UART 通道

UART 通道的工作原理类似于 LL GPIO 通道。不同之处在于,对 UART 发送数据(TXD)和接收数据(RXD)线的采样频率是 LL GPIO 采样频率的 3 倍。

UART 采样数据如何通过 LTPI 帧从 TX 端到 RX 端,并且在接收端恢复 UART 数据,如下图 4-2 所示。如本例所示,当生成字节号 7 并通过 LTPI 传输时,UART 样本需要准备就绪。这意味着在此之前,需要收集 3 个样本,假设样本随时间均匀分布。对于帧 N,当发送前一帧(N-1)的字节 10 时,实际采集样本 0。当通过 LTPI 发送字节 0 时采集样本 1,当生成并发送带有 UART 样本的字节 7 时采集样本 2。通过这种方式,在帧之间保持样本随时间的均匀分布。在接收器侧,当接收到的样本用于在 UART 接口上生成信号时,需要保持相同的分布。当接收到帧 N 的字节 7 时,样本 0 用于在 UART 接口上生成信号,当接收到字节 12 时,从帧 N 生成下一个样本 1。最后一个采样是在下一帧(N+1)的字节 1 上生成的。

#### 图 4-2 UART 采样与恢复示意图

UART 信道与 RXD 和 TXD 信号一起支持 RTS 和 CTS 支持的流控制信号隧道。流控制信号不是过采样的,而是类似于低延迟 GPIO 在每个 LTPI 帧中编码。表 4-3 显示了 UART 通道的编码。每个信道被编码在用于 TX 的 4 比特和用于 RX 方向的 4 比特上。这些编码将通过 LTPI 接口单独进行隧道传输。在该示例中,从 SCM 的角度考虑方向,因此 UART0/1 TX 编码适用于从 SCM 到 HPM 的隧道传输的 LTPI 帧。UART0/1 RX 编码适用于从 HPM 通过隧道传输到 SCM 的 LTPI 帧。

IPUG1086-1.0 20(46)

4 设计说明 4.3 外部通道接口处理

| _     |               | _                    |              |

|-------|---------------|----------------------|--------------|

| 主 /   | 2 T I A       | рт 🕏                 | 段配置          |

| 10x T | -0 U <i>F</i> | 71/ I <del>- 1</del> | - FV EII . 🗎 |

| 名称            | Bit 定义 |        |        |        |       |        |        |        |

|---------------|--------|--------|--------|--------|-------|--------|--------|--------|

| - E 1/4       | 7      | 6      | 5      | 4      | 3     | 2      | 1      | 0      |

|               | UART1  |        |        |        | UART0 |        |        |        |

| UART0/1 TX 编码 | RTS    | TXD[2] | TXD[1] | TXD[0] | RTS   | TXD[2] | TXD[1] | TXD[0] |

| UARTU/IIX 编码  | 0: 低   | 0: 低   | 0: 低   | 0: 低   | 0: 低  | 0: 低   | 0: 低   | 0: 低   |

|               | 1: 高   | 1: 高   | 1: 高   | 1: 高   | 1: 高  | 1: 高   | 1: 高   | 1: 高   |

| UART0/1 RX 编码 | CTS    | RXD[2] | RXD[1] | RXD[0] | CTS   | RXD[2] | RXD[1] | RXD[0] |

|               | 0: 低   | 0: 低   | 0: 低   | 0: 低   | 0: 低  | 0: 低   | 0: 低   | 0: 低   |

|               | 1: 高   | 1: 高   | 1: 高   | 1: 高   | 1: 高  | 1: 高   | 1: 高   | 1: 高   |

### 4.3.3 IIC/SMBus 通道

IIC/SMBus SCL 和 SDA 信号是双向的,并且可以在 IIC/SMBus 事件期间由控制器或目标设备主动驱动。因此,SCL 和 SDA 信号不能像 GPIO 或UART 信号那样直接通过 LTPI 进行隧道传输。在 LTPI 中,IIC/SMBus 通道实现了基于事件的模型,其中编码的 IIC/SMBus 事件/状态在 LTPI 的一侧被捕获并在另一侧被恢复。当 IIC/SMBus 事件由控制器生成时(例如,START条件),控制器的本地 SCL 线由 LTPI IP 来进行拉伸,直到接收到远端事件。当接收到远端事件时,它在控制器本地总线上恢复,然后 SCL 从拉伸状态释放。

表 4-4 IIC/SMBus 通道事务定义

| 总线事件                     | 方向                                | 描述                               | 事务编码(4bit) |

|--------------------------|-----------------------------------|----------------------------------|------------|

| Idle                     | 双向                                | 空闲状态                             | 4b0000     |

| Start                    | 控制端 (Controller)<br>到目标端 (Target) | 控制端检测到开始事件                       | 4b0001     |

| Start<br>Received        | 目标端到控制端                           | 开始事件在目标端恢复                       | 4b0010     |

| Stop                     | 控制端到目标端                           | 控制端检测到停止事件                       | 4b0011     |

| Stop<br>Received         | 目标端到控制端                           | 停止事件在目标端恢复                       | 4b0100     |

| Data<br>Received         | 双向                                | SDA 值在对端恢复                       | 4b0101     |

| Data0                    | 双向                                | 发送 SDA 值 0                       | 4b0110     |

| Data1                    | 双向                                | 发送 SDA 值 1                       | 4b0111     |

| Start Echo               | 目标端到控制端                           | 开始事件被目标端正确接收<br>的反馈事务            | 4b1000     |

| Stop Echo                | 目标端到控制端                           | 停止事件被目标端正确接收<br>的反馈事务            | 4b1001     |

| Data0 Echo               | 双向                                | 发送的 SDA 值 0 正确接收                 | 4b1010     |

| Data1 Echo               | 双向                                | 发送的 SDA 值 1 正确接收                 | 4b1011     |

| Data<br>Received<br>Echo | 双向                                | 表示 Data Received 事件被正确接收。它用于区分字节 | 4b1100     |

IPUG1086-1.0 21(46)

4 设计说明 4.3 外部通道接口处理

| 总线事件     | 方向 | 描述                    | 事务编码(4bit)    |

|----------|----|-----------------------|---------------|

|          |    | 传输过程中连续的 Data 0/1 事件。 |               |

| Reserved | 保留 | 保留                    | 4b1101-4b1111 |

每个 IIC/SMBus 总线相当于 4 位有效负载数据,如表 4-4 所示。在表 4-5 的示例中,对于 6 个 IIC/SMBus 总线,每帧相应地为 IIC/SMBus 通道分配了 3 个字节的有效负载。

表 4-5 IIC/SMBus 字段配置

| IIC/SMBus | Bit 定义          | Bit 定义   |          |          |                 |          |          |          |  |  |  |  |

|-----------|-----------------|----------|----------|----------|-----------------|----------|----------|----------|--|--|--|--|

| 载荷字节      | 7               | 6        | 5        | 4        | 3               | 2        | 1        | 0        |  |  |  |  |

| 0         | IIC/SMBus       | BUS 1    |          |          | IIC/SMBus BUS 0 |          |          |          |  |  |  |  |

| 0         | Event[3]        | Event[2] | Event[1] | Event[0] | Event[3]        | Event[2] | Event[1] | Event[0] |  |  |  |  |

| 1         | IIC/SMBus       | BUS 3    |          |          | IIC/SMBus BUS 2 |          |          |          |  |  |  |  |

| I         | Event[3]        | Event[2] | Event[1] | Event[0] | Event[3]        | Event[2] | Event[1] | Event[0] |  |  |  |  |

| 2         | IIC/SMBus BUS 5 |          |          |          | IIC/SMBus BUS 4 |          |          |          |  |  |  |  |

|           | Event[3]        | Event[2] | Event[1] | Event[0] | Event[3]        | Event[2] | Event[1] | Event[0] |  |  |  |  |

图 4-3 IIC/SMBus 总线事务交换

图 4-3 显示了 IIC/SMBus 总线事件交换。事件由控制器发起。一旦在 LTPI 中检测到事件请求,通信方就会通过 LTPI 将编码的事件 echo 发送回请求方来确认接收,并且当事件成功时,它会发送事件接收数据包。当任一方等待通信方的反馈时,本地 SCL 总线上会进行时钟拉伸,以防止当前事务正在进行时出现新事务。编码数据包持续传输,直到生成新事件。SCL 接口中的粗线表示在 SCL 总线上完成的时钟延伸。

IPUG1086-1.0 22(46)

4.3 外部通道接口处理

### 表 4-6 IIC/SMBus 事务流程

| 序号 | 控制端                                                                                                                                                                                                      | 目标端                                                                                                                                                                  | IIC/SMBus 事件                      | LTPI 事件方向 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------|

| 1  | IP 检测 SDA 下降沿和 SCL 高电平,开始向 LTPI 接口发送 Start 事件;IP 触发本地 SCL 上的 SCL 延伸并等待接收到 START Received.                                                                                                                | 总线空闲状态                                                                                                                                                               | Start                             | 控制端到目标端   |

| 2  | 时钟拉伸                                                                                                                                                                                                     | 从 LTPI 收到 Start 事件,发送 start echo 事件进行反馈,在本地 SCL 和 SDA 总线生成开始条件时序;发送 Start Received 事件到 LTPI; 触发 SCL 拉伸并等待下一个事件                                                       | Start Echo<br>Start Received      | 目标端到控制端   |

| 3  | 从 LTPI 接收到了 start Received 事件后停止本地总线的时钟拉升;控制器开始发送数据 bit; IP 检测到本地总线的 SCL 上升沿和 SDA 数据; IP 检测 SCL 下降沿,并发送 Data0/1 事务到 LTPI. IP 触发本地 SCL 上的 SCL 延伸并等待接收到 Data Received 事件                                   | 时钟拉伸                                                                                                                                                                 | Data0/1                           | 控制端到目标端   |

| 4  | 时钟拉伸                                                                                                                                                                                                     | 从 LTPI 收到 Data0/1 事件,<br>发送 Data echo 事件进行反<br>馈,释放 SCL 并在本地 SCL<br>和 SDA 总线发送数据 0/1;<br>在 SCL 高电平保持时间之后<br>SCL 拉低;发送 Data<br>Received 事件到 LTPI;触发<br>SCL 拉伸并等待下一个事件 | Data Echo<br>Data Received        | 目标端到控制端   |

| 5  | 从 LTPI 接收到了 Data Received 事件后停止本地总 线的时钟拉升;发送 Data Received Echo 事件到 LTPI 接口,控制器开始发送数据 bit; IP 检测到本地总线的 SCL 上升沿和 SDA 数据; IP 检测 SCL 下降沿,并发送 Data0/1 事务到 LTPI. IP 触发本地 SCL 上的 SCL 延伸并等待接收到 Data Received 事件 | 时钟拉伸                                                                                                                                                                 | Data Received<br>Echo<br>Data 0/1 | 控制端到目标端   |

| 6  | 时钟拉伸                                                                                                                                                                                                     | 首先从 LTPI 收到 Data<br>Received Echo 事件,表明<br>上一个 bit 发送完成,接下来<br>接收一个新的 Data 0/1 事<br>件; 发送 Data echo 事件进<br>行反馈,释放 SCL 并在本地<br>SCL 和 SDA 总线发送数据                       | Data Echo<br>Data Received        |           |

IPUG1086-1.0 23(46)

4.3 外部通道接口处理

|     | 校判禮                                                                                                                                                                 | 日左端                                                                                                              | IIC/CMPa 市件                | ITDI 東州之白 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------|-----------|

| 序号  | 控制端                                                                                                                                                                 | 目标端                                                                                                              | IIC/SMBus 事件               | LTPI 事件方向 |

|     |                                                                                                                                                                     | 0/1; 在 SCL 高电平保持时<br>间之后 SCL 拉低;发送 Data                                                                          |                            |           |

|     |                                                                                                                                                                     | Received 事件到 LTPI; 触发                                                                                            |                            |           |

|     |                                                                                                                                                                     | SCL 拉伸并等待下一个事件                                                                                                   |                            |           |

|     |                                                                                                                                                                     |                                                                                                                  |                            | •••       |

| 数据事 | 系方向的改变,即本例中的 AC                                                                                                                                                     | CK/NACK,但对于读事务中的验                                                                                                | 数据位来说是相同的                  | 的         |

|     |                                                                                                                                                                     |                                                                                                                  |                            |           |

| 7   | 时钟拉伸                                                                                                                                                                | 目的端将数据 bit 置于 SDA; IP 检测到本地总线上的 SCL 上升沿且 SDA 数据; IP 检测到 SCL 下降沿,且发送 Data0/1 事件到 LTPI; 触发 SCL 拉伸并等待下一个事件          | Data 0/1                   | 目标端到控制端   |

| 8   | 从 LTPI 收到 Data0/1 事件,<br>发送 Data echo 事件进行反<br>馈,释放 SCL 并在本地 SCL<br>和 SDA 总线发送数据 0/1;在<br>SCL 高电平保持时间之后<br>SCL 拉低;发送 Data<br>Received 事件到 LTPI;触发<br>SCL 拉伸并等待下一个事件 | 时钟拉伸                                                                                                             | Data Echo<br>Data Received | 控制端到目标端   |

| 9   | 时钟拉伸                                                                                                                                                                | 从 LTPI 接收到了 Data<br>Received 事件;开始发送<br>Data Receivd Echo 事件                                                     | Data Received<br>Echo      | 目标端到控制端   |

|     |                                                                                                                                                                     |                                                                                                                  |                            |           |

| 10  | 当本地总线上的 SCL 为高电平时(本地总线上的停止条件),IP 检测到 SDA 上升沿。IP 向 LTPI 发送 STOP 事件。                                                                                                  | 时钟拉伸                                                                                                             | Stop                       | 控制端到目标端   |

| 11  | 等待 Stop Echo 和 Stop Received 事件; IP 等待新的 IIC 起始条件,如果检测到新的 START 条件,则应将其推迟(使用时钟拉伸),直到收到先前 STOP 条件的 Stop Received 事件。                                                 | 收到 Stop 事件;发送 Stop<br>Echo 事件并开始在本地总<br>线 SCL 和 SDA 上生成停止<br>条件时序信号;通过 LTPI<br>接口发送 Stop Received;触<br>发总线状态为空闲。 | Stop Echo<br>Stop Received | 目标端到控制端   |

| 12  | 总线空闲状态                                                                                                                                                              | 总线空闲状态                                                                                                           | Idle                       | N/A       |

IPUG1086-1.0 24(46)

4 设计说明 4.3 外部通道接口处理

### 4.3.4 OEM 通道

OEM 通道将类似于与 LLGPIO,与 LLGPIO 不同的地方在于,OEM 通道将在所有非数据通道帧传输时更新,而 LLGPIO 在数据通道帧传输也会更新。

### 4.3.5 数据通道

数据通道允许将标准化读取和写入请求传送到可寻址内存空间。 DC-SCM LTPI 软 IP 支持数据通道的 APB 接口,并且在启用时可以按需访问。在 LTPI 中,数据通道实现了基于事件的模型,其中编码的数据事件/状态在 LTPI 的一侧被捕获并在另一侧被恢复。

### 表 4-7 数据通道事务定义

| 指令     | 参数    | 描述                         | 8bit 事件编码 |

|--------|-------|----------------------------|-----------|

| 读请求    | 地址    | 读指定地址的请求指令                 | 0x00      |

| 写请求    | 地址和数据 | 写指定地址和数据的请求指令              | 0x01      |

| 读完成    | 地址和数据 | 读操作完成指令                    | 0x02      |

| 写完成    | 地址    | 写操作完成指令                    | 0x03      |

| CRC 错误 | 无     | 接收的数据帧 CRC 错误,并且操作不能<br>完成 | 0x04      |

| 保留     | 保留    | 保留                         | 0x05~0xFF |

根据指令请求,每个数据通道字节被映射到数据帧中的每个有效负载字节。

### 表 4-8 数据通道字段配置

| 名称    | 比特编码                |            |       |      |                   |                   |                   |            |  |  |  |

|-------|---------------------|------------|-------|------|-------------------|-------------------|-------------------|------------|--|--|--|

| H 14. | 7                   | 6          | 5     | 4    | 3                 | 2                 | 1                 | 0          |  |  |  |

|       | Comma               | nd = 8'h(  | 00    |      |                   |                   |                   |            |  |  |  |

|       | 地址字章                | 节 3        |       |      |                   |                   |                   |            |  |  |  |

|       | 地址字世                | 节 2        |       |      |                   |                   |                   |            |  |  |  |

| 读操作   | 地址字寸                | <b>节 1</b> |       |      |                   |                   |                   |            |  |  |  |

|       | 地址字节 0              |            |       |      |                   |                   |                   |            |  |  |  |

|       | 保留                  |            |       |      | 字节 <b>3</b><br>使能 | 字节 <b>2</b><br>使能 | 字节 <b>1</b><br>使能 | 字节 0<br>使能 |  |  |  |

|       | Comma               | nd = 8'h(  | 02    |      |                   |                   |                   |            |  |  |  |

|       | 地址字章                | 地址字节 3     |       |      |                   |                   |                   |            |  |  |  |

|       | 地址字章                | <b>节 2</b> |       |      |                   |                   |                   |            |  |  |  |

| 读操作完成 | 地址字节 1              |            |       |      |                   |                   |                   |            |  |  |  |

|       | 地址字节 0              |            |       |      |                   |                   |                   |            |  |  |  |

|       | 读操作状态 字节3 字节2 字节1 写 |            |       |      |                   |                   | 字节 0              |            |  |  |  |

|       | 0:成功,               | 1: 非法      | 访问,2- | F 保留 | 使能                | 使能                | 使能                | 使能         |  |  |  |

IPUG1086-1.0 25(46)

4 设计说明 4.4LTPI 帧格式

| 名称    | 比特编码                  |       |      |      |      |  |  |  |  |  |  |

|-------|-----------------------|-------|------|------|------|--|--|--|--|--|--|

|       | 数据字节 3                | 数据字节3 |      |      |      |  |  |  |  |  |  |

|       | 数据字节2                 | 数据字节2 |      |      |      |  |  |  |  |  |  |

|       | 数据字节1                 |       |      |      |      |  |  |  |  |  |  |

|       | 数据字节 0                |       |      |      |      |  |  |  |  |  |  |

|       | Command = 8'h01       |       |      |      |      |  |  |  |  |  |  |

|       | 地址字节 3                |       |      |      |      |  |  |  |  |  |  |

|       | 地址字节 2                |       |      |      |      |  |  |  |  |  |  |

|       | 地址字节 1                |       |      |      |      |  |  |  |  |  |  |

|       | 地址字节 0                |       |      |      |      |  |  |  |  |  |  |

| 写操作   | 保留                    | 字节3   | 字节 2 | 字节 1 | 字节 0 |  |  |  |  |  |  |

|       | N. III                | 使能    | 使能   | 使能   | 使能   |  |  |  |  |  |  |

|       | 数据字节3                 |       |      |      |      |  |  |  |  |  |  |

|       | 数据字节2                 |       |      |      |      |  |  |  |  |  |  |

|       | 数据字节 1                |       |      |      |      |  |  |  |  |  |  |

|       | 数据字节 0                |       |      |      |      |  |  |  |  |  |  |

|       | Command = 8'h01       |       |      |      |      |  |  |  |  |  |  |

|       | 地址字节 3                |       |      |      |      |  |  |  |  |  |  |

|       | 地址字节 2                |       |      |      |      |  |  |  |  |  |  |

| 写操作完成 | 地址字节 1                |       |      |      |      |  |  |  |  |  |  |

|       | 地址字节 0                |       |      |      |      |  |  |  |  |  |  |

|       | 写操作状态                 | 保留    |      |      |      |  |  |  |  |  |  |

|       | 0:成功, 1: 非法访问, 2-F 保留 |       |      |      |      |  |  |  |  |  |  |

### 4.4 LTPI 帧格式

### 4.4.1 帧格式

IP 中所设计的帧格式全部与 DC-SCM 2.0 LTPI 协议中规定的一致,所有类型的帧格式都是固定长度的,一共 16 个字节,其格式如表 4-9 所示。

### 表 4-9 帧格式说明

| 字节数  | 说明         |

|------|------------|

| 0    | 帧起始,K码     |

| 1    | 帧类型        |

| 2-14 | 帧数据        |

| 15   | CRC8 校验,帧尾 |

IPUG1086-1.0 26(46)

**4** 设计说明 **4.4LTPI** 帧格式

### 4.4.2 具体帧定义

### 1. 链路训练阶段

该阶段有两种子帧类型,如表 4-10 所示。

### 表 4-10 链路训练阶段帧类型

| 帧类型         | 逗点符号  | 帧类型值 |

|-------------|-------|------|

| Link Detect | K28.5 | 0x00 |

| Link Speed  | K20.5 | 0x01 |

### a. Link Detect Frame

首先双方一开始发送的是 Link Detect Frame 帧,具体定义见表 4-11。

### 表 4-11 Link Detect 帧定义

| 帧内字节    | Bit 内容 |                             |   |   |   | - 描述 |               |                         |    |

|---------|--------|-----------------------------|---|---|---|------|---------------|-------------------------|----|

| 製 内 于 1 | 7      | 6                           | 5 | 4 | 3 | 2    | 1             | 0                       | 抽处 |

| 0       | 逗点     | 京符号                         | 1 |   |   |      | 根据上表定义        |                         |    |

| 1       | 帧类     | 帧类型                         |   |   |   |      |               | 根据上表定义                  |    |

| 2       | LTP    | LTPI Major 版本 LTPI Minor 版本 |   |   |   |      |               | BCD 编码 [Major].[ Minor] |    |

| 3       | 油用     | 速度能力                        |   |   |   |      |               | 格式见表 3-3                |    |

| 4       | 还以     | <b>还</b> /文化/J              |   |   |   |      |               | 借入允农 3-3                |    |

| 5-14    | 保留     | 保留                          |   |   |   |      |               | 保留                      |    |

| 15      | CR     | CRC                         |   |   |   |      | CRC8 checksum |                         |    |

### b. Link Speed Frame

Link Speed Frame 帧格式与 Link Detect Frame 帧格式完全相同,只是 Link Speed Frame 帧中 Speed Select 是已经协商后的速率,如表 4-12 所示。

### 表 4-12 Link Speed 帧定义

| 帧内字节 | Bit 内容        |               | - 描述                    |  |

|------|---------------|---------------|-------------------------|--|

| 製    | 7 6 5 4       | 3 2 1 0       | 加处                      |  |

| 0    | 逗点符号          |               | 根据上表定义                  |  |

| 1    | 帧类型           |               | 根据上表定义                  |  |

| 2    | LTPI Major 版本 | LTPI Minor 版本 | BCD 编码 [Major].[ Minor] |  |

| 3    | 协商后速度         |               | 格式见表 3-3                |  |

| 4    |               |               | 情式光衣 3-3                |  |

| 5-14 | 保留            |               | 保留                      |  |

| 15   | CRC           |               | CRC8 checksum           |  |

### 2. 链路配置阶段

该阶段有三种子帧类型,如表 4-13 所示。

IPUG1086-1.0 27(46)

4 设计说明 4.4LTPI 帧格式

### 表 4-13 链路配置阶段帧类型

| 帧类型       | 逗点符号  | 帧类型值 |

|-----------|-------|------|

| Advertise |       | 0x00 |

| Configure | K28.6 | 0x01 |

| Accept    |       | 0x02 |

### a. LTPI Advertise Frame

速率协商完成之后,SCM 和 HPM 都会发送 Advertise 帧,互相通告能力,具体定义如表 4-14。

### 表 4-14 Advertise 帧定义

| J. F. J. Darlia | Bit                               | 内容    |        |          |    |       |   | 1417 b            |          |  |  |

|-----------------|-----------------------------------|-------|--------|----------|----|-------|---|-------------------|----------|--|--|

| 帧内字节            | 7                                 | 6     | 5      | 4        | 3  | 2     | 1 | 0                 | 描述       |  |  |

| 0               | 逗点                                | 点符号   | 크<br>プ |          |    |       |   | 根据上表定义            |          |  |  |

| 1               | 帧乡                                | 类型    |        |          |    |       |   | 根据上表定义            |          |  |  |

| 2               | Dla                               | tform | , 米用   | ıJ       |    |       |   | -                 |          |  |  |

| 3               | ı ıa                              | uom   | 1 大3   | <u>.</u> |    |       |   |                   |          |  |  |

|                 |                                   | 力类型   |        |          |    |       |   | 能力类型允许自定义 LTPI 能力 |          |  |  |

| 4               |                                   | )0 默  |        |          | 型  |       |   |                   |          |  |  |

|                 | 0x01-0x80 保留<br>0x81-0xFF OEM 自定义 |       |        |          |    |       |   |                   | 16,000   |  |  |

|                 | 3x0                               | 31-0x | FF C   | DEM      | 目定 | 义<br> |   |                   |          |  |  |

| 5               |                                   |       |        |          |    |       |   |                   |          |  |  |

| 6               |                                   |       |        |          |    |       |   |                   |          |  |  |

| 7               |                                   |       |        |          |    |       |   |                   |          |  |  |

| 8               | LTF                               | ol 能  | 力      |          |    |       |   |                   | 格式见表 3-4 |  |  |

| 9               |                                   |       |        |          |    |       |   |                   |          |  |  |

| 10              |                                   |       |        |          |    |       |   |                   |          |  |  |

| 11              |                                   |       |        |          |    |       |   |                   |          |  |  |

| 12              |                                   |       |        |          |    |       |   |                   |          |  |  |

| 13-14           | 保旨                                | 習     |        |          |    |       |   | 保留                |          |  |  |

| 15              | CR                                | C     |        |          |    |       |   | CRC8 checksum     |          |  |  |

互相通告能力之后,接下来,SCM 会发送 Configure 帧。Configure 帧与 Advertise 帧格式一致,不同在于,SCM 会将 SCM 预设的能力或者是 BMC 实时设置的能力放置于请求 LTPI 能力字段。

### b. LTPI Configure Frame

### 表 4-15 Configure 帧定义

| 帧内字节 | Bit | 内容  |   |   |   |   | 描述 |        |

|------|-----|-----|---|---|---|---|----|--------|

|      | 7   | 6   | 5 | 4 | 3 | 2 | 1  | 0      |

| 0    | 逗点  | 京符号 | Ļ |   |   |   |    | 根据上表定义 |

| 1    | 帧学  | き型  |   |   |   |   |    | 根据上表定义 |

IPUG1086-1.0 28(46)

4 设计说明 4.4LTPI 帧格式

| 帧内字节  | Bit 内容            | 描述                |  |  |

|-------|-------------------|-------------------|--|--|

| 2     | Platform 类型       |                   |  |  |

| 3     | Tiation 天生        |                   |  |  |

|       | 能力类型              |                   |  |  |

| 4     | 0x00 默认能力类型       | 能力类型允许自定义 LTPI 能力 |  |  |

| 7     | 0x01-0x80 保留      | 能力关至允许自定人上口能力     |  |  |

|       | 0x81-0xFF OEM 自定义 |                   |  |  |

| 5     |                   | 格式见表 3-4          |  |  |

| 6     |                   |                   |  |  |

| 7     |                   |                   |  |  |

| 8     | ]<br>· 请求 LTPI 能力 |                   |  |  |

| 9     | 頃水 LIFI 配力<br>    |                   |  |  |

| 10    |                   |                   |  |  |

| 11    |                   |                   |  |  |

| 12    |                   |                   |  |  |

| 13-14 | 保留                | 保留                |  |  |

| 15    | CRC               | CRC8 checksum     |  |  |

#### c. LTPI Accept Frame

HPM 接收到了 Configure 帧之后,会与本地能力进行对比,如果本地能力包含 Configure 帧内所描述的能力,则发送 Accept 帧。Accept 帧与 Configure 帧格式一致。接受 LTPI 能力和请求 LTPI 能力部分内容一致。

#### 表 4-16 Accept 帧定义

| 帧内字节 | Bit                                                      | 内容     |            |        |     |   | 描述 |   |                   |  |  |  |

|------|----------------------------------------------------------|--------|------------|--------|-----|---|----|---|-------------------|--|--|--|

| 製    | 7                                                        | 6      | 5          | 4      | 3   | 2 | 1  | 0 | 捆处                |  |  |  |

| 0    | 逗点                                                       | 点符号    | ļ          |        |     |   |    |   | 根据上表定义            |  |  |  |

| 1    | 帧类                                                       | 类型     |            |        |     |   |    |   | 根据上表定义            |  |  |  |

| 2    | Plat                                                     | tform  | <b>光</b> 刑 |        |     |   |    |   | _                 |  |  |  |

| 3    | ı ıa                                                     |        | 大土         |        |     |   |    |   |                   |  |  |  |

| 4    | 能力类型<br>0x00 默认能力类型<br>0x01-0x80 保留<br>0x81-0xFF OEM 自定义 |        |            |        |     |   |    |   | 能力类型允许自定义 LTPI 能力 |  |  |  |

| 5    | UXO                                                      | I -UXI | -          | ⊏IVI ⊧ | コルメ |   |    |   |                   |  |  |  |

| 6    |                                                          |        |            |        |     |   |    |   |                   |  |  |  |

| 7    |                                                          |        |            |        |     |   |    |   |                   |  |  |  |

| 8    | 接受 LTPI 能力                                               |        |            |        |     |   |    |   | 格式见表 3-4          |  |  |  |

| 9    |                                                          |        |            |        |     |   |    |   |                   |  |  |  |

| 10   |                                                          |        |            |        |     |   |    |   |                   |  |  |  |

| 11   |                                                          |        |            |        |     |   |    |   |                   |  |  |  |

| 12   |                                                          |        |            |        |     |   |    |   |                   |  |  |  |

IPUG1086-1.0 29(46)

**4** 设计说明 **4.4LTPI** 帧格式

| 帧内字节  | Bit 内容 | 描述            |

|-------|--------|---------------|

| 13-14 | 保留     | 保留            |

| 15    | CRC    | CRC8 checksum |

SCM 收到 Accept 帧之后,开始进入运行阶段,发送 Operation 帧,而 HPM 收到 SCM 发来的 Operation 帧后进入运行阶段。

#### 3. 运行阶段

当 SCM 和 HPM 都进入了 operation 状态时,开始发送运行帧。

运行帧有三种,一种是默认 I/O 帧,一种是默认数据帧,还有 OEM 自定义帧,如表 4-17 所示。当前的 IP 只支持默认 I/O 帧和默认数据帧。

#### 表 4-17 运行阶段帧类型

| 帧类型          | 逗点符号  | 帧类型值      |

|--------------|-------|-----------|

| Default I/O  |       | 0x00      |

| Default Data | K28.7 | 0x01      |

| Reserved     | N20.1 | 0x02-0x0F |

| OEM Defined  |       | 0x10-0xFF |

当没有使能 Data 通道的时候,则只有 Default I/O 帧, LTPI Default I/O Frame。

#### a. LTPI Default I/O Frame

该帧传输 GPIO/UART/IIC/OEM 等通道的信息,具体定义如表 4-18 所示。

#### 表 4-18 Default I/O 帧定义

| 帧内字节  | Bit 内容 |               |      |    |   |   |   | - 描述     |                      |

|-------|--------|---------------|------|----|---|---|---|----------|----------------------|

|       | 7      | 6             | 5    | 4  | 3 | 2 | 1 | 0        | · 加处                 |

| 0     | 逗      | 点符            | 号    |    |   |   |   |          | 根据上表定义               |

| 1     | 帧      | 类型            |      |    |   |   |   |          | 根据上表定义               |

| 2     | 帧      | 计数            | 器    |    |   |   |   |          | 帧计数器用于解码 NL GPIO 的位置 |

| 3     | 低      | 延迟            | GPIC | 00 |   |   |   |          | 定义见表 4-2             |

| 4     | 低      | 低延迟 GPIO1     |      |    |   |   |   |          | 定义见表 4-2             |

| 5     | 正      | 正常延迟 GPIO0    |      |    |   |   |   |          | 定义见表 4-2             |

| 6     | 正      | 正常延迟 GPIO1    |      |    |   |   |   |          | 定义见表 4-2             |

| 7     | UA     | UART0 和 UART1 |      |    |   |   |   |          | 定义见表 4-3             |

| 8     | IIC    | IIC0 和 IIC1   |      |    |   |   |   |          | 定义见表 4-5             |

| 9     | IIC    | IIC2 和 IIC3   |      |    |   |   |   |          | 定义见表 4-5             |

| 10    | IIC    | IIC4 和 IIC5   |      |    |   |   |   | 定义见表 4-5 |                      |

| 11-14 | OE     | OEM 保留        |      |    |   |   |   |          | OEM 保留               |

| 15    | CF     | RC            |      |    |   |   |   |          | CRC8 checksum        |

IPUG1086-1.0 30(46)

#### b. LTPI Default Data Frame

该帧用于传送总线数据,具体定义如表 4-19 所示。

表 4-19 Default Data 帧定义

| 帧内字节    | Bit | 内容          |     |   |   |   |        | 描述       |               |

|---------|-----|-------------|-----|---|---|---|--------|----------|---------------|

| 製 内 于 1 | 7   | 6           | 5   | 4 | 3 | 2 | 1      | 0        | 加处            |