# Gowin EDP Encoder Decoder IP 用户指南

IPUG1179-2.1,2024-06-07

#### 版权所有 © 2024 广东高云半导体科技股份有限公司

GO₩IN富云、₩、Gowin、GowinSynthesis、云源以及高云均为广东高云半导体科技股份有限公司注册商标,本手册中提到的其他任何商标,其所有权利属其拥有者所有。未经本公司书面许可,任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部,并不得以任何形式传播。

#### 免责声明

本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止反言或其它方式授予任何知识产权许可。除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。高云半导体不承诺对这些文档进行适时的更新。

## 版本信息

| 日期         | 版本  | 说明                                                                    |  |

|------------|-----|-----------------------------------------------------------------------|--|

| 2023/12/13 | 1.0 | 7始版本。                                                                 |  |

| 2024/02/23 | 1.1 | 更新参数。                                                                 |  |

| 2024/03/29 | 2.0 | IP 名称更新为 EDP Encoder Decoder; 更新 EDP Encoder 端口参数计算描述; 更新界面截图。        |  |

| 2024/06/07 | 2.1 | <ul><li>更新 EDP Decoder 端口;</li><li>新增边带控制描述;</li><li>更新时序图。</li></ul> |  |

i

## 目录

| 目 | 录                      | i   |

|---|------------------------|-----|

| 图 | ]目录                    | iii |

| 表 | 是目录                    | iv  |

| 1 | 关于本手册                  | . 1 |

|   | 1.1 手册内容               | 1   |

|   | 1.2 相关文档               | 1   |

|   | 1.3 术语、缩略语             | 1   |

|   | 1.4 技术支持与反馈            | 2   |

| 2 | 概述                     | . 3 |

|   | 2.1 概述                 | 3   |

|   | 2.2 主要特征               | 3   |

|   | 2.3 资源利用               | 4   |

| 3 | 功能描述                   | . 5 |

|   | 3.1 系统框图               | 5   |

|   | 3.2 结构框图               | 5   |

|   | 3.3 工作原理               | 6   |

|   | 3.3.1 主链路数据封包解包        | 6   |

|   | 3.3.2 边带控制             | 12  |

|   | 3.4 端口列表               | 13  |

|   | 3.4.1 EDP Encoder 端口   | 13  |

|   | 3.4.2 EDP Decoder 端口   | 17  |

|   | 3.5 参数配置               | 22  |

|   | 3.5.1 EDP Encoder 参数   | 22  |

|   | 3.5.2 EDP Decoder 参数   | 22  |

|   | 3.6 时序说明               | 23  |

|   | 3.7 EDP Encoder 端口参数计算 | 25  |

| 4 | 界面配置                   | 28  |

|   | 4.1 EDP Encoder IP 配置 | 28 |

|---|-----------------------|----|

|   | 4.2 EDP Decoder IP 配置 | 31 |

| 5 | 参考设计                  | 34 |

| 6 | 件交付                   | 35 |

|   | 6.1 文档                | 35 |

|   | 6.2 设计源代码 (加密)        | 35 |

|   | 6.3 参考设计              | 35 |

## 图目录

| 图 | 3-1 系统框图                           | 5  |

|---|------------------------------------|----|

| 图 | 3-2 结构框图                           | 5  |

| 图 | 3-3 DP 数据传输通道                      | 6  |

| 图 | 3-4 视频流数据封包格式示意图                   | 8  |

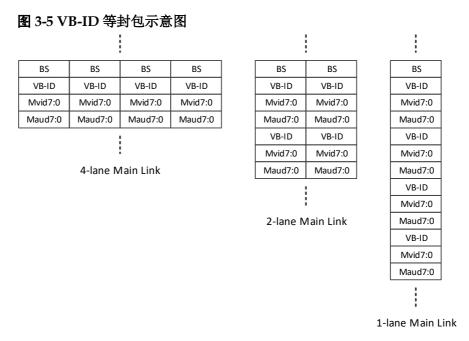

| 图 | 3-5 VB-ID 等封包示意图                   | 9  |

| 图 | 3-6 Transfer Unit 示意图              | 9  |

| 图 | 3-7 MSA 传输示意图                      | 10 |

| 图 | 3-8 通道歪斜示意图                        | 11 |

| 图 | 3-9 辅助通道差分信号                       | 12 |

| 图 | 3-10 eDP 辅助通道差分信号                  | 12 |

| 图 | 3-11 EDP Encoder IO 端口示意图          | 13 |

| 图 | 3-12 EDP Decoder IO 端口示意图          | 17 |

| 图 | 3-13 EDP Encoder 视频接口时序示意图(2lanes) | 23 |

| 图 | 3-14 EDP Encoder 输出接口时序示意图(2lanes) | 23 |

| 图 | 3-15 EDP Decoder 输入接口时序示意图(2lanes) | 24 |

| 图 | 3-16 EDP Decoder 输出接口时序示意图(2lanes) | 24 |

| 图 | 4-1 打开 IP Core Generator           | 28 |

| 图 | 4-2 打开 EDP Encoder IP 核            | 29 |

| 图 | 4-3 EDP Encoder IP 核接口示意图          | 29 |

| 图 | 4-4 基本信息配置界面                       | 30 |

| 图 | 4-5 Options 选项卡                    | 30 |

| 图 | 4-6 打开 IP Core Generator           | 31 |

| 图 | 4-7 打开 EDP Decoder IP 核            | 32 |

| 图 | 4-8 EDP Decoder IP 核接口示意图          | 32 |

| 图 | 4-9 基本信息配置界面                       | 33 |

| 图 | 4-10 Options 选项卡                   | 33 |

| 图 | 5-1 参考设计实例一基本结构框图                  | 34 |

## 表目录

| 表 1-1 术语、缩略语                       | 1  |

|------------------------------------|----|

| 表 2-1 Gowin EDP Encoder Decoder IP | 3  |

| 表 2-2 EDP Encoder 占用资源             | 4  |

| 表 2-3 EDP Decoder 占用资源             | 4  |

| 表 3-1 主链路的像素填充                     | 6  |

| 表 3-2 K 码与控制符号对应关系                 | 7  |

| 表 3-3 普通帧模式与增强帧模式控制符号差别            | 7  |

| 表 3-4 Gowin EDP Encoder IP 的端口列表   | 14 |

| 表 3-5 Gowin EDP Decoder IP 的端口列表   | 18 |

| 表 3-6 EDP Encoder 参数               | 22 |

| 表 3-7 EDP Decoder 参数               | 22 |

| 表 6-1 文档列表                         | 35 |

| 表 6-2 Gowin EDP Encoder 设计源代码列表    | 35 |

| 表 6-3 Gowin EDP Decoder 设计源代码列表    | 35 |

| 表 6-4 Gowin FDP RefDesign 文件夹内容列表  | 35 |

#

## 1.1 手册内容

Gowin EDP Encoder Decoder IP 用户指南主要内容包括产品概述、功能描述、配置调用、参考设计等,旨在帮助用户快速了解 Gowin EDP Encoder Decoder IP 的特性及使用方法。本手册中的软件界面截图参考的是V1.9.9.03 (64-bit)版本,因软件版本升级,部分信息可能会略有差异,具体以用户软件版本的信息为准。

## 1.2 相关文档

通过登录高云半导体网站 <u>www.gowinsemi.com.cn</u> 可以下载、查看以下相关文档:

- DS981, GW5AT 系列 FPGA 产品数据手册

- DS1104, GW5AST 系列 FPGA 产品数据手册

- SUG100, Gowin 云源软件用户指南

## 1.3 术语、缩略语

本手册中出现的相关术语、缩略语及相关释义如表 1-1 所示。

#### 表 1-1 术语、缩略语

| 术语、缩略语 | 全称                              | 含义       |

|--------|---------------------------------|----------|

| AUX CH | Auxiliary Channel               | 辅助通道     |

| DE     | Data Enable数据使能                 |          |

| DP     | DisplayPort 显示端口                |          |

| EDP    | Embedded DisplayPort            | 嵌入式显示端口  |

| FPGA   | Field Programmable Gate Array   | 现场可编程门阵列 |

| HPD    | Hot Plug Detect                 | 热插拔检测    |

| HS     | Horizontal Sync                 | 水平同步     |

| IP     | Intellectual Property           | 知识产权     |

| RGB    | R(Red) G(Green) B(Blue)         | 红绿蓝颜色空间  |

| SerDes | Serializer/Deserializer 串行器/解串器 |          |

IPUG1179-2.1 1(36)

| 术语、缩略语 | 全称                                      | 含义       |

|--------|-----------------------------------------|----------|

| TU     | Transfer Unit                           | 传输单元     |

| VESA   | Video Electronics Standards Association | 视频电子标准协会 |

| VS     | Vertical Sync                           | 垂直同步     |

## 1.4 技术支持与反馈

高云半导体提供全方位技术支持,在使用过程中如有任何疑问或建议,可直接与公司联系:

网址: www.gowinsemi.com.cn

E-mail: <a href="mailto:support@gowinsemi.com">support@gowinsemi.com</a>

Tel: +86 755 8262 0391

IPUG1179-2.1 2(36)

2 概述 2.1 概述

# 2概述

## 2.1 概述

DisplayPort (DP) 是一个由 PC 及芯片制造商联盟开发,视频电子标准协会 (VESA) 标准化的数字式视频接口标准。该接口免认证、免授权金,主要用于视频源与显示器等设备的连接,并也支持携带音频、USB 和其他形式的数据。

eDP(Embedded DisplayPort)协议是针对 DP 应用在嵌入式方向架构和协议的拓展,所以 eDP 协议完全兼容 DP 协议。EDP 多用做平板,笔记本电脑的液晶显示屏的接口。

EDP Encoder IP 用于接收并行视频信号,然后根据 eDP 协议编码后输出给 SerDes 串行化。EDP Decoder IP 用于接收经 SerDes 解串后的数据,然后根据 eDP 协议解码成并行信号。

| 表 2-1 Gowin EDP Encoder Decoder II | 表 2-1 | Gowin | <b>EDP</b> | Encoder | Decoder | IP |

|------------------------------------|-------|-------|------------|---------|---------|----|

|------------------------------------|-------|-------|------------|---------|---------|----|

| Gowin EDP Encoder Decoder IP            |                     |  |

|-----------------------------------------|---------------------|--|

| 逻辑资源                                    | 请参见表 2-2 和表 2-3。    |  |

| 交付文件                                    |                     |  |

| 设计文件                                    | Verilog (encrypted) |  |

| 参考设计                                    | Verilog             |  |

| TestBench                               | Verilog             |  |

| 测试设计流程                                  |                     |  |

| 综合软件                                    | GowinSynthesis      |  |

| 应用软件 Gowin Software (V1.9.9(64-bit)及以上) |                     |  |

#### 注!

可登录高云半导体网站查看芯片支持信息。

## 2.2 主要特征

- 可配置为 1, 2, or 4 lanes

- 支持 8B10B 编解码功能

- 支持 Word Alignment 功能

IPUG1179-2.1 3(36)

2 概述 2.3 资源利用

- Link rate 支持 1.62/2.7/5.4 Gbps/lane

- 支持用户数据位宽 16/32

## 2.3 资源利用

通过 Verilog 语言实现 EDP Encoder 和 Decoder。因使用器件的密度、速度和等级不同,其性能和资源利用情况可能不同。以高云 GW5AST 系列 FPGA 为例,EDP Encoder 和 Decoder 资源利用情况如表 2-2 和表 2-3 所示。

#### 表 2-2 EDP Encoder 占用资源

| 器件系列       | 速度等级  | 器件名称  | 资源利用 | 备注                       |

|------------|-------|-------|------|--------------------------|

|            |       | LUT   | 2258 |                          |

| GW5AST-138 | C1/I0 | REG   | 1963 | 4 lanes,<br>5.4Gbps/lane |

|            |       | BSRAM | 32   | 0.4 <b>0</b> 5p5/10110   |

#### 表 2-3 EDP Decoder 占用资源

| 器件系列       | 速度等级  | 器件名称  | 资源利用 | 备注                       |

|------------|-------|-------|------|--------------------------|

|            |       | LUT   | 5059 |                          |

| GW5AST-138 | C1/I0 | REG   | 5140 | 4 lanes,<br>5.4Gbps/lane |

|            |       | BSRAM | 0    | 0.400ps/lane             |

IPUG1179-2.1 4(36)

**3** 功能描述 3.1 系统框图

# 3功能描述

## 3.1 系统框图

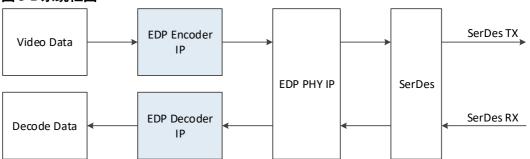

Gowin EDP Encoder Decoder IP 分为 EDP Encoder IP 和 EDP Decoder IP, 其系统框图如图 3-1 所示。

#### 图 3-1 系统框图

## 3.2 结构框图

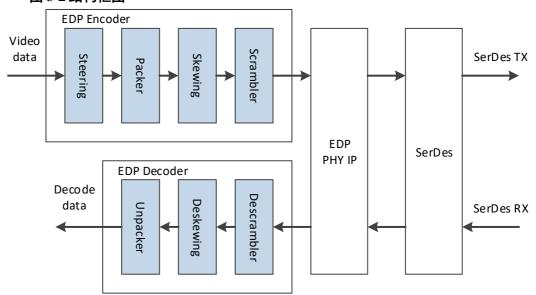

#### 图 3-2 结构框图

IPUG1179-2.1 5(36)

EDP Encoder IP 主要包括数据引导模块、组包模块、偏移模块和扰码模块。EDP Decoder IP 主要包括数据解扰码模块、解偏移模块和解包模块。

## 3.3 工作原理

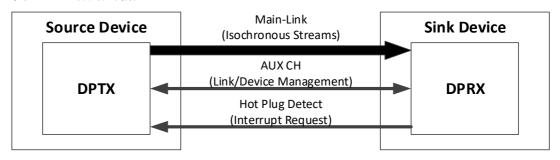

根据 Display Port Version1.4 协议,如图 3-3 所示,完整的 DP 收发控制器大体可分成两大部分:

- 1. 主链路部分(Main-Link),包括链路数据封包解包,SerDes 物理层

- 2. 边带控制部分(AUX CH+HPD),包括链路层管理,辅助通道,热插拔检测

#### 图 3-3 DP 数据传输通道

Gowin EDP Encoder Decoder IP 只涉及主链路部分的链路数据封包解包。

注!

本手册简要介绍 DP 协议相关术语和定义,详细信息请参考 DisplayPort Version1.4 协议。

### 3.3.1 主链路数据封包解包

#### 引导模块

根据 DP 协议主链路可支持 1,2 或 4 lanes。无论视频流的颜色空间和像素位深度如何,依照表 3-1 进行像素数据的填充。

#### 表 3-1 主链路的像素填充

| # of Lanes                                  | Pixel Steering                                                                    |  |  |

|---------------------------------------------|-----------------------------------------------------------------------------------|--|--|

| One                                         | All pixels to Lane 0                                                              |  |  |

| Two Pixel 2N to Lane 0 Pixel 2N+1 to Lane 1 |                                                                                   |  |  |

| Four                                        | Pixel 4N to Lane 0 Pixel 4N+1 to Lane 1 Pixel 4N+2 to Lane 2 Pixel 4N+3 to Lane 3 |  |  |

EDP Encoder IP 根据主链路通道数决定视频输入数据位宽。主链路为 1 lane, 视频输入数据为 24 bits, 单像素模式, 即每个像素时钟传输 1 个像素。主链路为 2 lanes, 视频输入数据为 48 bits, 双像素模式, 即每个像素时钟传输 2 个像素。主链路为 4 lanes, 视频输入数据为 96 bits, 四像素模式,

IPUG1179-2.1 6(36)

即每个像素时钟传输4个像素。

#### 组包与解包模块

根据 DP 协议,以下控制符号用于组帧。

- BS: Blanking Start,视频消隐开始标志

- BE: Blanking End,视频消隐结束标志,每行第一个有效视频前插入

- FS: Fill Start,填充数据开始标志

- FE: Fill End,填充数据结束标志

- SS: Secondary-data Start,第二数据填充开始标志

- SE: Secondary-data End,第二数据填充结束标志

- SR: Scrambler Reset, SR symbol 用来复位 LFSR 到初始值

- BF: Blanking Fill, 增强帧模式填充标志 在 ANSI 标准中 8B/10B 特殊 K 码与控制符号对应关系如下表 3-2。

#### 表 3-2 K 码与控制符号对应关系

| Special Character | Control Symbol in Single Stream Enhanced Mode |

|-------------------|-----------------------------------------------|

| K28.0             | SR                                            |

| K28.1             | CP                                            |

| K28.2             | SS                                            |

| K28.3             | BF                                            |

| K28.5             | BS                                            |

| K23.7             | FE                                            |

| K27.7             | BE                                            |

| K29.7             | SE                                            |

| K30.7             | FS                                            |

根据 DP 协议, 普通帧模式与增强帧模式控制符号差别如下表 3-3。

#### 表 3-3 普通帧模式与增强帧模式控制符号差别

| Default Framing Mode Symbols                    | Enhanced Framing Mode Symbols |

|-------------------------------------------------|-------------------------------|

| BS                                              | BS+BF+BF+BS                   |

| SR                                              | SR+BF+BF+SR                   |

| CPBS(called CP symbol in Enahnced Framing Mode) | BS+CP+CP+BS                   |

| CPSR(called BF symbol in Enahnced Framing Mode) | SR+CP+CP+SR                   |

| BE                                              | BE(no change)                 |

| FS                                              | FS(no change)                 |

| FE                                              | FE(no change)                 |

| SS                                              | SS(no change)                 |

| SE                                              | SE(no change)                 |

IPUG1179-2.1 7(36)

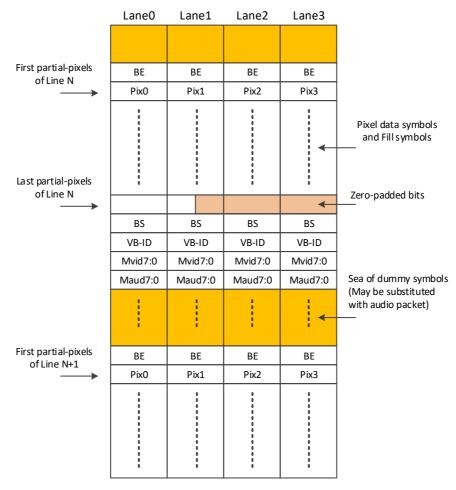

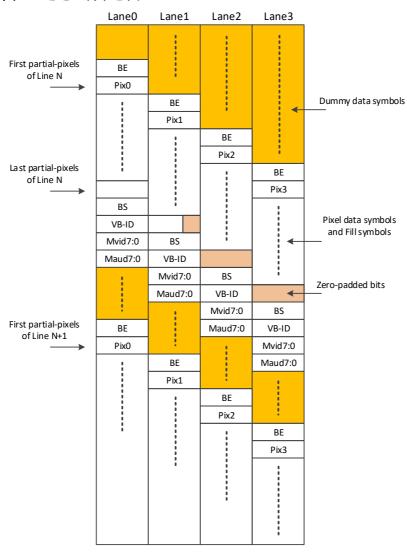

视频流数据封包格式如图 3-4 所示。

#### 图 3-4 视频流数据封包格式示意图

每个 lane 的 BS 后必须跟随 VB-ID, Mvid7:0 和 Maud7:0。

无论 lane 数量是多少, VB-ID,Mvid7:0 和 Maud7:0 必须传输 4 次, 如图 3-5 所示。

IPUG1179-2.1 8(36)

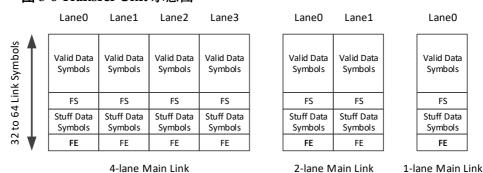

为避免链路带宽过载,数据打包速率(packed data rates)必须小于等于链路符号速率(link symbols rates)。当打包数据率低于链路符号率时,链路层必须执行符号填充(Symbols stuffing)。

符号填充由 stuffing frame symbols 和 dummy data symbols 组成。 Stuffing frame symbols 由 FS 和 FE 构成,位于每个 TU (Transfer Unit)之内, dummy data symbols 在扰码之前必须是 0x00,插在 FS 和 FE 之间,如图 3-6 所示。

Transfer Unit 的大小必须介于每 lane 32~64 个符号。

每行视频数据最后一个 TU 不填充 FS 和 FE。

#### 图 3-6 Transfer Unit 示意图

主视频流属性数据 Main Stream Attribute(MSA)在主视频流的垂直消隐期间每帧发送一次。属性数据包括以下:

- 1. 用于视频流时钟恢复的 M 和 N 值(24bits each)

- 2. 水平总点数和垂直总行数(16bits each)

- 3. 水平有效开始点数和垂直有效开始行数(16bits each)

- 4. 水平和垂直同步信号极性和宽度(1 bit for polarity and 15 bits for width)

IPUG1179-2.1 9(36)

- 5. 水平有效点数和垂直有效行数(16bits each)

- 6. 杂项 0(MISC0, 8bits)

- 7. 杂项 1(MISC1, 8bits)

通过每 lane 发送 2 个连续的"SS"符号,将主流属性数据包与第二数据包区分开来,如图 3-7 所示。

#### 图 3-7 MSA 传输示意图

| Lane0       | Lane1       | Lane2       | Lane3     |

|-------------|-------------|-------------|-----------|

| SS          | SS          | SS          | SS        |

| SS          | SS          | SS          | SS        |

| Mvid23:16   | Mvid23:16   | Mvid23:16   | Mvid23:16 |

| Mvid15:8    | Mvid15:8    | Mvid15:8    | Mvid15:8  |

| Mvid7:0     | Mvid7:0     | Mvid7:0     | Mvid7:0   |

| Htotal15:8  | Hstart15:8  | Hwidth15:8  | Nvid23:16 |

| Htotal7:0   | Hstart7:0   | Hwidth7:0   | Nvid15:8  |

| Vtotal15:8  | Vstart15:8  | Vheight15:8 | Nvid7:0   |

| Vtotal7:0   | Vstart7:0   | Vheight7:0  | MISC0_7:0 |

| HSP HSW14:8 | VSP VSW14:8 | All 0s      | MIS1_7:0  |

| HSW7:0      | VSW7:0      | All 0s      | All Os    |

| SE          | SE          | SE          | SE        |

|             |             |             |           |

4-lane Main Link

HSW = Hsync Width HSP = Hsync Ploarity VSW = Vsync Width VSP = Vsync Ploarity

| Lane0       | Lane1       |

|-------------|-------------|

| SS          | SS          |

| SS          | SS          |

| Mvid23:16   | Mvid23:16   |

| Mvid15:8    | Mvid15:8    |

| Mvid7:0     | Mvid7:0     |

| Htotal15:8  | Hstart 15:8 |

| Htotal7:0   | Hstart7:0   |

| Vtotal15:8  | Vstart15:8  |

| Vtotal7:0   | Vstart7:0   |

| HSP HSW14:8 | VSP VSW14:8 |

| HSW7:0      | VSW7:0      |

| Mvid23:16   | Mvid23:16   |

| Mvid15:8    | Mvid15:8    |

| Mvid7:0     | Mvid7:0     |

| Hwidth15:8  | Nvid23:16   |

| Hwidth7:0   | Nvid15:8    |

| Vheight15:8 | Nvid7:0     |

| Vheight7:0  | MISC0_7:0   |

| All 0s      | MIS1_7:0    |

| All 0s      | All 0s      |

| SE          | SE          |

|             |             |

2-lane Main Link

Htotal15:8 Htotal7:0 Vtotal15:8 Vtotal7:0 HSP|HSW14:8 HSW7:0 Mvid23:16 Mvid15:8 Mvid7:0 Hstart15:8 Hstart 7:0 Vstart15:8 Vstart7:0 VSP|VSW14:8 VSW7:0 Mvid23:16 Mvid15:8 Mvid7:0 Hwidth15:8 Hwidth7:0 Vheight15:8 Vheight7:0 All 0s All 0s Mvid23:16 Mvid15:8 Mvid7:0 Nvid23:16 Nvid15:8 Nvid7:0 MISC0\_7:0 MIS1\_7:0 All 0s

SE

SS

SS

Mvid23:16

Mvid15:8

Mvid7:0

### 偏移与解偏移模块

相邻 lane 必须插入 2 个链路时钟 LS\_Clk 歪斜,目的是提高链路对外部噪声的抗干扰能力,如图 3-8 所示。

IPUG1179-2.1 10(36)

#### 图 3-8 通道歪斜示意图

#### 扰码与解扰码模块

为了减少 EMI,在 8B/10B 编码之前,需进行扰码。16-bit LFSR 的多项式为  $G(X) = X^{16} + X^5 + X^4 + X^3 + 1$ 。数据的每个字节都使用 LFSR 的最高有效 8 位以相反的位顺序进行加扰/解扰。

$\begin{aligned} &\{D'[7],\,D'[6],\,D'[5],\,D'[4],\,D'[3],\,D'[2],\,D'[1],\,D'[0]\} = \{\,D[7],\,D[6],\,D[5],\\ &D[4],\,D[3],\,D[2],\,D[1],\,D[0]\} \land \{LFSR[8],\,LFSR[9],\,LFSR[10],\,LFSR[11],\\ &LFSR[12],\,LFSR[13],\,LFSR[14],\,LFSR[15]\} \end{aligned}$

SR 符号或 SR BF BF SR 符号序列被用于复位 LFSR 至初始值 FFFFh (或在 eDP 标准下初始值为 FFFEh)。

IPUG1179-2.1 11(36)

#### 3.3.2 边带控制

#### 热插拔检测

热插拔检测(HPD)信号是由终端向源端发出的中断请求信号,这是一个单向信号,高有效,当源端检测的此信号为高的时候表示有终端设备连接,如果为低则表示没有终端设备连接。热插拔检测信号 IO 电平标准为 3.3V。

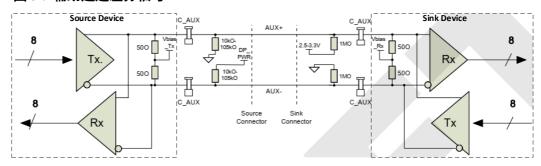

#### 辅助通道

辅助通道(AUX CH)是 DP 接口中一条独立的双向传输辅助通道,采用交流耦合差分传输方式,是一条双向半双工传输通道,速率为 1Mbps,采用曼彻斯特 II 编码,用来传输控制指令。辅助通道 IO 电平标准推荐 1.8V。

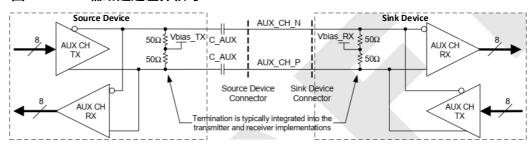

如果作为 DP 接口通过线缆连接,外部电路推荐如图 3-9 所示。

#### 图 3-9 辅助通道差分信号

如果作为 eDP 接口在板内连接,外部电路推荐如图 3-10 所示。

#### 图 3-10 eDP 辅助通道差分信号

IPUG1179-2.1 12(36)

**3** 功能描述 **3.4** 端口列表

## 3.4 端口列表

## 3.4.1 EDP Encoder 端口

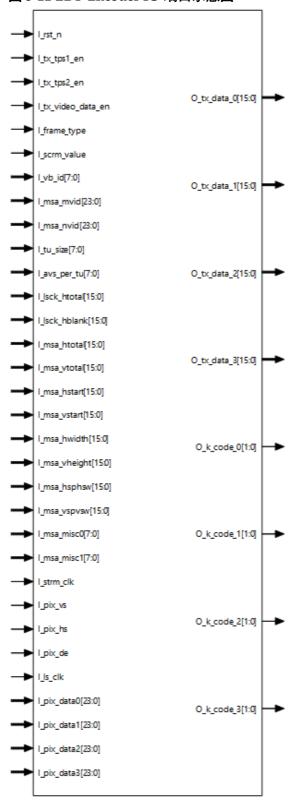

Gowin EDP Encoder IP 的 IO 端口如图 3-11 所示。

#### 图 3-11 EDP Encoder IO 端口示意图

IPUG1179-2.1 13(36)

根据配置参数不同,端口会略有不同。

Gowin EDP Encoder IP 的 IO 端口详细描述如表 3-4 所示。

表 3-4 Gowin EDP Encoder IP 的端口列表

|    | sowin EDF Encouer if | HUPPUR                                 | /11/C                                   |                |  |

|----|----------------------|----------------------------------------|-----------------------------------------|----------------|--|

| 序号 | 信号名称                 | 方向                                     | 描述                                      | 备注             |  |

| 1  | I_rst_n              | 1                                      | 复位信号, 低有效。                              | 所有信号输          |  |

| 2  | I_tx_tps1_en         | I                                      | TPS1训练数据使能                              | 入输出方向<br>均以EDP |  |

|    |                      |                                        | 参数Training Pattern TPS1                 | Encoder IP     |  |

| 3  | I_tx_tps2_en         | 1                                      | Enable为Yes时有效 TPS2训练数据使能                | 为参考。           |  |

| 3  | 1_tX_tpsz_en         | '                                      | 参数Training Pattern TPS2                 |                |  |

|    |                      |                                        | Enable为Yes时有效                           |                |  |

| 4  | I_tx_video_data_en   | I                                      | 发送视频数据使能                                |                |  |

| 5  | I_frame_type         | 1                                      | 帧类型控制信号                                 |                |  |

|    |                      |                                        | 0: 普通帧                                  |                |  |

|    |                      |                                        | 1: 增强帧                                  |                |  |

| 6  | I_scrm_value         | I                                      | 扰码复位初始值控制信号                             |                |  |

|    |                      |                                        | 0: 复位初始值0xFFFF                          |                |  |

| 7  | 1 .4- :4             |                                        | 1: 复位初始值0xFFFE                          |                |  |

| 7  | I_vb_id              | 1                                      | VB-ID参数                                 |                |  |

| 8  | I_msa_mvid           | 1                                      | MSA中Mvid参数                              |                |  |

| 9  | I_msa_nvid           | 1                                      | MSA中Nvid参数                              |                |  |

| 10 | I_tu_size            | I                                      | TU大小参数,范围32~64                          |                |  |

|    |                      | User Clock Ratio 为 1:20 时,<br>须为 2 的倍数 |                                         |                |  |

|    |                      |                                        | User Clock Ratio为1:40时,必<br>须为4的倍数      |                |  |

| 11 | I_avs_per_tu         | I                                      | 每TU平均有效数据参数,范围                          |                |  |

|    |                      |                                        | 小于等于(I_tu_size-2)                       |                |  |

|    |                      |                                        | User Clock Ratio 为 1:20 时,必<br>须为 2 的倍数 |                |  |

|    |                      |                                        | User Clock Ratio为1:40时,必                |                |  |

|    |                      |                                        | 须为4的倍数                                  |                |  |

| 12 | I_lsck_htotal        | I                                      | 链路时钟域一行总时钟数                             |                |  |

| 13 | I_lsck_hblank        | 1                                      | 链路时钟域一行消隐时钟数                            |                |  |

| 14 | I_msa_htotal         | I                                      | MSA中水平总点数参数                             |                |  |

| 15 | I_msa_vtotal         | 1                                      | MSA中垂直总行数参数                             |                |  |

| 16 | I_msa_hstart         | 1                                      | MSA中水平有效开始点数参数                          |                |  |

| 17 | I_msa_vstart         | I                                      | MSA中垂直有效开始行数参数                          |                |  |

| 18 | I_msa_hwidth         | 1                                      | MSA中水平有效点数参数                            |                |  |

| 19 | I_msa_vheight        | 1                                      | MSA中垂直有效行数参数                            |                |  |

| 20 | I_msa_hsphsw         | I                                      | MSA中水平同步信号极性和宽                          |                |  |

IPUG1179-2.1 14(36)

| 序号    | 信号名称           | 方向            | 描述                                                                                                                                              | 备注 |

|-------|----------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| /1, 7 |                | 71 1-1        | 度参数                                                                                                                                             | 田仁 |

|       |                |               | [15]: 同步信号极性,0表示正极性脉冲,1表示负极性脉冲                                                                                                                  |    |

| 21    | I_msa_vspvsw   | 1             | MSA中垂直同步信号极性和宽                                                                                                                                  |    |

| 21    | I_IIIsa_vspvsw | '             | 度参数<br>[15]: 同步信号极性,0表示正极                                                                                                                       |    |

|       |                |               | 性脉冲,1表示负极性脉冲<br>[14:0]: 同步信号宽度                                                                                                                  |    |

| 22    | I_msa_misc0    | 1             | MSA中MISC0参数                                                                                                                                     |    |

|       |                |               | [0]: 0表示链路时钟与视频流时钟异步,1表示链路时钟与视频流时钟同步                                                                                                            |    |

| 23    | I_msa_misc1    | 1             | MSA中MISC1参数                                                                                                                                     |    |

| 24    | I_strm_clk     | I             | 输入视频流时钟                                                                                                                                         |    |

| 25    | I_pix_vs       | I             | 输入视频流场同步信号                                                                                                                                      |    |

| 26    | I_pix_de       | I             | 输入视频流数据有效信号                                                                                                                                     |    |

| 27    | I_ls_clk       | I             | 输入链路时钟                                                                                                                                          |    |

| 28    | I_pix_data0    | 1             | 输入视频流数据0,格式{B,G,R}<br>若Double Pixels Per Lane参数<br>为Yes,则数据格式为                                                                                  |    |

|       |                |               | $\{B_1,G_1,R_1,B_0,G_0,R_0\}$                                                                                                                   |    |

| 29    | I_pix_data1    | l 输入视频流数据1,格式 |                                                                                                                                                 |    |

|       |                |               | {B,G,R},链路为2/4 lane时支持                                                                                                                          |    |

|       |                |               | 若Double Pixels Per Lane参数<br>为Yes,则数据格式为                                                                                                        |    |

|       |                |               | { B <sub>1</sub> ,G <sub>1</sub> ,R <sub>1</sub> , B <sub>0</sub> ,G <sub>0</sub> ,R <sub>0</sub> }                                             |    |

| 30    | I_pix_data2    | I             | 输入视频流数据2,格式<br>{B,G,R},链路为4 lane时支持                                                                                                             |    |

|       |                |               | 若Double Pixels Per Lane参数<br>为Yes,则数据格式为<br>{ B <sub>1</sub> ,G <sub>1</sub> ,R <sub>1</sub> , B <sub>0</sub> ,G <sub>0</sub> ,R <sub>0</sub> } |    |

| 31    | I_pix_data3    | I             | 输入视频流数据3,格式<br>{B,G,R},链路为4 lane时支持                                                                                                             |    |

|       |                |               | 若Double Pixels Per Lane参数<br>为Yes,则数据格式为<br>{ B <sub>1</sub> ,G <sub>1</sub> ,R <sub>1</sub> , B <sub>0</sub> ,G <sub>0</sub> ,R <sub>0</sub> } |    |

| 32    | O_tx_data_0    | 0             | 输出链路数据0                                                                                                                                         |    |

|       |                |               | User Clock Ratio 为 1:20 时, 位<br>宽 16 bits                                                                                                       |    |

|       |                |               | User Clock Ratio为1:40时,位<br>宽32 bits                                                                                                            |    |

| 33    | O_tx_data_1    | 0             | 输出链路数据1,链路为2/4 lane<br>时支持                                                                                                                      |    |

IPUG1179-2.1 15(36)

| 序号    | 信号名称        | 方向                                                                                                              | 描述                                                                                                           | 备注     |

|-------|-------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------|

| 7,1 3 | III O'SLIM  | × 1.4                                                                                                           | User Clock Ratio 为 1:20 时, 位<br>宽 16 bits<br>User Clock Ratio为1:40时, 位<br>宽32 bits                           | H 1.L. |

| 34    | O_tx_data_2 | O 输出链路数据2,链路为4 lane<br>时支持<br>User Clock Ratio 为 1:20 时,位<br>宽 16 bits<br>User Clock Ratio为1:40时,位<br>宽32 bits  |                                                                                                              |        |

| 35    | O_tx_data_3 | 0                                                                                                               | 输出链路数据3,链路为4 lane<br>时支持<br>User Clock Ratio 为 1:20 时,位<br>宽 16 bits<br>User Clock Ratio为1:40时,位<br>宽32 bits |        |

| 36    | O_k_code_0  | 0                                                                                                               | 输出链路K码标志0<br>User Clock Ratio 为 1:20 时,位<br>宽 2 bits<br>User Clock Ratio为1:40时,位<br>宽4 bits                  |        |

| 37    | O_k_code_1  | O 输出链路K码标志1,链路为2/4<br>lane时支持<br>User Clock Ratio 为 1:20 时,位<br>宽 2 bits<br>User Clock Ratio为1:40时,位<br>宽4 bits |                                                                                                              |        |

| 38    | O_k_code_2  | O 输出链路K码标志2,链路为4 lane时支持 User Clock Ratio 为 1:20 时, 位宽 2 bits User Clock Ratio为1:40时, 位宽4 bits                  |                                                                                                              |        |

| 39    | O_k_code_3  | 0                                                                                                               | 输出链路K码标志3,链路为4<br>lane时支持<br>User Clock Ratio 为 1:20 时,位<br>宽 2 bits<br>User Clock Ratio为1:40时,位<br>宽4 bits  |        |

#### 注!

Lanes Number 参数为 1 lane 时,输入单像素。Lanes Number 参数为 2 lane 时,输入双像素。Lanes Number 参数为 4 lane 时,输入四像素。

IPUG1179-2.1 16(36)

**3** 功能描述 **3.4** 端口列表

### 3.4.2 EDP Decoder 端口

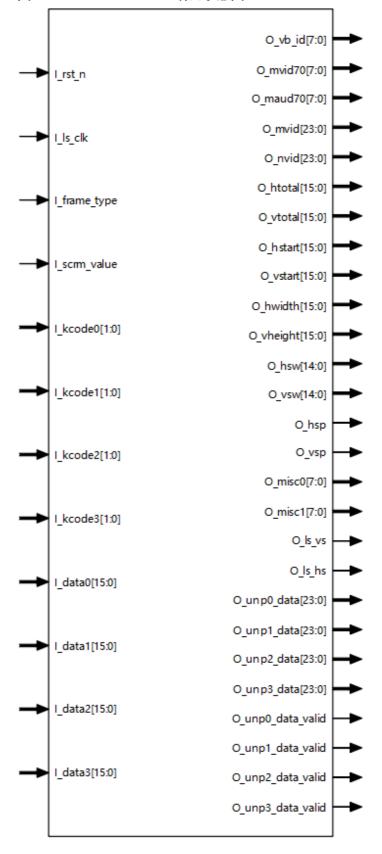

Gowin EDP Decoder IP 的 IO 端口如图 3-12 所示。

#### 图 3-12 EDP Decoder IO 端口示意图

IPUG1179-2.1 17(36)

根据配置参数不同,端口会略有不同。

Gowin EDP Decoder IP 的 IO 端口详细描述如表 3-5 所示。

表 3-5 Gowin EDP Decoder IP 的端口列表

| 序号 | 信号名称         | 方向 | 描述                                            | 备注                    |

|----|--------------|----|-----------------------------------------------|-----------------------|

| 1  | I_rst_n      | 1  | 复位信号, 低有效。                                    | 所有信号输入                |

| 2  | I_ls_clk     | 1  | 输入链路时钟                                        | 输出方向均以<br>EDP Decoder |

| 3  | I_tps1_en    | 1  | TPS1 训练数据使能                                   | IP 为参考。               |

|    |              |    | 参数 Training Pattern TPS1                      |                       |

| 4  | 1 4000 00    | 1  | Enable 为 Yes 时有效                              |                       |

| 4  | I_tps2_en    | I  | TPS2 训练数据使能<br>参数 Training Pattern TPS2       |                       |

|    |              |    | 多数 Halling Fallell 1F32<br>  Enable 为 Yes 时有效 |                       |

| 5  | I_frame_type | 1  | 帧类型控制信号                                       |                       |

|    |              |    | 0: 普通帧                                        |                       |

|    |              |    | 1: 增强帧                                        |                       |

| 6  | I_scrm_value | 1  | 扰码复位初始值控制信号                                   |                       |

|    |              |    | 0: 复位初始值0xFFFF                                |                       |

|    |              |    | 1: 复位初始值 0xFFFE                               |                       |

| 7  | O_vb_id      | 0  | VB-ID参数                                       |                       |

| 8  | O_mvid70     | 0  | MSA中Mvid参数低8位                                 |                       |

| 9  | O_maud70     | 0  | 音频Maud参数低8位                                   |                       |

| 10 | O_mvid       | 0  | MSA 中 Mvid 参数                                 |                       |

| 11 | O_nvid       | 0  | MSA 中 Nvid 参数                                 |                       |

| 12 | O_htotal     | 0  | MSA 中水平总点数参数                                  |                       |

| 13 | O_vtotal     | 0  | MSA 中垂直总行数参数                                  |                       |

| 14 | O_hstart     | 0  | MSA 中水平有效开始点数参数                               |                       |

| 15 | O_vstart     | 0  | MSA 中垂直有效开始行数参数                               |                       |

| 16 | O_hwidth     | 0  | MSA 中水平有效点数参数                                 |                       |

| 17 | O_vheight    | 0  | MSA 中垂直有效行数参数                                 |                       |

| 18 | O_hsw        | 0  | MSA中水平同步信号宽度参数                                |                       |

| 19 | O_vsw        | 0  | MSA中垂直同步信号宽度参数                                |                       |

| 20 | O_hsp        | 0  | MSA中水平同步信号极性参数                                |                       |

| 21 | O_vsp        | 0  | MSA中垂直同步信号极性参数                                |                       |

| 22 | O_misc0      | 0  | MSA 中 MISC0 参数                                |                       |

| 23 | O_misc1      | 0  | MSA 中 MISC1 参数                                |                       |

| 24 | O_ls_vs      | 0  | 链路时钟域场同步信号                                    |                       |

| 25 | O_ls_hs      | 0  | 链路时钟域行同步信号                                    |                       |

| 26 | I_kcode0     | I  | 输入 lane0 链路 K 码标志 0                           |                       |

|    |              |    | User Clock Ratio 为 1:20 时,位                   |                       |

IPUG1179-2.1 18(36)

| J. 17 | D. E. 4.41 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | THAN                                     | <i>h</i> |

|-------|------------|---------------------------------------|------------------------------------------|----------|

| 序号    | 信号名称       | 方向                                    | 描述                                       | 备注       |

|       |            |                                       | 宽 2 bits                                 |          |

|       |            |                                       | User Clock Ratio 为 1:40 时,位<br>宽 4 bits  |          |

| 27    | I_data0    | 1                                     | 输入 lane0 链路数据 0                          |          |

|       |            |                                       | User Clock Ratio 为 1:20 时,位<br>宽 16 bits |          |

|       |            |                                       | User Clock Ratio 为 1:40 时,位<br>宽 32 bits |          |

| 28    | I_kcode1   | I                                     | 输入 lane1 链路 K 码标志 1, 链路 为 2/4 lane 时支持   |          |

|       |            |                                       | User Clock Ratio 为 1:20 时,位<br>宽 2 bits  |          |

|       |            |                                       | User Clock Ratio 为 1:40 时,位<br>宽 4 bits  |          |

| 29    | I_data1    | I                                     | 输入 lane1 链路数据 1,链路为<br>2/4 lane 时支持      |          |

|       |            |                                       | User Clock Ratio 为 1:20 时,位<br>宽 16 bits |          |

|       |            |                                       | User Clock Ratio 为 1:40 时,位<br>宽 32 bits |          |

| 30    | I_kcode2   | I                                     | 输入 lane2 链路 K 码标志 2, 链路 为 4 lane 时支持     |          |

|       |            |                                       | User Clock Ratio 为 1:20 时,位<br>宽 2 bits  |          |

|       |            |                                       | User Clock Ratio 为 1:40 时,位<br>宽 4 bits  |          |

| 31    | I_data2    | I                                     | 输入 lane2 链路数据 2,链路为 4 lane 时支持           |          |

|       |            |                                       | User Clock Ratio 为 1:20 时,位<br>宽 16 bits |          |

|       |            |                                       | User Clock Ratio 为 1:40 时,位<br>宽 32 bits |          |

| 32    | I_kcode3   | I                                     | 输入 lane3 链路 K 码标志 3,链路 为 4 lane 时支持      |          |

|       |            |                                       | User Clock Ratio 为 1:20 时,位<br>宽 2 bits  |          |

|       |            |                                       | User Clock Ratio 为 1:40 时,位<br>宽 4 bits  |          |

| 33    | I_data3    | I                                     | 输入 lane3 链路数据 3,链路为 4 lane 时支持           |          |

|       |            |                                       | User Clock Ratio 为 1:20 时,位<br>宽 16 bits |          |

|       |            |                                       | User Clock Ratio 为 1:40 时,位<br>宽 32 bits |          |

IPUG1179-2.1 19(36)

| 序号 | 信号名称                | 方向 | 描述                                                                                       | 备注 |

|----|---------------------|----|------------------------------------------------------------------------------------------|----|

| 34 | O_rx0_tps1_don<br>e | О  | Lane0 TPS1 数据训练结束标志<br>参数 Training Pattern TPS1<br>Enable 为 Yes 时有效                      |    |

| 35 | O_rx0_tps1_ok       | 0  | Lane0 TPS1 数据训练成功标志<br>参数 Training Pattern TPS1<br>Enable 为 Yes 时有效                      |    |

| 36 | O_rx0_tps2_don<br>e | 0  | Lane0 TPS2 数据训练结束标志<br>参数 Training Pattern TPS2<br>Enable 为 Yes 时有效                      |    |

| 37 | O_rx0_tps2_ok       | 0  | Lane0 TPS2 数据训练成功标志<br>参数 Training Pattern TPS2<br>Enable 为 Yes 时有效                      |    |

| 38 | O_rx1_tps1_don<br>e | 0  | Lane1 TPS1 数据训练结束标志<br>参数 Training Pattern TPS1<br>Enable 为 Yes 时有效                      |    |

| 39 | O_rx1_tps1_ok       | 0  | Lane1 TPS1 数据训练成功标志,<br>链路为 2/4 lane 时支持<br>参数 Training Pattern TPS1<br>Enable 为 Yes 时有效 |    |

| 40 | O_rx1_tps2_don<br>e | 0  | Lane1 TPS2 数据训练结束标志<br>参数 Training Pattern TPS2<br>Enable 为 Yes 时有效                      |    |

| 41 | O_rx1_tps2_ok       | 0  | Lane1 TPS2 数据训练成功标志,<br>链路为 2/4 lane 时支持<br>参数 Training Pattern TPS2<br>Enable 为 Yes 时有效 |    |

| 42 | O_rx2_tps1_don<br>e | 0  | Lane2 TPS1 数据训练结束标志<br>参数 Training Pattern TPS1<br>Enable 为 Yes 时有效                      |    |

| 43 | O_rx2_tps1_ok       | 0  | Lane2 TPS1 数据训练成功标志,<br>链路为 4 lane 时支持<br>参数 Training Pattern TPS1<br>Enable 为 Yes 时有效   |    |

| 44 | O_rx2_tps2_don<br>e | 0  | Lane2 TPS2 数据训练结束标志<br>参数 Training Pattern TPS2<br>Enable 为 Yes 时有效                      |    |

| 45 | O_rx2_tps2_ok       | 0  | Lane2 TPS2 数据训练成功标志,<br>链路为 4 lane 时支持<br>参数 Training Pattern TPS2<br>Enable 为 Yes 时有效   |    |

| 46 | O_rx3_tps1_don<br>e | О  | Lane3 TPS1 数据训练结束标志<br>参数 Training Pattern TPS1<br>Enable 为 Yes 时有效                      |    |

IPUG1179-2.1 20(36)

| 序号 | 信号名称                  | 方向 | 描述                                                                                                                                                                                                              | 备注  |

|----|-----------------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 47 | O_rx3_tps1_ok         | 0  | Lane3 TPS1 数据训练成功标志,<br>链路为 4 lane 时支持<br>参数 Training Pattern TPS1<br>Enable 为 Yes 时有效                                                                                                                          | д ш |

| 48 | O_rx3_tps2_don<br>e   | 0  | Lane3 TPS2 数据训练结束标志<br>参数 Training Pattern TPS2<br>Enable 为 Yes 时有效                                                                                                                                             |     |

| 49 | O_rx3_tps2_ok         | 0  | Lane3 TPS2 数据训练成功标志,<br>链路为 4 lane 时支持<br>参数 Training Pattern TPS2<br>Enable 为 Yes 时有效                                                                                                                          |     |

| 50 | O_unp0_data           | 0  | 输出 lane0 解包数据 User Clock Ratio 为 1:20 时,格式{B,G,R} User Clock Ratio 为 1:40 时,格式{B <sub>1</sub> ,G <sub>1</sub> ,R <sub>1</sub> ,B <sub>0</sub> ,G <sub>0</sub> ,R <sub>0</sub> }                                 |     |

| 51 | O_unp0_data_va<br>lid | 0  | 输出 lane0 解包数据有效信号                                                                                                                                                                                               |     |

| 52 | O_unp1_data           | 0  | 输出 lane1 解包数据,链路为 2/4 lane 时支持<br>User Clock Ratio 为 1:20 时,格<br>式{B,G,R}<br>User Clock Ratio 为 1:40 时,格<br>式{B <sub>1</sub> ,G <sub>1</sub> ,R <sub>1</sub> ,B <sub>0</sub> ,G <sub>0</sub> ,R <sub>0</sub> }  |     |

| 53 | O_unp1_data_va<br>lid | 0  | 输出 lane1 解包数据有效信号,链路为 2/4 lane 时支持                                                                                                                                                                              |     |

| 54 | O_unp2_data           | 0  | 输出 lane2 解包数据,链路为 4 lane 时支持<br>User Clock Ratio 为 1:20 时,格<br>式{B,G,R}<br>User Clock Ratio 为 1:40 时,格<br>式{B <sub>1</sub> ,G <sub>1</sub> ,R <sub>1</sub> ,B <sub>0</sub> ,G <sub>0</sub> ,R <sub>0</sub> }    |     |

| 55 | O_unp2_data_va<br>lid | 0  | 输出 lane2 解包数据有效信号,链路为 4 lane 时支持                                                                                                                                                                                |     |

| 56 | O_unp3_data           | 0  | 输出 lane3 解包数据,链路为 4<br>lane 时支持<br>User Clock Ratio 为 1:20 时,格<br>式{B,G,R}<br>User Clock Ratio 为 1:40 时,格<br>式{B <sub>1</sub> ,G <sub>1</sub> ,R <sub>1</sub> ,B <sub>0</sub> ,G <sub>0</sub> ,R <sub>0</sub> } |     |

| 57 | O_unp3_data_va<br>lid | 0  | 输出 lane3 解包数据有效信号,链路为 4 lane 时支持                                                                                                                                                                                |     |

注!

IPUG1179-2.1 21(36)

3.5 参数配置

● User Clock Ratio 参数为 1:20 时,每 lane 输出数据单像素,User Clock Ratio 参数为 1:40 时,每 lane 输出数据双像素。

• 输出解包数据有效信号 unp\_data\_valid 每行非连续信号, 与 DE 信号不同。

## 3.5 参数配置

## 3.5.1 EDP Encoder 参数

表 3-6 EDP Encoder 参数

| 序号 | 参数名称                                           | 允许范围          | 默认值  | 描述                                                                                                                                   |

|----|------------------------------------------------|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------|

| 1  | User Clock Ratio                               | 1:20/1:40     | 1:20 | 用户时钟与串行化时钟比例                                                                                                                         |

| 2  | Lanes Number                                   | 1/2/4         | 1    | 主链路 lane 数                                                                                                                           |

| 3  | Bits Per Pixel                                 | 24            | 24   | 每像素 bit 数                                                                                                                            |

| 4  | TX Line Buffer<br>Depth                        | 2048/4096/809 | 4096 | 发送行缓存深度                                                                                                                              |

| 5  | Active Symbols<br>Per TU Almost<br>Equal To TU | 勾选/不勾选        | 不勾选  | 若 User Clock Ratio 为1:20,<br>I_avs_per_tu==<br>I_tu_size-2,必须勾选;<br>若 User Clock Ratio 为1:40,<br>I_avs_per_tu==<br>I_tu_size-4,必须勾选。 |

| 6  | Double Pixels<br>Per Lane                      | 勾选/不勾选        | 不勾选  | 每 lane 输入双像素使能控制                                                                                                                     |

| 7  | Training Pattern<br>TPS1 Enable                | 勾选/不勾选        | 勾选   | 训练 Pattern TPS1 使能控制                                                                                                                 |

| 8  | Training Pattern<br>TPS2 Enable                | 勾选/不勾选        | 勾选   | 训练 Pattern TPS2 使能控制                                                                                                                 |

### 3.5.2 EDP Decoder 参数

#### 表 3-7 EDP Decoder 参数

| 序号 | 参数名称                            | 允许范围             | 默认值  | 描述                                                                                   |

|----|---------------------------------|------------------|------|--------------------------------------------------------------------------------------|

| 1  | User Clock Ratio                | 1:20/1:40        | 1:20 | 用户时钟与串行化时钟比例                                                                         |

| 2  | Lanes Number                    | 1/2/4            | 1    | 主链路 lane 数                                                                           |

| 3  | Bits Per Pixel                  | 24               | 24   | 每像素 bit 数                                                                            |

| 4  | RX Deskew<br>Enable             | 勾选/不勾选           | 勾选   | 接收解偏移使能控制,如<br>EDP PHY 启用 RX Channel<br>Bonding 功能,可关闭接收<br>解偏移模块<br>勾选为 Yes,不勾选为 No |

| 5. | Training Pattern TPS1 Enable    | <br>  勾选/不勾选<br> | 勾选   | 训练 Pattern TPS1 使能控制<br>勾选为 Yes,不勾选为 No                                              |

| 6  | Training Pattern<br>TPS2 Enable | 勾选/不勾选           | 勾选   | 训练 Pattern TPS2 使能控制<br>勾选为 Yes,不勾选为 No                                              |

IPUG1179-2.1 22(36)

3.6 时序说明

## 3.6 时序说明

本节介绍 Gowin EDP Encoder Decoder IP 的时序情况。

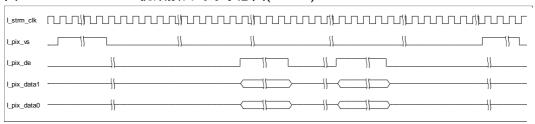

EDP Encoder 视频接口时序示意图(2 lanes)如图 3-13 所示。

#### 图 3-13 EDP Encoder 视频接口时序示意图(2lanes)

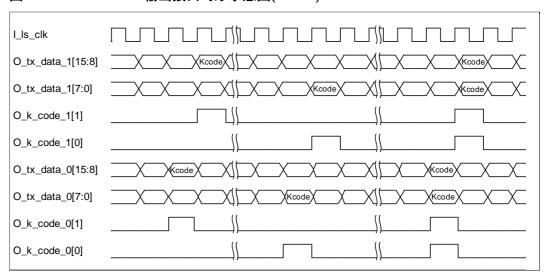

EDP Encoder 输出接口时序示意图(2 lanes)如图 3-14 所示,数据位宽以 16bit 为例。

#### 图 3-14 EDP Encoder 输出接口时序示意图(2lanes)

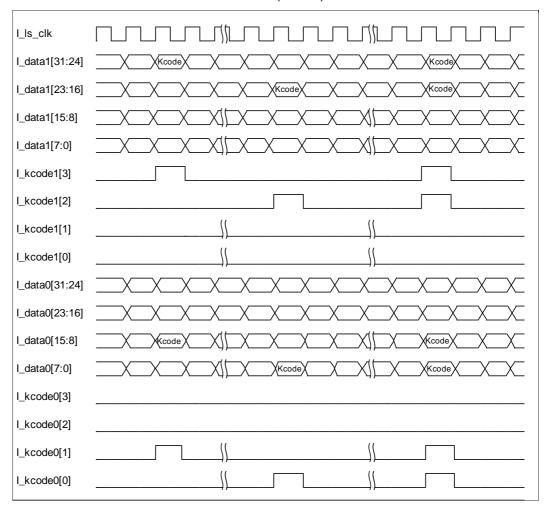

EDP Decoder 输入接口时序示意图(2 lanes)如图 3-15 所示,数据位宽以 32 bits 为例。

IPUG1179-2.1 23(36)

**3** 功能描述 **3.6** 时序说明

#### 图 3-15 EDP Decoder 输入接口时序示意图(2lanes)

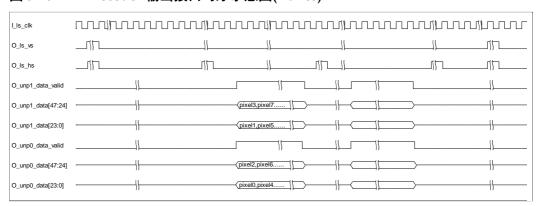

EDP Decoder 输出接口时序示意图(2 lanes)如图 3-16 所示,像素数据位宽以 48 bits 为例。

#### 图 3-16 EDP Decoder 输出接口时序示意图(2lanes)

#### 注!

User Clock Ratio 为 1:40 时,Lanes Number 为 2 或 4lanes 时,每 lane 输出 48 bits 像素数据非顺序输出,顺序如上图所示。

IPUG1179-2.1 24(36)

## 3.7 EDP Encoder 端口参数计算

本文以三个例子说明端口参数计算方法。

#### 示例一

3840x2160@60Hz 分辨率 eDP 屏,串行速率 5.4Gbps,lanes=4,视频流像素时钟频率 f\_Strm\_Clk =533.280MHz,链路时钟频率 f\_LS\_Clk=540MHz,视频时序参数 htotal=4000,vtotal=2222,hstart=48,vstart=6,hwidth=3840,vheight=2160,hsw=8,vsw=2,hsp=0,vsp=0,misc0=0x20,misc1=0x00,BPP(Bits Per Pixel)=24,User Clock Ratio=1:40。

其余端口参数计算过程。

- 1. Nvid 取 32768, Mvid= Nvid \* (f\_Strm\_Clk/f\_LS\_Clk)=32360。

- 2. 计算每 lane 链路时钟域一行总字节数(Hbytes),利用一行总时间相等计算,Hbytes =htotal/f Strm Clk\*f LS Clk =4050(向下取整)。

- 3. Transfer Unit 选取,如 I\_tu\_size =32。

- 4. Average valid symbols per TU 计算。如 I\_avs\_per\_tu = f\_Strm\_Clk\*BPP/8/lanes/ f\_LS\_Clk\* I\_tu\_size=24(实际 23.7),如果 User Clock Ratio 为 1:20,向上取邻近 2 的倍数,如果 User Clock Ratio 为 1:40,向上取邻近 4 的倍数。

- 5. 每 lane 有效字节数(Bla)。如每行 3840 个像素,对应每行有效字节数 =3840\*BPP/8=11520bytes,分为 4 个 lane 传输,每 lane 有效字节数 Bla =11520/4=2880bytes/lane。

- 6. 每 lane 一行 TU 数(Bla/ I\_avs\_per\_tu)。举例: 2880/24=120 个 TU, 如果不整除,整数部分为完整 TU 数,小数部分对应数据在最后一个 TU 传输。

- 7. 每 lane 一行 TU 总占字节数,最后一个 TU 只有数据,无填充 0。如所有 TU 包含总 byte 数=119\*32+24=3832。

- 8. 计算每 lane 一行总字节数 Hbytes,如果 User Clock Ratio 为 1:20,需为 2 的倍数,如果 User Clock Ratio 为 1:40,需为 4 的倍数。将一行总字节数值扩大到相邻值。如 4050 不是 4 的倍数,向上取 4052。

- 9. 每 lane 每行 LS clock 数,如果 User Clock Ratio 为 1:20,则 Hbytes 除 2,如果 User Clock Ratio 为 1:40,则 Hbytes 除 4。如 I\_lsck\_htotal=4052/4=1013。

- 10. 每 lane 每行消隐占 LS clock 数,如果 User Clock Ratio 为 1:20,则 (Hbytes-每 lane 一行 TU 总占字节数)除 2,如果 User Clock Ratio 为 1:40,则(Hbytes-每 lane 一行 TU 总占字节数)除 4。如 I\_lsck\_hblank =(4052-3832)/4=55。

- 11.再次计算 Mvid,公式 Mvid/Nvid = Htotal/Hbytes。如 Mvid = 4000/4052\*32768 = 32347。

IPUG1179-2.1 25(36)

#### 示例二

1280x800@60Hz 分辨率 eDP 屏,串行速率 2.7Gbps,lanes=2,视频流像素时钟频率 f\_Strm\_Clk =72.484MHz,链路时钟频率 f\_LS\_Clk=270MHz,视频时序参数 htotal=1452,vtotal=832,hstart=48,vstart=6,hwidth=1280,vheight=800,hsw=8,vsw=2,hsp=0,vsp=0,misc0=0x20,misc1=0x00。BPP(Bits Per Pixel)=24。User Clock Ratio=1:40。

其余端口参数计算过程。

- 1. Nvid 取 32768,Mvid= Nvid \* (f\_Strm\_Clk/f\_LS\_Clk)=8797。

- 2. 计算每 lane 链路时钟域一行总字节数(Hbytes),利用一行总时间相等计算,Hbytes =htotal/f\_Strm\_Clk\*f\_LS\_Clk =5408(向下取整)。

- 3. Transfer Unit 选取。如 I\_tu\_size =32。

- 4. Average valid symbols per TU 计算。如 I\_avs\_per\_tu = f\_Strm\_Clk\*BPP/8/lanes/ f\_LS\_Clk\* I\_tu\_size=16 (实际 12.89),如果 User Clock Ratio 为 1:20,向上取邻近 2 的倍数,如果 User Clock Ratio 为 1:40,向上取邻近 4 的倍数。

- 5. 每 lane 有效字节数(Bla)。如每行 1280 个像素,对应每行有效字节数 =1280\*BPP/8=3840bytes,分为 2 个 lane 传输,每 lane 有效字节数 Bla =3840/2=1920bytes/lane。

- 6. 每 lane 一行 TU 数(Bla/ I\_avs\_per\_tu)。如 1920/16=120 个 TU,如果不整除,整数部分为完整 TU 数,小数部分对应数据在最后一个 TU 传输。

- 7. 每 lane 一行 TU 总占字节数,最后一个 TU 只有数据,无填充 0。如所有 TU 包含总 byte 数=119\*32+16=3824。

- 8. 计算每 lane 一行总字节数 Hbytes,如果 User Clock Ratio 为 1:20,需为 2 的倍数,如果 User Clock Ratio 为 1:40,需为 4 的倍数。将一行总字节 数值扩大到相邻值。如 5408 是 4 的倍数,就取 5408。

- 9. 每 lane 每行 LS clock 数,如果 User Clock Ratio 为 1:20,则 Hbytes 除 2,如果 User Clock Ratio 为 1:40,则 Hbytes 除 4。如 I lsck htotal=5408/4=1352。

- 10. 每 lane 每行消隐占 LS clock 数,如果 User Clock Ratio 为 1:20,则 (Hbytes-每 lane 一行 TU 总占字节数)除 2,如果 User Clock Ratio 为 1:40,则(Hbytes-每 lane 一行 TU 总占字节数)除 4。如 I\_lsck\_hblank =(5408-3824)/4=396。

- 11. 再次计算 Mvid,公式 Mvid/Nvid = Htotal/Hbytes。如 Mvid = 1452/5408\*32768 = 8797。

#### 示例三

1920x1080@59.954Hz分辨率 DP显示器,串行速率 1.62Gbps,lanes=4,视频流像素时钟频率 f\_Strm\_Clk = 148.386MHz,链路时钟频率 f\_LS\_Clk=162MHz,视频时序参数 htotal=2200, vtotal=1125, hstart=192, vstart=41, hwidth=1920, vheight=1080, hsw=44, vsw=5, hsp=0, vsp=0,

IPUG1179-2.1 26(36)

- misc0=0x20, misc1=0x00。BPP(Bits Per Pixel)=24。User Clock Ratio=1:40。 其余端口参数计算过程。

- 1. Nvid 取 32768,Mvid= Nvid \* (f\_Strm\_Clk/f\_LS\_Clk)=30014。

- 2. 计算每 lane 链路时钟域一行总字节数(Hbytes),利用一行总时间相等计算,Hbytes =htotal/f Strm Clk\*f LS Clk =2401(向下取整)。

- 3. Transfer Unit 选取。如 I tu size =64。

- 4. Average valid symbols per TU 计算。如 I\_avs\_per\_tu = f\_Strm\_Clk\*BPP/8/lanes/ f\_LS\_Clk\* I\_tu\_size=44(实际 43.966),如果 User Clock Ratio 为 1:20,向上取邻近 2 的倍数,如果 User Clock Ratio 为 1:40,向上取邻近 4 的倍数。

- 5. 每 lane 有效字节数(Bla)。如每行 1920 个像素,对应每行有效字节数 =1920\*BPP/8=5760bytes,分为 4 个 lane 传输,每 lane 有效字节数 Bla =5760/4=1440bytes/lane。

- 6. 每 lane 一行 TU 数(Bla/ I\_avs\_per\_tu)。如 1440/44=32.73 个 TU,如果不整除,整数部分为完整 TU 数,传输 32\*44=1408bytes,小数部分对应数据在最后一个 TU 传输,传输 1440-1408=32bytes。

- 7. 每 lane 一行 TU 总占字节数,最后一个 TU 只有数据,无填充 0。如所有 TU 包含总 byte 数=32\*64+32=2080。

- 8. 计算每 lane 一行总字节数 Hbytes,如果 User Clock Ratio 为 1:20,需为 2 的倍数,如果 User Clock Ratio 为 1:40,需为 4 的倍数。将一行总字节 数值扩大到相邻值。如 2401 不是 4 的倍数,向上取 2404。

- 9. 每 lane 每行 LS clock 数,如果 User Clock Ratio 为 1:20,则 Hbytes 除 2,如果 User Clock Ratio 为 1:40,则 Hbytes 除 4。如 I lsck htotal=2404/4=601。

- 10.每 lane 每行消隐占 LS clock 数,如果 User Clock Ratio 为 1:20,则 (Hbytes-每 lane 一行 TU 总占字节数)除 2,如果 User Clock Ratio 为 1:40,则(Hbytes-每 lane 一行 TU 总占字节数)除 4。如 I\_lsck\_hblank =(2404-2080)/4=81。

- 11. 再次计算 Mvid,公式 Mvid/Nvid = Htotal/Hbytes。如 Mvid = 2200/2404\*32768 = 29987。

IPUG1179-2.1 27(36)

4.1 EDP Encoder IP 配置

# **4** 果面配置

用户可用高云半导体云源软件中的 IP 内核生成器工具调用和配置高云 EDP Encoder 和 Decoder IP。

## 4.1 EDP Encoder IP 配置

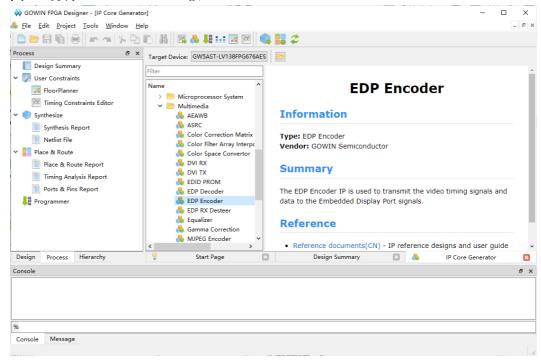

1. 打开 IP Core Generator

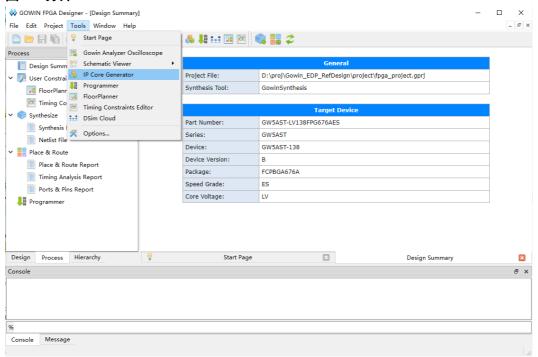

用户建立工程后,单击左上角"Tools"选项卡,下拉单击"IP Core Generator"选项,即可打开 Gowin IP Core Generator 如图 4-1 所示。

#### ₩ GOWIN FPGA Designer - [Design Summary] File Edit Project Tools Window Help Start Page 🚴 👫 💴 🖂 🍳 🔡 🏖 Gowin Analyzer Oscilloscope Design Summ ✓ User Constrai Project File: D:\proj\Gowin\_EDP\_RefDesign\project\fpga\_project.gprj User Constrai FloorPlanr Timing Co Timing Co Timing Constraints Editor Synthesis Tool: GowinSynthesis Synthesize DSim Cloud GW5AST-LV138FPG676AES Synthesis Options... GW5AST Series: Device: GW5AST-138 ✓ Place & Route Device Version: Place & Route Report FCPBGA676A Package: Timing Analysis Report Speed Grade: ES Ports & Pins Report Core Voltage: LV Programmer Design Process Hierarchy 9 Start Page × ₽×

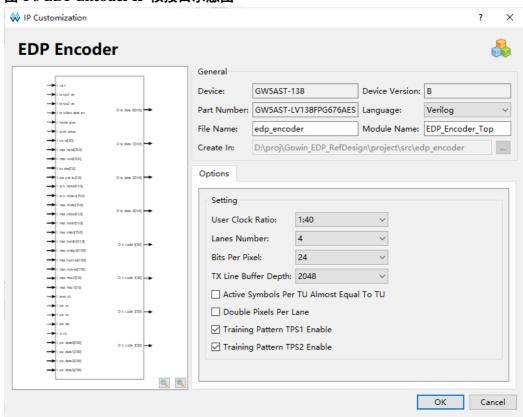

#### 图 4-1 打开 IP Core Generator

#### 2. 打开 EDP Encoder IP 核

单击 "Multimedia" 选项,双击 "EDP Encoder",打开 EDP Encoder IP 核的配置界面如图 4-2 所示。

IPUG1179-2.1 28(36)

4.1 EDP Encoder IP 配置

#### 图 4-2 打开 EDP Encoder IP 核

#### 3. EDP Encoder IP 核端口界面

配置界面左侧为 EDP Encoder IP 核的接口示意图如图 4-3 所示。

#### 图 4-3 EDP Encoder IP 核接口示意图

IPUG1179-2.1 29(36)

4 界面配置 4.1 EDP Encoder IP 配置

#### 4. 配置基本信息

在配置界面的上部分是工程基本信息配置界面,以GW5AST-138为例, 封装选择FPG676A。Module Name 选项后面是工程产生后项层文件的名字, 默认为"EDP\_Encoder\_Top",用户可自行修改。"File Name"是IP 核文件 产生的文件夹,存放 EDP Encoder IP 核所需文件,默认为"edp\_encoder", 用户可自行修改路径。Create In 选项是IP 核文件夹产生路径,默认为"\ 工程路径\src\edp\_encoder",用户可自行修改路径。

#### 图 4-4 基本信息配置界面

| General      |                                                     |                 |                 |

|--------------|-----------------------------------------------------|-----------------|-----------------|

| Device:      | GW5AST-138                                          | Device Version: | В               |

| Part Number: | GW5AST-LV138FPG676AES                               | Language:       | Verilog ~       |

| File Name:   | edp_encoder                                         | Module Name:    | EDP_Encoder_Top |

| Create In:   | D:\proj\Gowin_EDP_RefDesign\project\src\edp_encoder |                 |                 |

#### 5. Options 选项卡

在选项卡中,用户需要配置 EDP Encoder 所使用的参数信息。

#### 图 4-5 Options 选项卡

| tions                                    |      |   |

|------------------------------------------|------|---|

| Setting                                  |      |   |

| User Clock Ratio:                        | 1:40 | ~ |

| Lanes Number:                            | 4    | ~ |

| Bits Per Pixel:                          | 24   | ~ |

| TX Line Buffer Depth:                    | 2048 | ~ |

| Active Symbols Per TU Almost Equal To TU |      |   |

| ☐ Double Pixels Per Lane                 |      |   |

| ✓ Training Pattern TPS1 Enable           |      |   |

| ☑ Training Pattern TPS2 Enable           |      |   |

IPUG1179-2.1 30(36)

4 界面配置 4.2 EDP Decoder IP 配置

## 4.2 EDP Decoder IP 配置

#### 1. 打开 IP Core Generator

用户建立工程后,单击左上角"Tools"选项卡,下拉单击"IP Core Generater"选项,即可打开 Gowin IP Core Generator 如图 4-6 所示。

#### 图 4-6 打开 IP Core Generator

#### 2. 打开 EDP Decoder IP 核

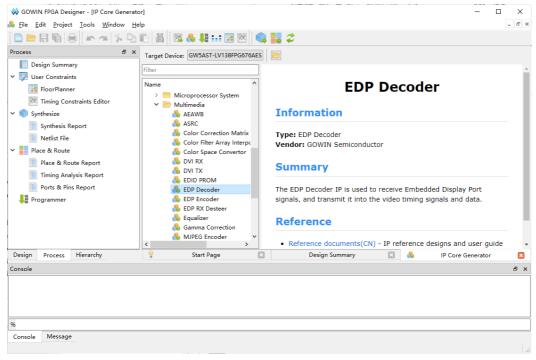

单击 "Multimedia" 选项,双击 "EDP Decoder",打开 EDP Decoder IP 核的配置界面如图 4-7 所示。

IPUG1179-2.1 31(36)

#### 图 4-7 打开 EDP Decoder IP 核

#### 3. EDP Decoder IP 核端口界面

配置界面左侧为 EDP Decoder IP 核的接口示意图如图 4-8 所示。

#### 图 4-8 EDP Decoder IP 核接口示意图

IPUG1179-2.1 32(36)

4 界面配置 4.2 EDP Decoder IP 配置

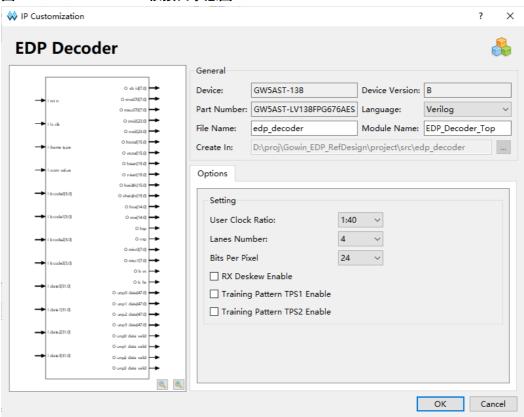

#### 4. 配置基本信息

在配置界面的上部分是工程基本信息配置界,以 GW5AST-138 为例,封装选择 FPG676A。Module Name 选项后面是工程产生后项层文件的名字,默认为 "EDP\_Decoder\_Top",用户可自行修改。"File Name"是 IP 核文件产生的文件夹,存放 EDP Decoder IP 核所需文件,默认为"edp\_decoder",用户可自行修改路径。Create In 选项是 IP 核文件夹产生路径,默认为"\工程路径\src\edp\_decoder",用户可自行修改路径。

#### 图 4-9 基本信息配置界面

| General      |                                                     |                 |                 |

|--------------|-----------------------------------------------------|-----------------|-----------------|

| Device:      | GW5AST-138                                          | Device Version: | В               |

| Part Number: | GW5AST-LV138FPG676AES                               | Language:       | Verilog ~       |

| File Name:   | edp_decoder                                         | Module Name:    | EDP_Decoder_Top |

| Create In:   | D:\proj\Gowin_EDP_RefDesign\project\src\edp_decoder |                 |                 |

#### 5. Options 选项卡

在选项卡中,用户需要配置 EDP Decoder 所使用的参数信息。

#### 图 4-10 Options 选项卡

| Options                        |        |  |

|--------------------------------|--------|--|

| Setting                        |        |  |

| User Clock Ratio:              | 1:40 ∨ |  |

| Lanes Number:                  | 4 ~    |  |

| Bits Per Pixel                 | 24 ~   |  |

| RX Deskew Enable               |        |  |

| ☐ Training Pattern TPS1 Enable |        |  |

| ☐ Training Pattern TPS2 Enable |        |  |

IPUG1179-2.1 33(36)

# 5参考设计

本节主要介绍 EDP Encoder Decoder IP 的参考设计实例的搭建及使用方法。详细信息请参见高云半导体官网给出的相关参考设计。

#### 设计实例

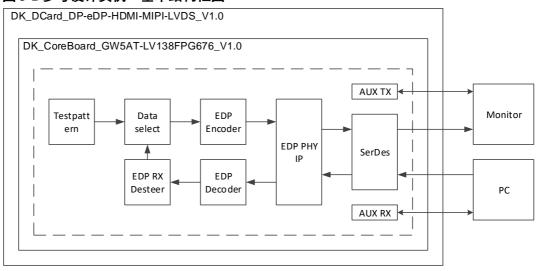

本参考设计以 DK\_CoreBoard\_GW5AT-LV138FPG676\_V1.0 和 DK\_DCard\_DP-eDP-HDMI-MIPI-LVDS\_V1.0 开发板为例,参考设计基本结构框图如图 5-1 所示。开发板相关信息参考官方网站。

#### 图 5-1 参考设计实例一基本结构框图

在参考设计中,分为 DP 发送部分和 DP 接收部分。DP 发送部分通过 Testpattern 模块产生测试图视频信号,经过 EDP Encoder 模块编码,输入 到 EDP PHY IP 转成串行信号输出到 DP 显示器,DP 接收部分如未接收到 数据则一直显示测试图。DP 接收部分由 PC 输出的 DP 信号经过 EDP PHY IP 接收转成并行信号,通过 EDP Decoder 模块解码,经过 EDP RX Desteer 模块格式转换,再输出到数据选择模块后到显示器显示。

IPUG1179-2.1 34(36)

6 文件交付 6.1 文档

## **6** 文件交付

Gowin EDP Encoder Decoder IP 交付文件主要包含三个部分,分别为:文档、设计源代码和参考设计。

## 6.1 文档

文件夹主要包含用户指南 PDF 文档。

#### 表 6-1 文档列表

| 名称                                          | 描述                                   |

|---------------------------------------------|--------------------------------------|

| IPUG1179, Gowin EDP Encoder Decoder IP 用户指南 | 高云 EDP Encoder Decoder IP 用户手册,即本手册。 |

## 6.2 设计源代码(加密)

加密代码文件夹包含 Gowin EDP Encoder Decoder IP 的 RTL 加密代码, 供 GUI 使用,以配合高云云源软件产生用户所需的 IP 核。

#### 表 6-2 Gowin EDP Encoder 设计源代码列表

| 名称            | 描述                     |

|---------------|------------------------|

| edp_encoder.v | IP 核项层文件,给用户提供接口信息,加密。 |

#### 表 6-3 Gowin EDP Decoder 设计源代码列表

| 名称            | 描述                     |

|---------------|------------------------|

| edp_decoder.v | IP 核项层文件,给用户提供接口信息,加密。 |

## 6.3 参考设计

Gowin EDP RefDesign 文件夹主要包含 Gowin EDP Encoder Decoder IP 的网表文件,用户参考设计,约束文件、顶层文件及工程文件夹等。

#### 表 6-4 Gowin EDP RefDesign 文件夹内容列表

| 名称               | 描述             |

|------------------|----------------|

| test_top.v       | 参考设计的顶层 module |

| fpga_project.cst | 工程物理约束文件       |

| fpga_project.sdc | 工程时序约束文件       |

IPUG1179-2.1 35(36)

6.3 参考设计

| 名称              | 描述              |

|-----------------|-----------------|

| key_debounce.v  | 消抖模块文件          |

| key_debounceN.v | 消抖模块文件          |

| serdes          | EDP PHY IP 文件夹  |

| testpatternX4.v | 测试图产生模块         |

| auxlink         | 辅助通道 AUX 通信文件夹  |

| gowin_pll       | PLL IP 文件夹      |

| edp_decoder     | EDP 接收模块文件夹     |

| edp_encoder     | EDP 发送模块文件夹     |

| edp_rx_desteer  | EDP 接收数据排序模块文件夹 |

IPUG1179-2.1 36(36)