# Gowin FP Div IP 用户指南

IPUG1185-1.0,2024-03-29

#### 版权所有 © 2024 广东高云半导体科技股份有限公司

**GO**₩IN高云、₩、Gowin、GowinSynthesis、云源以及高云均为广东高云半导体科技股份有限公司注册商标,本手册中提到的其他任何商标,其所有权利属其拥有者所有。未经本公司书面许可,任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部,并不得以任何形式传播。

#### 免责声明

本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止反言或其它方式授予任何知识产权许可。除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。高云半导体不承诺对这些文档进行适时的更新。

#### 版本信息

| 日期         | 版本  | 说明    |

|------------|-----|-------|

| 2024/03/29 | 1.0 | 初始版本。 |

# 目录

| i   |

|-----|

| ii  |

| iii |

| 1   |

| 1   |

| 1   |

| 2   |

| 2   |

| 3   |

| 3   |

| 3   |

| 3   |

| 4   |

| 4   |

| 5   |

| 6   |

| 8   |

| 9   |

| 9   |

| 10  |

| 11  |

| 12  |

| 12  |

| 12  |

|     |

# 图目录

| 图 3-1 Gowin FP Div IP 结构示意图 | 5  |

|-----------------------------|----|

| 图 4-1 Gowin FP Div IP 的接口实现 | 6  |

| 图 5-1 Gowin FP Div IP 信号时序  | 8  |

| 图 6-1 工具栏图标打开 IP 配置界面       | 9  |

| 图 6-2 Gowin FP Div IP 配置界面  | 10 |

IPUG1185-1.0 ii

## 表目录

| 表 1-1 术语、缩略语                            | . 2  |

|-----------------------------------------|------|

| 表 2-1 Gowin FP Div IP                   | . 3  |

| 表 2-2 Gowin FP Div IP 占用资源              | . 4  |

| 表 4-1 Gowin FP Div IP I/O 端口列表          | . 6  |

| 表 8-1 Gowin FP Div IP 文档列表              | . 12 |

| 表 8-2 Gowin FP Div IP RefDesign 文件夹内容列表 | . 12 |

IPUG1185-1.0 iii

1.1 手册内容

# 1

#### 1.1 手册内容

Gowin FP Div IP 用户指南主要内容包括功能特点、端口描述、时序说明、配置调用、参考设计等,旨在帮助用户快速了解 Gowin FP Div IP 的产品特性、特点及使用方法。本手册中的软件界面截图参考的是 V1.9.9 Beta-4 版本,因软件版本升级,部分信息可能会略有差异,具体以用户软件版本的信息为准。

#### 1.2 相关文档

通过登录高云半导体网站 <u>www.gowinsemi.com.cn</u>可以下载、查看以下相关文档:

- DS100, GW1N 系列 FPGA 产品数据手册

- DS117, GW1NR 系列 FPGA 产品数据手册

- DS821, GW1NS 系列 FPGA 产品数据手册

- DS861, GW1NSR 系列 FPGA 产品数据手册

- DS891, GW1NSE 系列安全 FPGA 产品数据手册

- DS961, GW2ANR 系列 FPGA 产品数据手册

- DS102, GW2A 系列 FPGA 产品数据手册

- DS226, GW2AR 系列 FPGA 产品数据手册

- DS971, GW2AN-18X &9X 器件数据手册

- DS976, GW2AN-55 器件数据手册

- DS981, GW5AT 系列 FPGA 产品数据手册

- DS1103, GW5A 系列 FPGA 产品数据手册

- DS1104, GW5AST 系列 FPGA 产品数据手册

- DS1108, GW5AR 系列 FPGA 产品数据手册

IPUG1185-1.0 1(12)

1 关于本手册 1.3 术语、缩略语

- DS1105, GW5AS 系列 FPGA 产品数据手册

- SUG100, Gowin 云源软件用户指南

## 1.3 术语、缩略语

表 1-1 中列出了本手册中出现的相关术语、缩略语及相关释义。

#### 表 1-1 术语、缩略语

| 术语、缩略语   | 全称                      | 含义     |

|----------|-------------------------|--------|

| Register | Register                | 寄存器    |

| ALU      | Arithmetic Logical Unit | 算数逻辑单元 |

| LUT      | Look-up Table           | 查找表    |

## 1.4 技术支持与反馈

高云半导体提供全方位技术支持,在使用过程中如有任何疑问或建议,可直接与公司联系:

网站: www.gowinsemi.com.cn

E-mail: <a href="mailto:support@gowinsemi.com">support@gowinsemi.com</a>

Tel: +86 755 8262 0391

IPUG1185-1.0 2(12)

2 概述 2.1Gowin FP Div IP 介绍

2概述

### 2.1 Gowin FP Div IP 介绍

Gowin FP Div IP 可以得到两个单精度浮点格式数的商。该 IP 支持可选输出端口,例如上溢、下溢、零、NaN 和除零,旨在使用较少的逻辑资源完成浮点数除法的运算。

#### 表 2-1 Gowin FP Div IP

| Gowin FP Div IP |                                |

|-----------------|--------------------------------|

| 逻辑资源            | 请参见表 2-2                       |

| 交付文件            |                                |

| 设计文件            | Verilog                        |

| 参考设计            | Verilog                        |

| TestBench       | Verilog                        |

| 测试设计流程          |                                |

| 综合软件            | GowinSynthesis                 |

| 应用软件            | Gowin Software (V1.9.9 Beta-4) |

|                 |                                |

#### 注!

可登录高云半导体网站查看芯片支持信息。

## 2.2 主要特征

- 获取两个单精度浮点格式数的商

- 可选输出端口

## 2.3 最大频率

Gowin FP Div IP 的最大频率主要根据所选器件的速度等级(speed grade of the devices)确定。

IPUG1185-1.0 3(12)

2.4 延迟 Latency

## 2.4 延迟 Latency

Gowin FP Div IP 输出延迟主要由配置参数来确定。

### 2.5 资源利用

通过 Verilog 语言实现 Gowin FP Div IP。因使用器件的密度、速度和等级不同,其性能和资源利用情况可能不同。

以高云 GW2A-55 系列 FPGA 为例,Gowin FP Div IP 资源利用情况如表 2-2 Gowin FP Div IP 占用资源所示,有关在其他高云 FPGA 上的应用验证,请关注后期发布信息。

表 2-2 Gowin FP Div IP 占用资源

| 器件系列    | 速度等级  | 资源名称      | 资源利用 |

|---------|-------|-----------|------|

| GW2A-55 | C8/I7 | Registers | 3588 |

|         |       | LUTs      | 605  |

|         |       | ALUs      | 1394 |

|         |       | I/O Buf   | 104  |

IPUG1185-1.0 4(12)

# 3功能描述

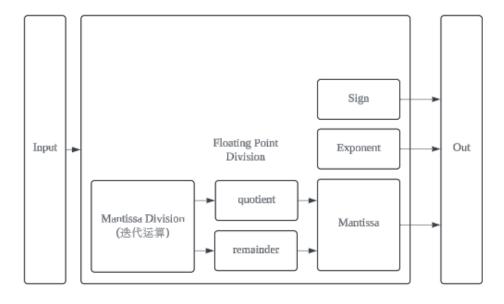

Gowin FP Div IP 可实现计算两个单精度浮点数的商,用户生成该模块时可根据需求自行配置参数。其结构示意图如图 3-1 所示。

#### 图 3-1 Gowin FP Div IP 结构示意图

IPUG1185-1.0 5(12)

# **4** 端口描述

有关 Gowin FP Div IP 的 I/O 端口框图如所示,详情如表 4-1 所示。

#### 图 4-1 Gowin FP Div IP 的接口实现

表 4-1 Gowin FP Div IP I/O 端口列表

| 信号     | 方向    | 描述                |

|--------|-------|-------------------|

| clk    | Input | 时钟信号              |

| rstn   | Input | 复位信号(低电平有效)       |

| се     | Input | 时钟使能信号(高电平有效)(可选) |

| data_a | Input | 输入a               |

| data_b | Input | 输入b               |

IPUG1185-1.0 6(12)

| 信号               | 方向     | 描述   |

|------------------|--------|------|

| overflow         | Output | 上溢   |

| underflow        | Output | 下溢   |

| nan              | Output | 非数   |

| zero             | Output | 零    |

| division_by_zero | Output | 除零   |

| result           | Output | 输出结果 |

IPUG1185-1.0 7(12)

# 5时序说明

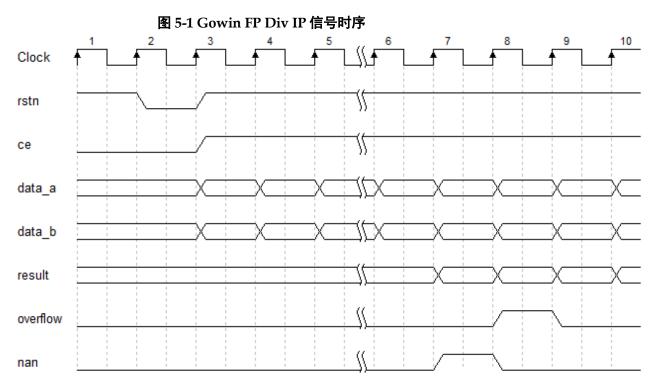

Gowin FP Div IP 信号时序图如图 5-1 所示。

如图所示,输入两个单精度浮点数数据后 55 个时钟输出两个数值的商 以及其数值资料类型。

IPUG1185-1.0 8(12)

6 调用及配置 6.1IP 调用

# 6调用及配置

### 6.1 IP 调用

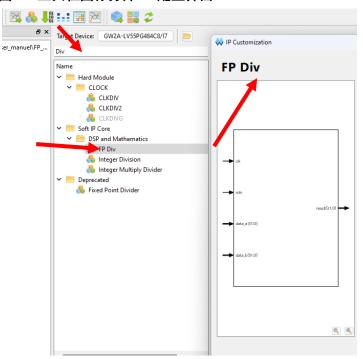

在高云云源软件界面菜单栏 Tools 下,可启动 IP Core Generator 工具,在 DSP and Mathematics 分类下, 可以找到 FP Div 完成调用与配置; 也可使用工具栏图标,如图 6-1 所示

#### 图 6-1 工具栏图标打开 IP 配置界面

IPUG1185-1.0 9(12)

6 调用及配置 6.2IP 配置

### 6.2 IP 配置

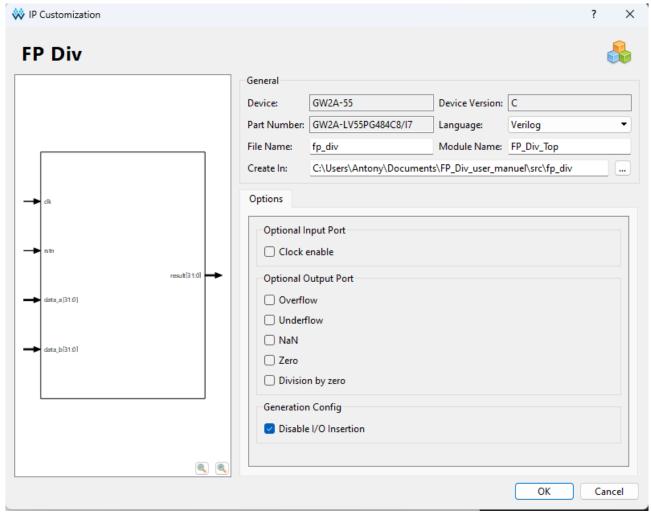

Gowin FP Div IP 配置界面如图 6-2 所示。

图 6-2 Gowin FP Div IP 配置界面

本手册以型号GW2A-LV55PG484C8/I7 为例。

- Create In 选项是 IP 核文件夹产生路径,用户可自行修改。

- File Name 选项是配置产生的 IP 文件名称, 用户可自行修改。

- Module Name 选项是配置产生的 IP 模块名称,用户可自行修改。

IPUG1185-1.0 10(12)

# 7参考设计

Gowin FP Div IP 参考设计请参考 RefDesign 内相关测试案例。

IPUG1185-1.0 11(12)

8 文档交付 8.1 文档

# **8** 文档交付

Gowin FP Div IP 交付文件主要包含文档和参考设计。

### 8.1 文档

文件夹主要包含用户指南 PDF 文档。

#### 表 8-1 Gowin FP Div IP 文档列表

| 名称                             | 描述               |

|--------------------------------|------------------|

| IPUG1185, Gowin FP Div IP 用户指南 | 高云 IP 用户手册,即本手册。 |

#### 8.2 参考设计

Gowin FP Div IP RefDesign 文件夹主要包含 Gowin FP Div IP 的网表文件,用户参考设计,约束文件、顶层文件及工程文件夹等。

#### 表 8-2 Gowin FP Div IP RefDesign 文件夹内容列表

| 名称         | 描述                  |

|------------|---------------------|

| top.v      | 参考设计的顶层 module      |

| FP_Div.cst | 工程物理约束文件            |

| FP_Div.sdc | 工程时序约束文件            |

| FP_Div.rao | 在线逻辑分析仪文件           |

| fp_div.v   | 生成 FP Div IP 顶层加密文件 |

IPUG1185-1.0 12(12)